Dynamic local reconfigurable system for real-time fault tolerance of hardware

A hardware and local technology, applied in the field of electronics, can solve the problems of system paralysis, high maintenance cost, and high cost in the replacement of hardware equipment, and achieve the effect of improving the life cycle, prolonging the life cycle, and being easy to update and upgrade.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

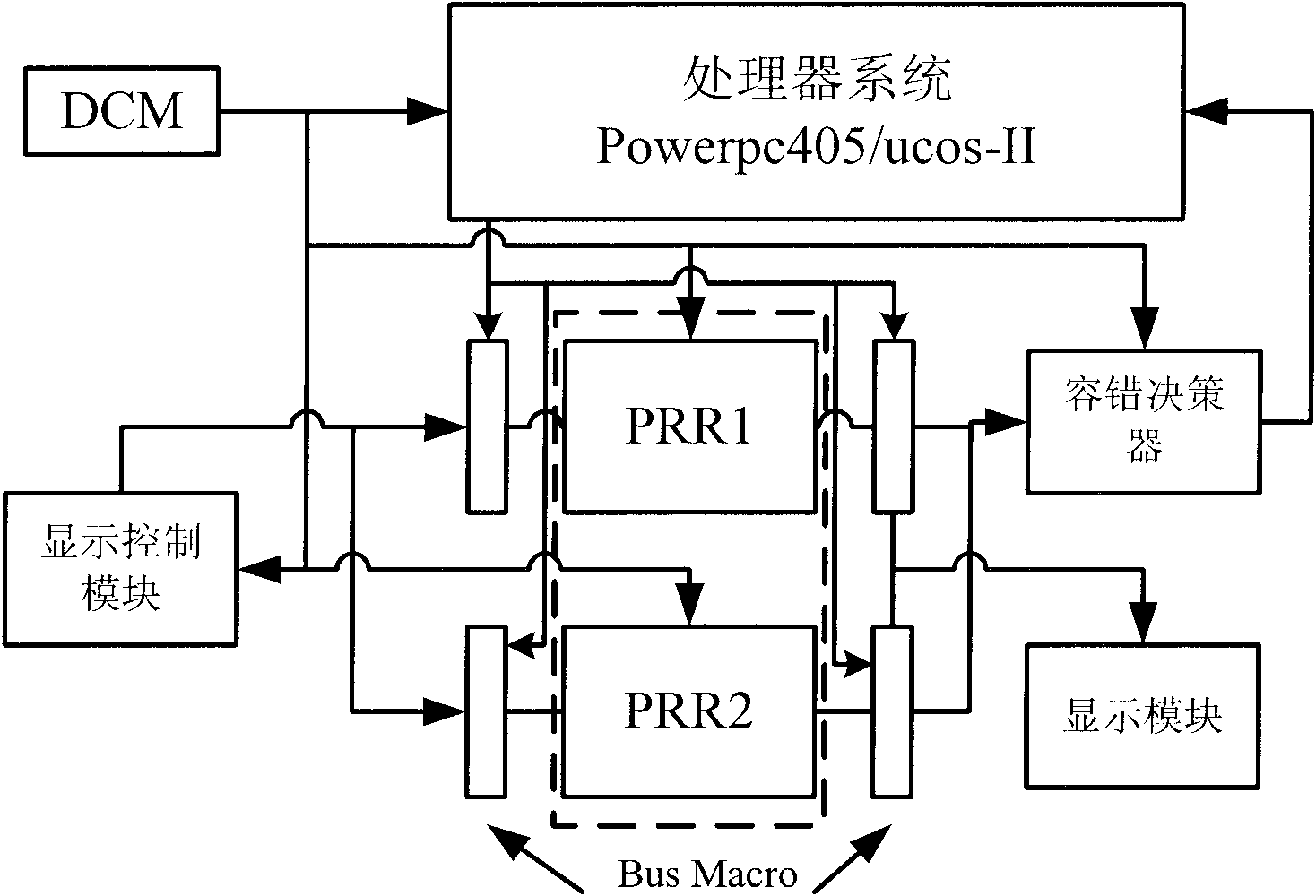

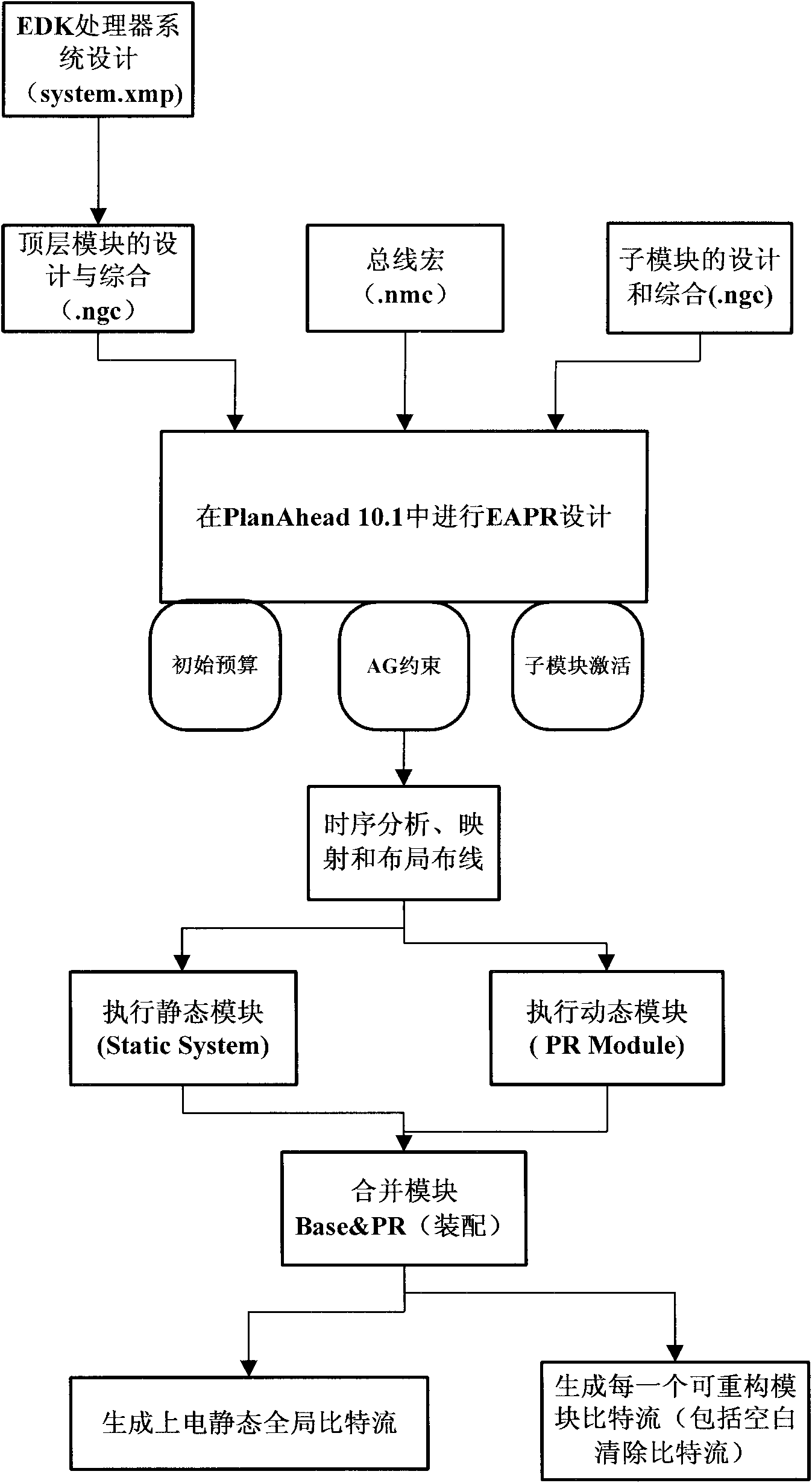

[0025] The present invention will be further described below in conjunction with accompanying drawing.

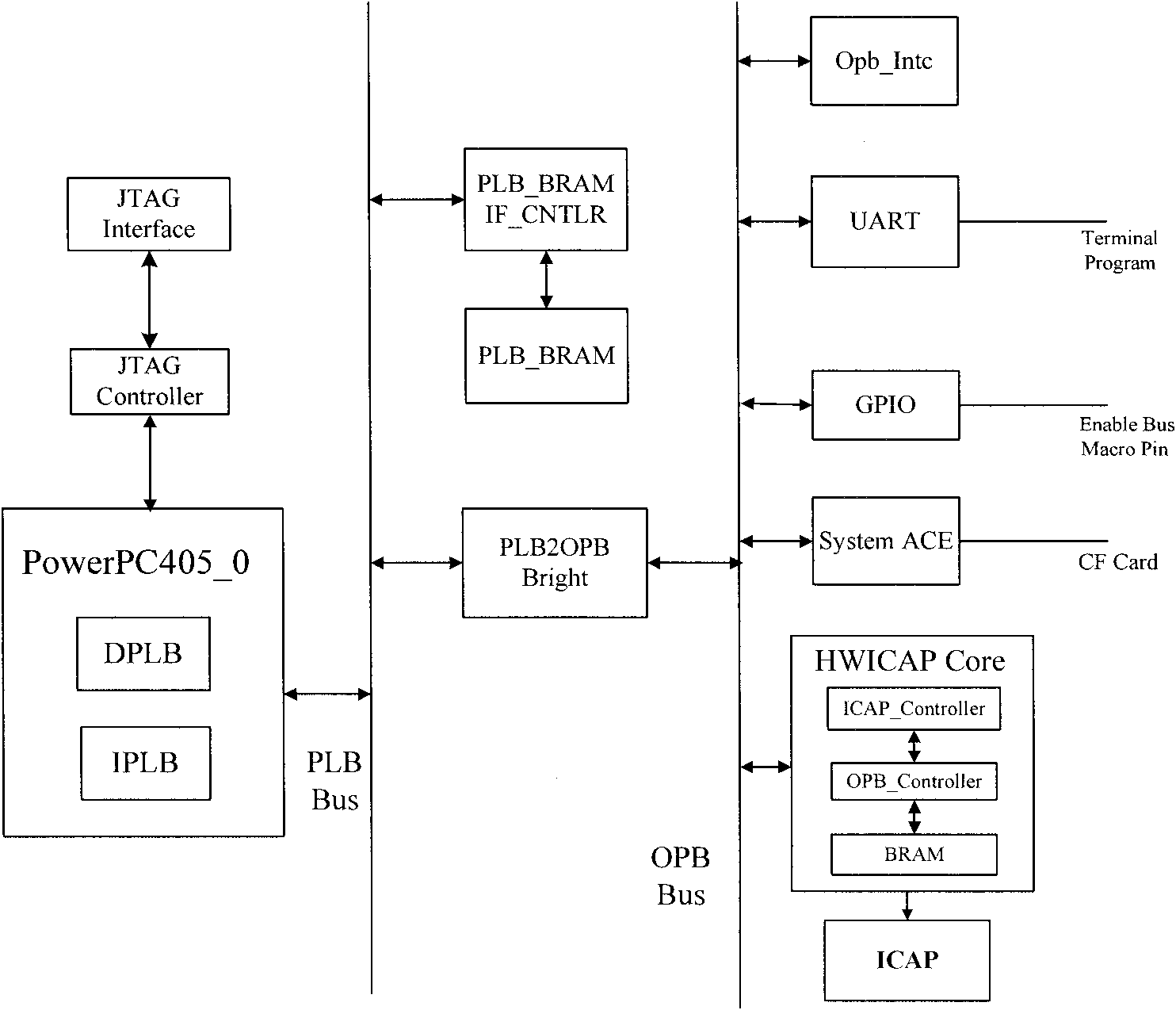

[0026] This embodiment is developed and designed on the XC2VP30 FPGA of Xilinx's Virtex-II Pro platform. The Virtex-II Pro platform supports partial dynamic reconfiguration and its FPGA is embedded with two IBM Powerpc405RSIC processors with a 5-stage standard pipeline structure. The PowerPC processor supports the CoreConnect bus standard technology developed by IBM. The use of CoreConct bus standard technology makes it possible to connect multiple IP Cores, making the design and application of SOPC-based dynamic partially reconfigurable systems easier, and the peripheral IP cores of the system can be reused, which also accelerates system design and The cycle of application product launch greatly saves human resources and development costs. The CoreConnect bus specification includes three bus architectures and two conversion bridges, namely: PLB bus (Processor Local Bus, p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More