Phase change memory chip layout structure

A phase change memory and layout structure technology, applied in the field of microelectronics, can solve the problems of signal distortion, read and write data errors, etc., and achieve the effect of reducing interference and reasonable chip layout.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

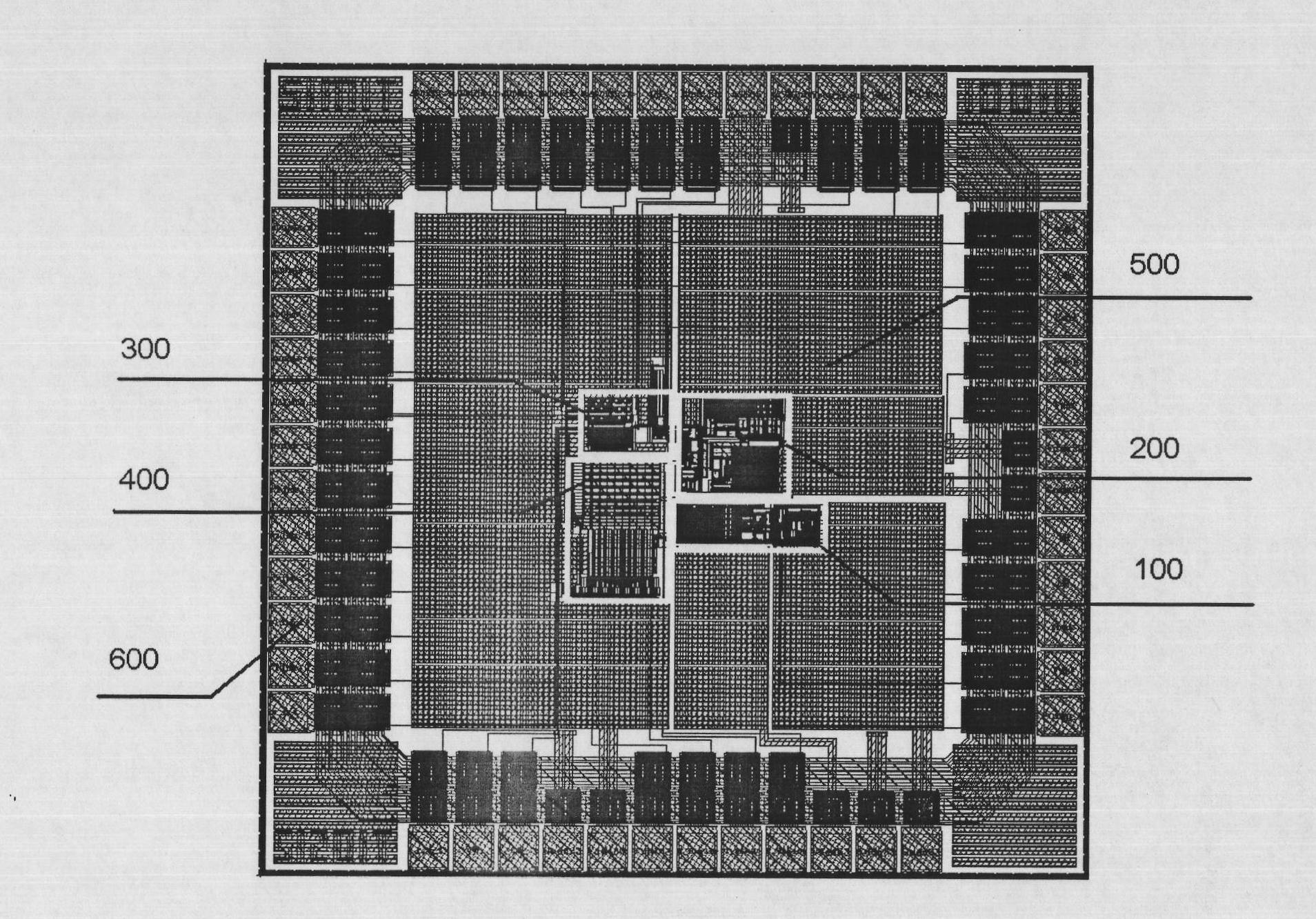

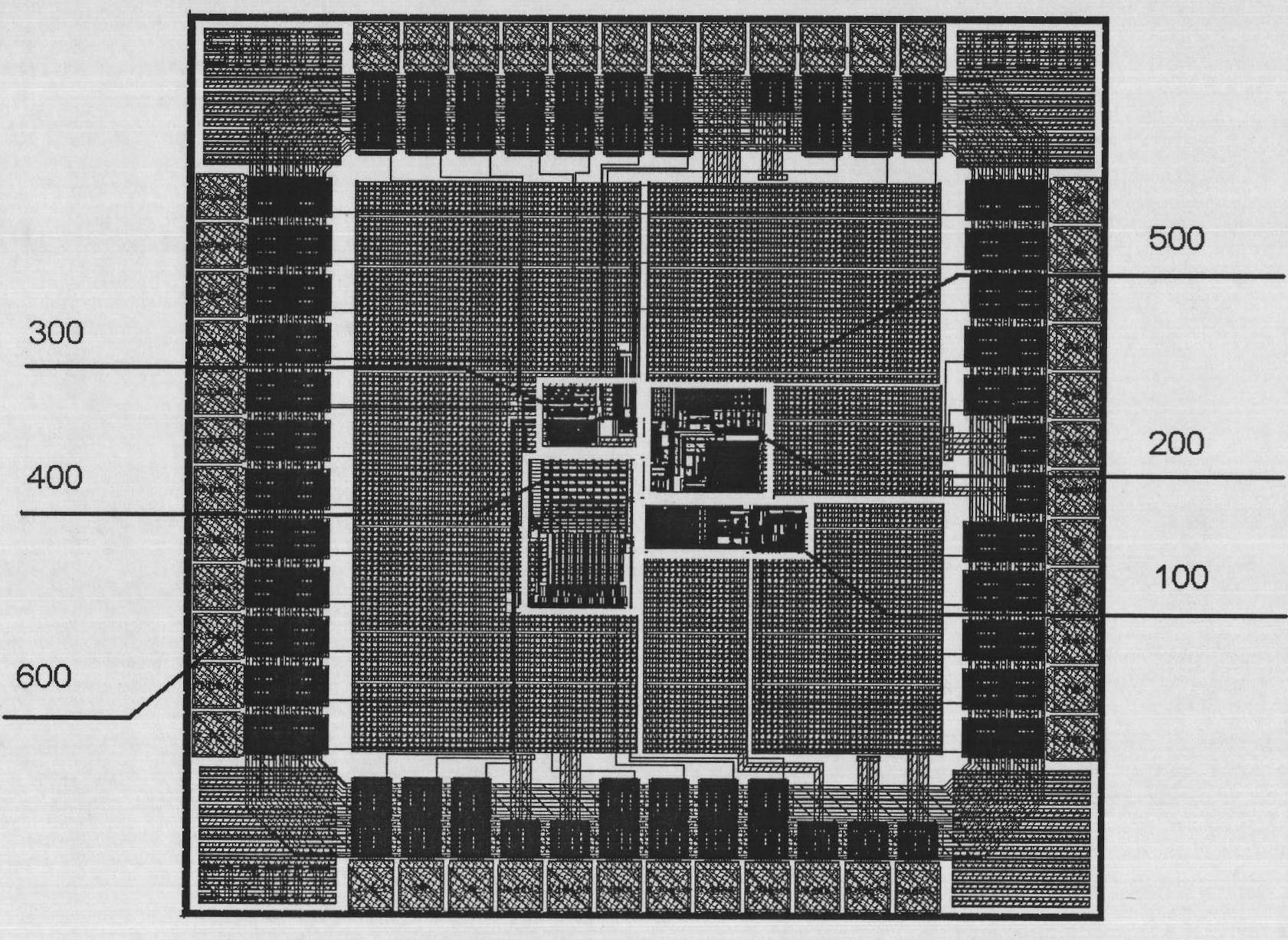

[0022] The invention discloses a phase-change memory chip layout structure, which makes the layout of the chip layout more reasonable.

[0023] see figure 2 , this embodiment takes a phase-change memory with a capacity of 512 bits manufactured by a 180nm CMOS process as an example to illustrate the layout structure of a phase-change memory chip provided by the present invention. The phase change memory chip layout is composed of a first layout area 100, a second layout area 200, a third layout area 300, a fourth layout area 400, a fifth layout area 500 and a sixth layout area 600; the first layout area 100, The second layout area 200, the third layout area 300 and the fourth layout area 400 are located in the center of the phase change memory chip layout; the first layout area 100 is connected to the second layout area 200, and the second layout area 200 is connected to the third layout area 300 The second layout area 200 is connected to the fourth layout area 400, the third...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More