Method for optimizing topological structure and mapping of network on chip

An on-chip network and topology technology, applied in data exchange networks, special data processing applications, instruments, etc., can solve the problems of chip area waste and high power consumption, and achieve optimized network structure and mapping, low power consumption, and small area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements.

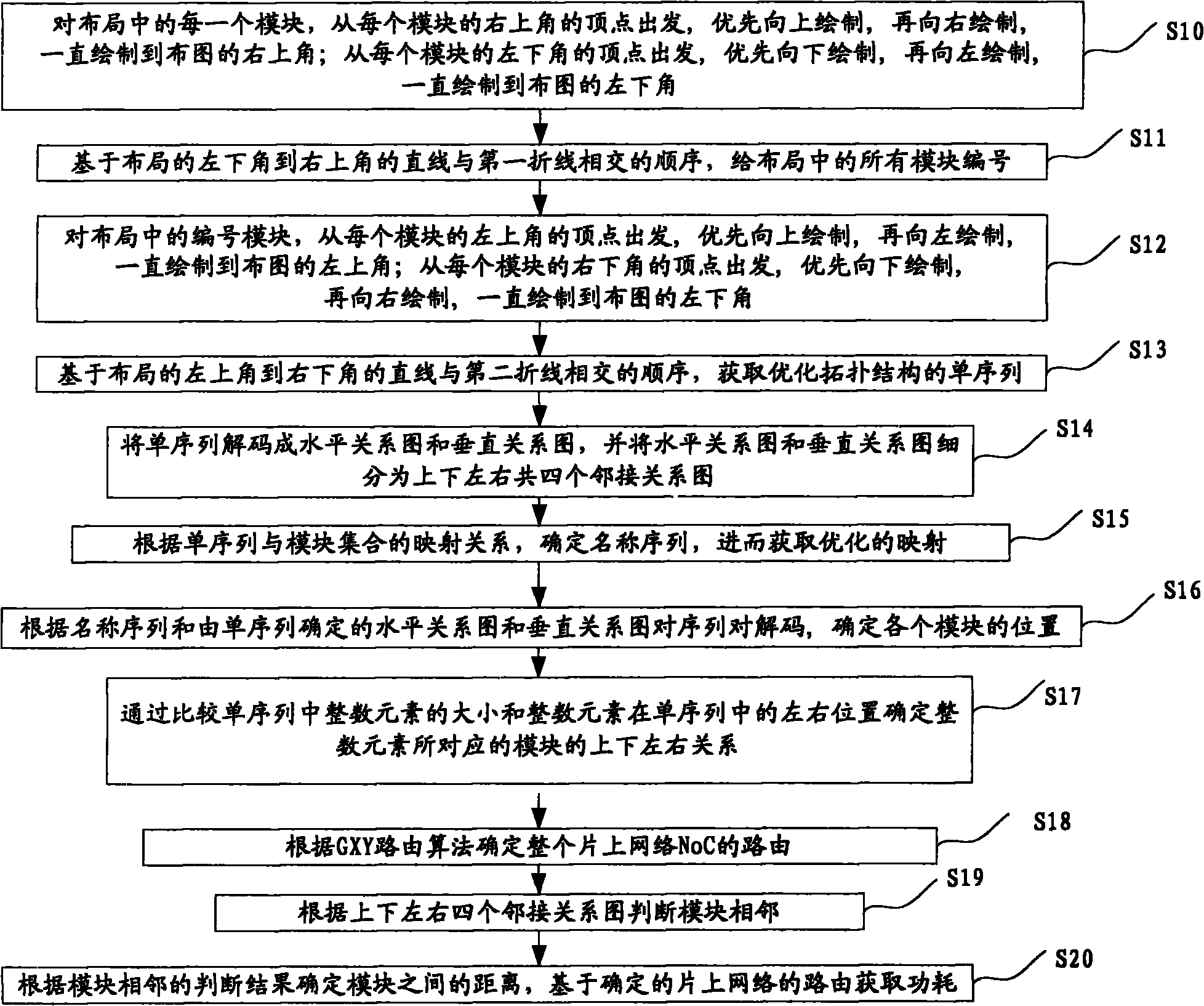

[0041] See figure 1 , the topology structure and mapping optimization method of the on-chip network in this embodiment includes the following steps:

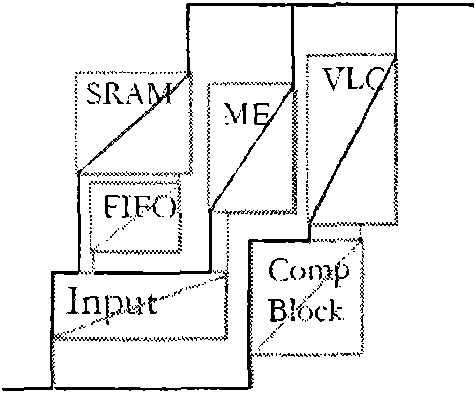

[0042]Step S10, for each module in the layout, start from the vertex in the upper right corner of each module, draw upward first, then draw to the right, and draw to the upper right corner of the layout; start from the vertex in the lower left corner of each module , draw downwards first, then draw to the left, and draw to the lower left corner of the layout;

[0043] Step S11, numbering all modules in the layout based on the order in which the straight line from the lower left corner to the upper right corner of the layout intersects with the first fold line;

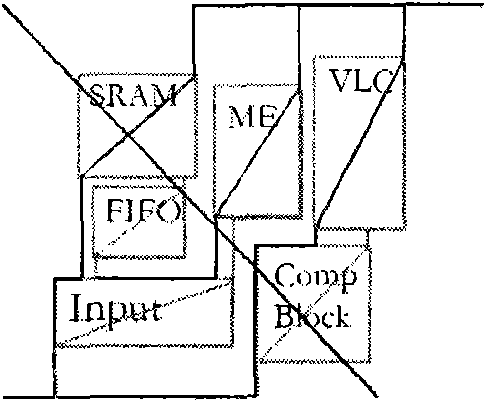

[0044] Step S12, for the numbered modules in the layout, start from the vertex in the upper left corner of each...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More