Circuit and method for realizing FFT/IFFT conversion

A circuit and complex number addition technology, applied in the direction of electrical digital data processing, reliability improvement and modification, complex mathematical operations, etc., can solve the problem of different data storage order, achieve the effect of reducing operation bit width, saving RAM consumption, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

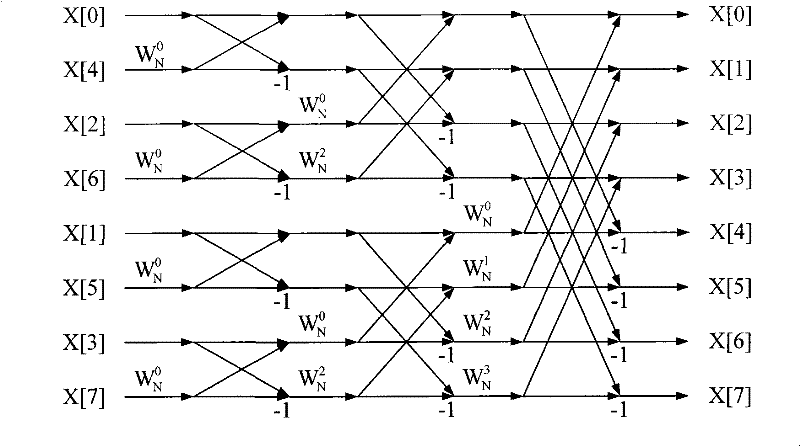

Image

Examples

Embodiment Construction

[0041] Below in conjunction with accompanying drawing and embodiment the present invention is described in further detail:

[0042] see image 3 , shown in this figure is the circuit realizing FFT / IFFT conversion of the present invention, comprising: multiplexer (A), multiplexer (B), RAM memory 1 (C), RAM memory 0 (D), ROM Memory (E), multiplexer (F), multiplexer (G), complex multiplier (H), complex adder (J), complex adder (K); the output of this circuit is multiplexed The data output of the device (F) and the multiplexer (G), or the data output of the RAM memory 1 (C) and the RAM memory 0 (D); this circuit has two data inputs, respectively connected to the multiplexer (A) and multiplexer (B);

[0043] Wherein, one data input end of FFT / IFFT and the output end of complex number adder (J) are connected with two input ends of multiplexer (A) respectively; Another data input end of FFT / IFFT is connected with complex number adder ( The output end of K) links to each other with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More