Interlock of read column select and read databus precharge control signals

A technology for reading data and data bus, which is applied in timing control of column selection and precharge signal. field, which can solve problems such as slow device execution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

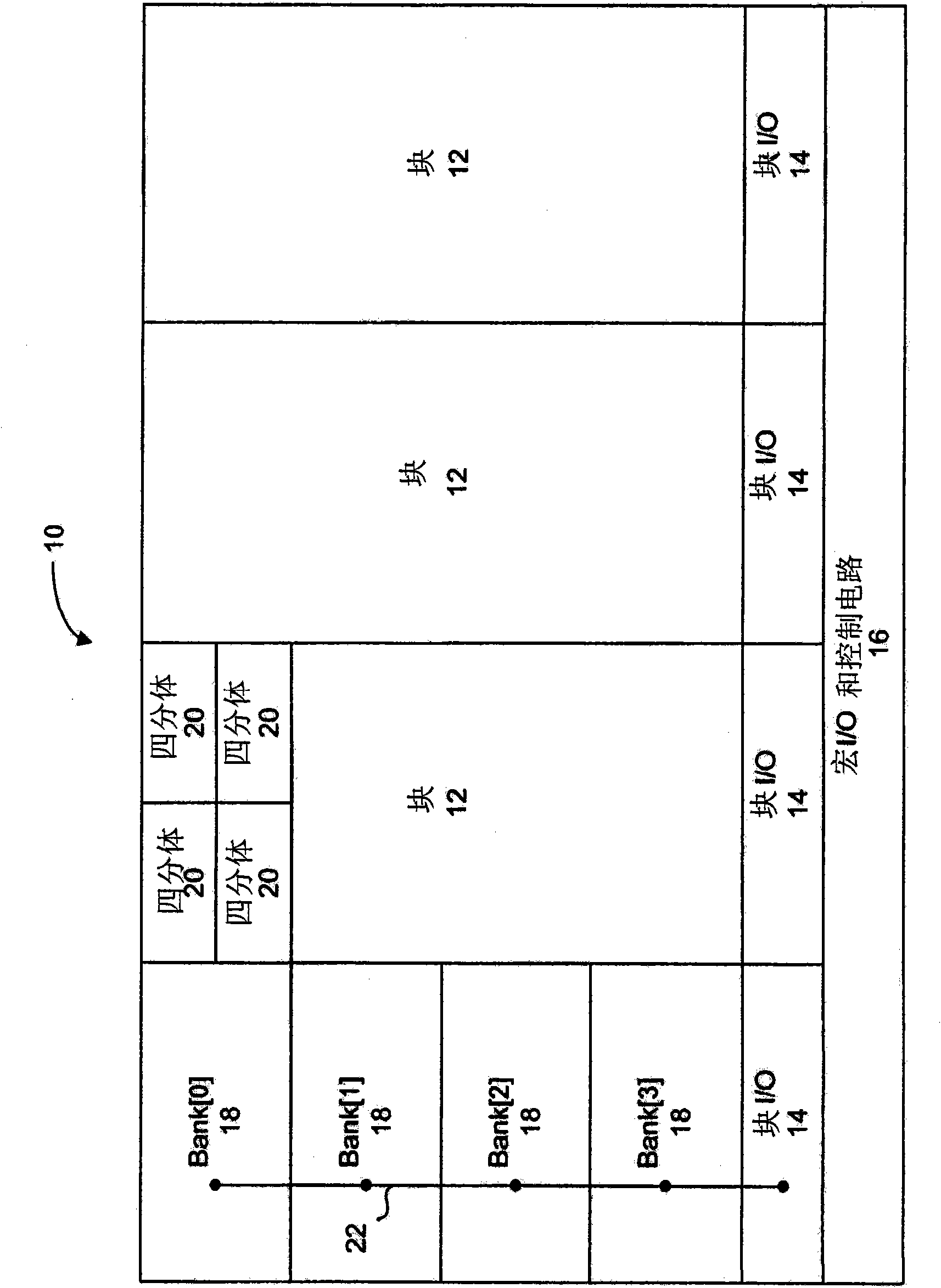

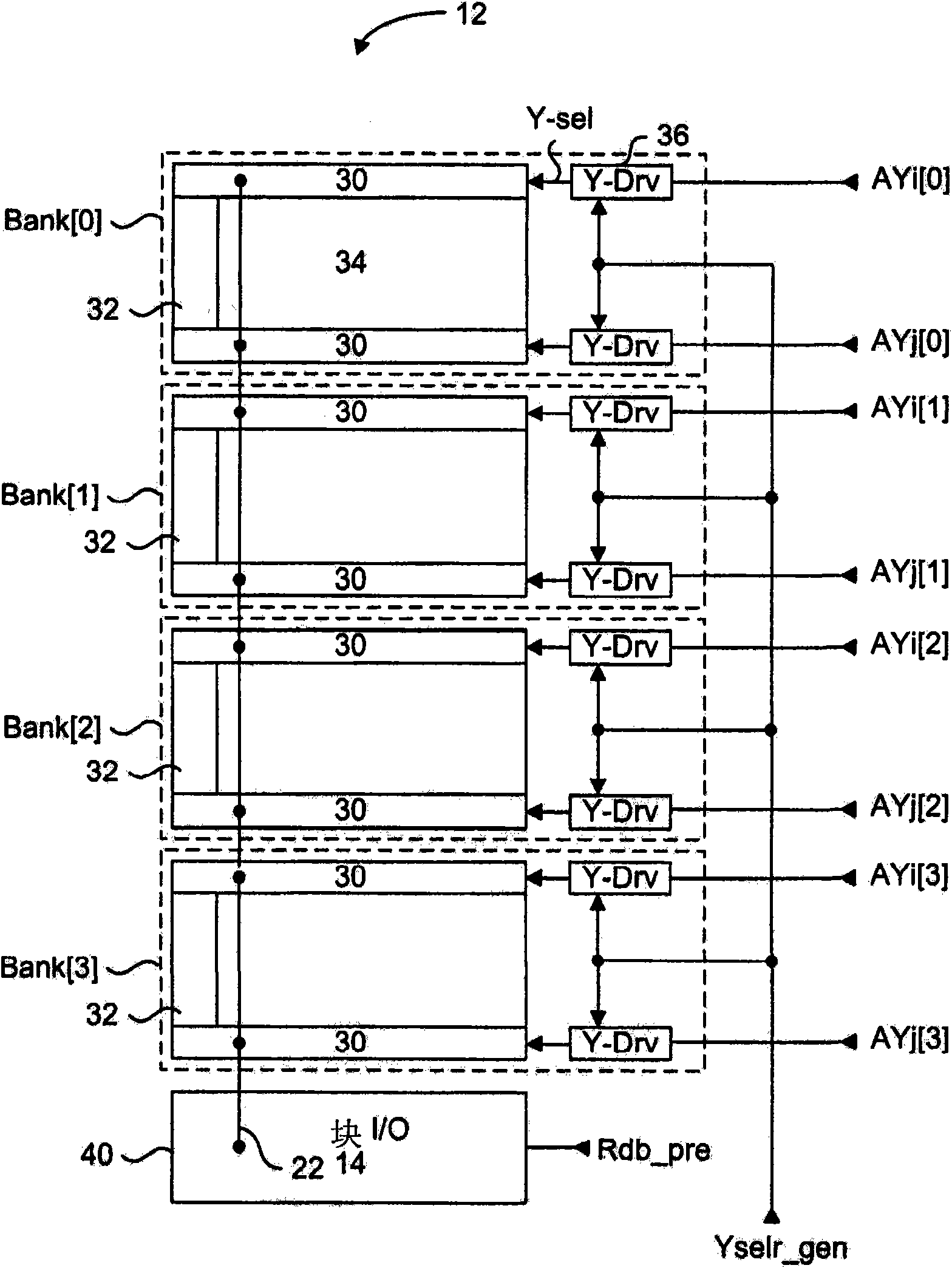

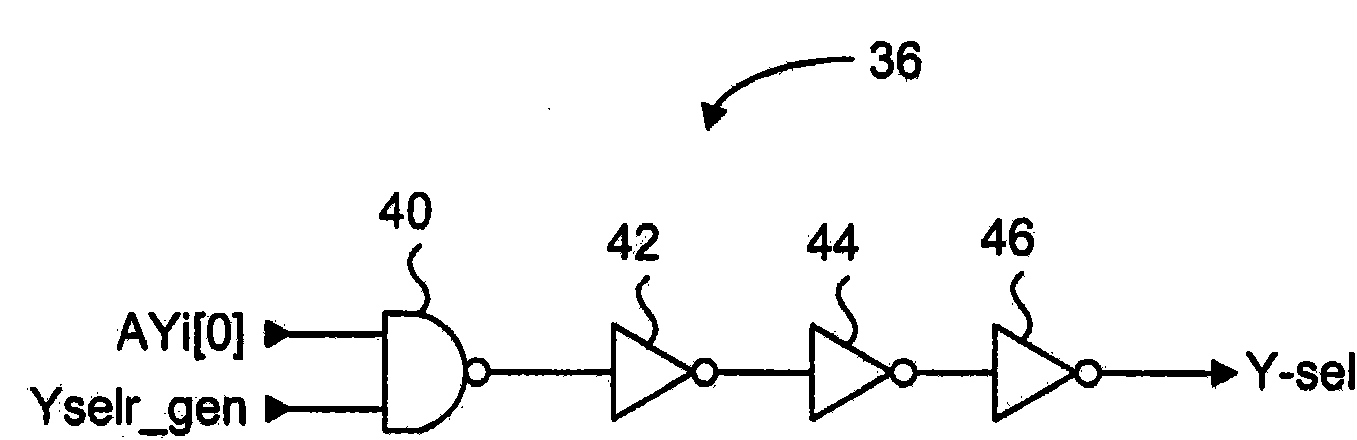

[0040] The invention discloses a column selection and precharge signal interlock scheme for DRAM memory. The signal interlock system includes a column sense enable circuit associated with each bank of the DRAM memory for generating a column select signal for coupling data to a common sense data bus and for generating a column select signal for disabling the sense data Read data bus precharge disable signal for bus precharge device. Each column read enable circuit includes a pulse generator circuit having an adjustable element for generating at least one column select signal pulse and a read data bus precharge disable pulse during a read operation. The circuitry in the pulse generator circuit ensures that the column select pulse is always embedded with the read data bus precharge disable pulse. Thus, there is no overlap between active column select means and active read data bus precharge means.

[0041] In fact, the column select signal pulses and precharge disable signal puls...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More