Semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices, can solve the problems of increased SGT standby leakage current and increased power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0201] Embodiment 1 Semiconductor device

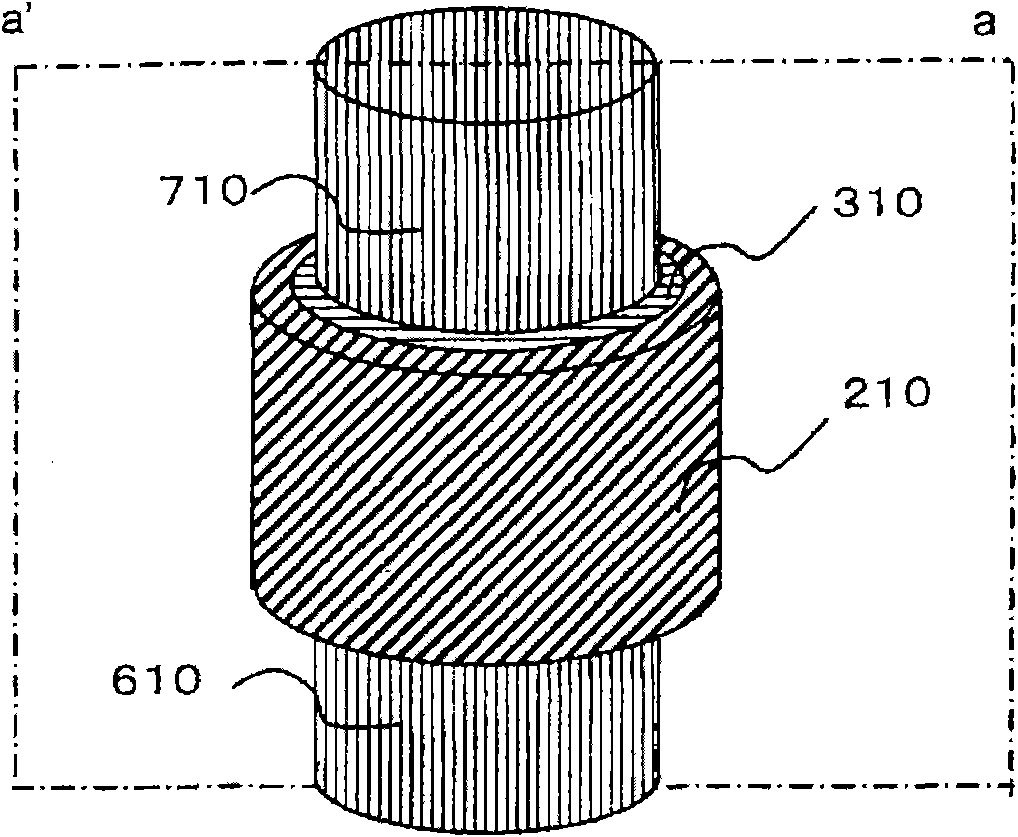

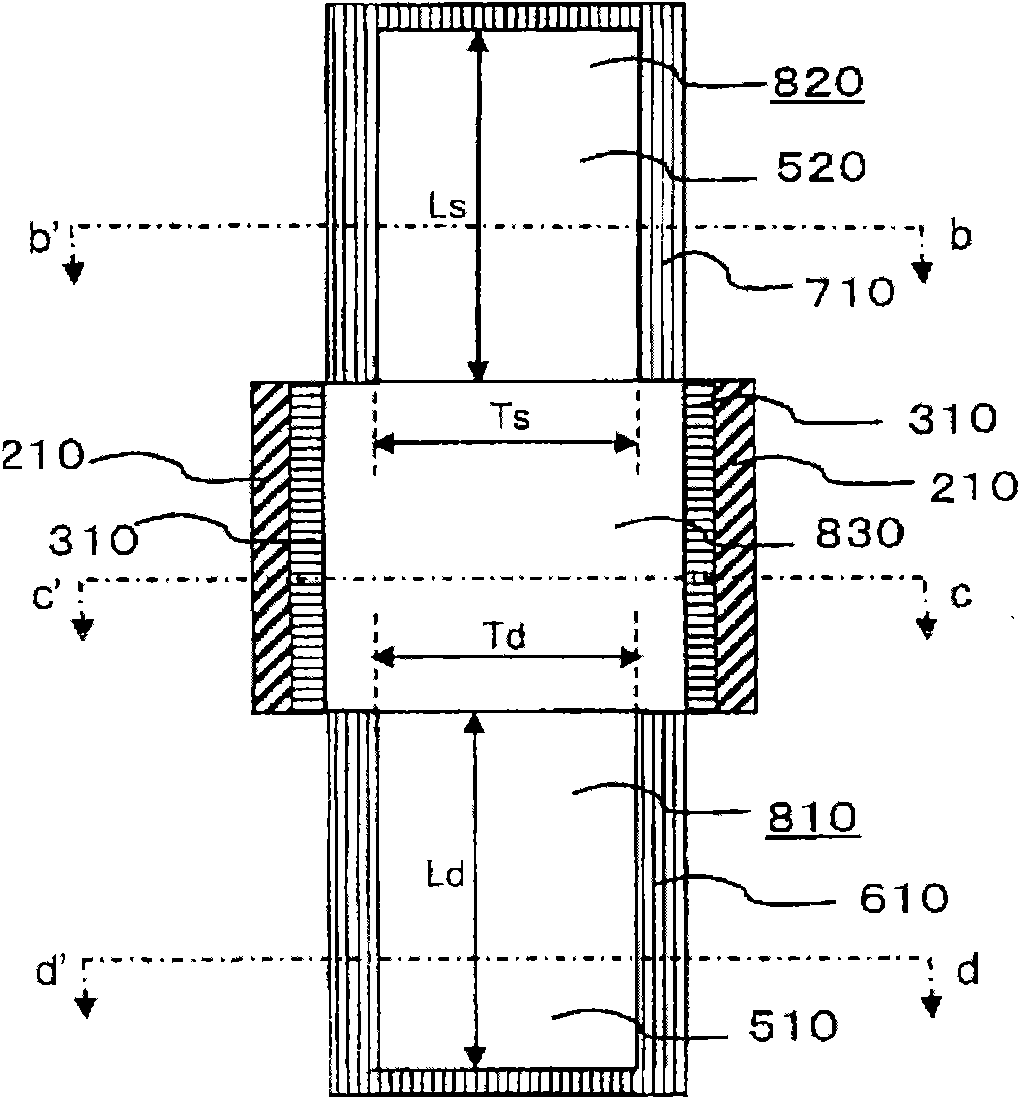

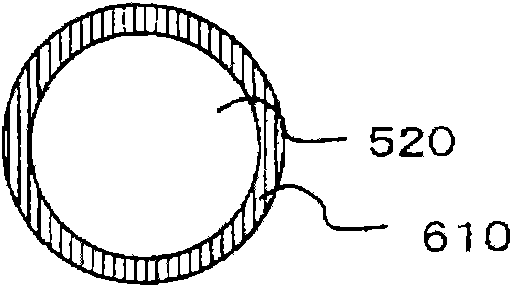

[0202] figure 1 It is a schematic bird's-eye view showing the semiconductor device of Embodiment 1 of the present invention. figure 2 for along figure 1 A schematic cross-sectional view of the cutting line (cut line) a-a'. image 3 for along figure 2 A schematic cross-sectional view of the cutting line b-b'. Figure 4 for along figure 2 A schematic cross-sectional view of the cutting line c-c'. Figure 5 for along figure 2 A schematic cross-sectional view of the cutting line d-d'.

[0203] The semiconductor device of this embodiment includes: a third silicon pillar 830 of the first conductivity type; a first insulator 310 surrounding the side surface of the third silicon pillar 830; a gate 210 surrounding the first insulator 310; a first silicon pillar 810 set On the lower part of the third silicon pillar 830; the second silicon pillar 820 is arranged on the upper part of the third silicon pillar 830; the second conducti...

Embodiment 2

[0227] Embodiment 2 Semiconductor device

[0228] Figure 8 In order to show that the first conductivity type impurity region 510 formed on the first silicon pillar 810 in the first embodiment is the same second conductivity type as the second conductivity type high-concentration impurity region 610 formed on the first silicon pillar 810 A schematic bird's-eye view of a transistor in the semiconductor device of the present invention in a high-concentration impurity region. Figure 9 for Figure 8 A rough cross-sectional view of the cutting line (cut line) a-a', Figure 10 for Figure 9 A rough cross-sectional view of the cutting line b-b', Figure 11 for Figure 9 A rough profile of the cutting line c-c', Figure 12 for Figure 9 A schematic cross-sectional view of the cutting line d-d'.

[0229] In this embodiment, in order to increase the breakdown voltage, it is more preferable that the first conductive type impurity region 520 included in the second silicon pillar ...

Embodiment 3

[0241] Embodiment 3 Semiconductor device

[0242] Figure 15 In order to show that the first conductivity type impurity region 520 formed on the second silicon pillar 820 in Embodiment 1 is the same second conductivity type as the second conductivity type high-concentration impurity region 710 formed on the second silicon pillar 820 A schematic bird's-eye view of a transistor in the semiconductor device of the present invention in a high-concentration impurity region. Figure 16 for Figure 15 A rough cross-sectional view of the cutting line a-a′, Figure 17 for Figure 16 A rough cross-sectional view of the cutting line b-b', Figure 18 for Figure 16 A rough profile of the cutting line c-c′, Figure 19 for Figure 16 A schematic cross-sectional view of the cutting line d-d'.

[0243] In this embodiment, in order to increase the breakdown voltage, it is more preferable that the first conductive type impurity region 510 included in the first silicon pillar 810 has a la...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Film thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More