Method o encapsulating a wafer level microdevice

A micro-device, wafer-level technology, applied in the directions of microstructure devices, manufacturing microstructure devices, assembling microstructure devices, etc., can solve the problems of increasing the thickness of wafer stacking, wafer handling problems, etc., to avoid chemical pollution, thin wafers, and transfer. Easy-to-use effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

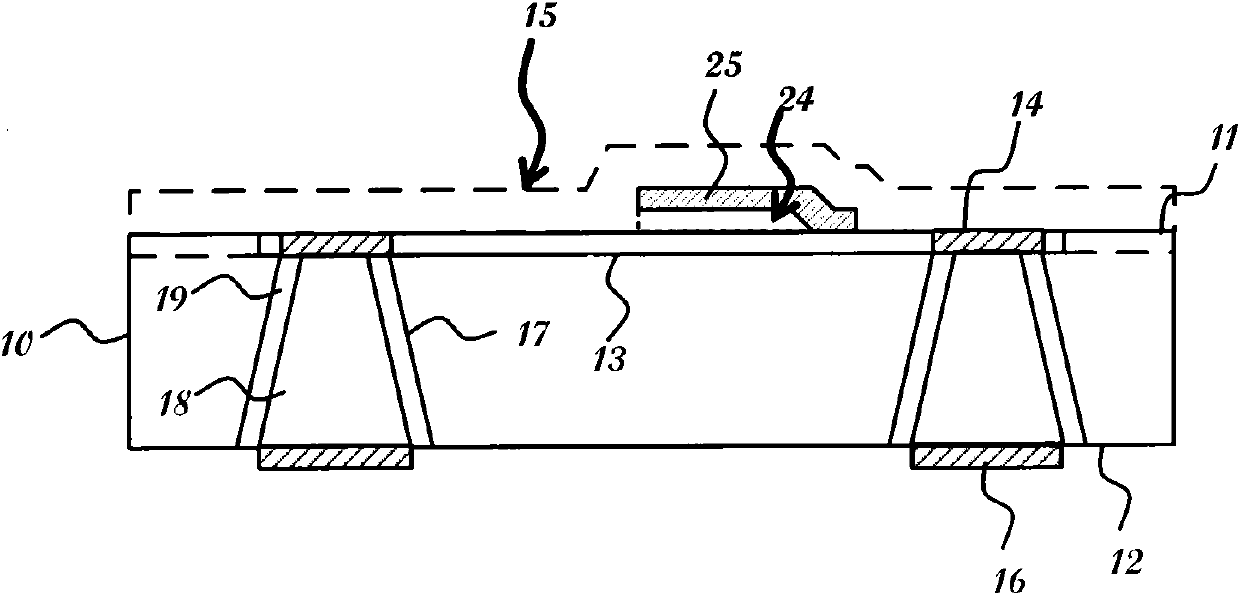

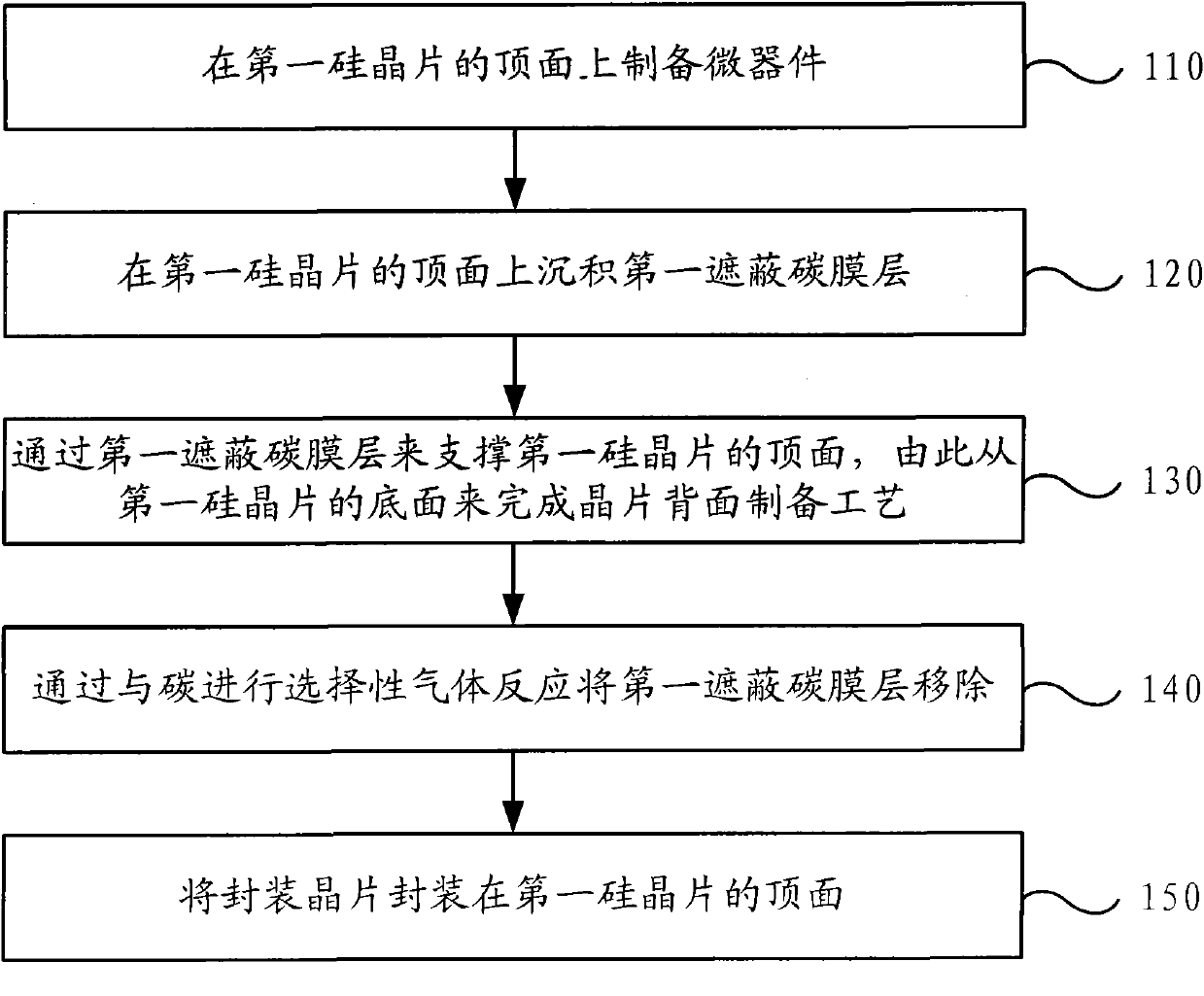

[0029] figure 1 The flow chart of the packaging method of wafer-level micro-device provided for Embodiment 1 of the present invention shows the basic packaging process of the micro-device of the present invention, wherein the details that are known and obvious to the field of wafer-level electronic preparation are ignored and simplified describe. This embodiment specifically includes the following steps:

[0030] Step 110, preparing micro-devices 13 on the top surface 11 of the first silicon wafer 10;

[0031] The first silicon wafer 10 is used as a silicon substrate, and any process method in the prior art and / or industrial practice can be used to prepare micro-devices 13, usually a plurality of micro-devices 13 are prepared, and a plurality of micro-devices 13 are in the form of a planar array arrange, such as Figure 2a Shown is the partial structural representation of the micro-device prepared by the first embodiment of the present invention Figure 1 , which exemplari...

Embodiment 2

[0052] image 3 It is a flow chart of the packaging method for wafer-level micro-devices provided in Embodiment 2 of the present invention, forming Figure 2e There are many ways of the structure shown, and this embodiment provides a specific implementation way, and packaging the package chip 20 on the top surface 11 of the first silicon chip 10 includes:

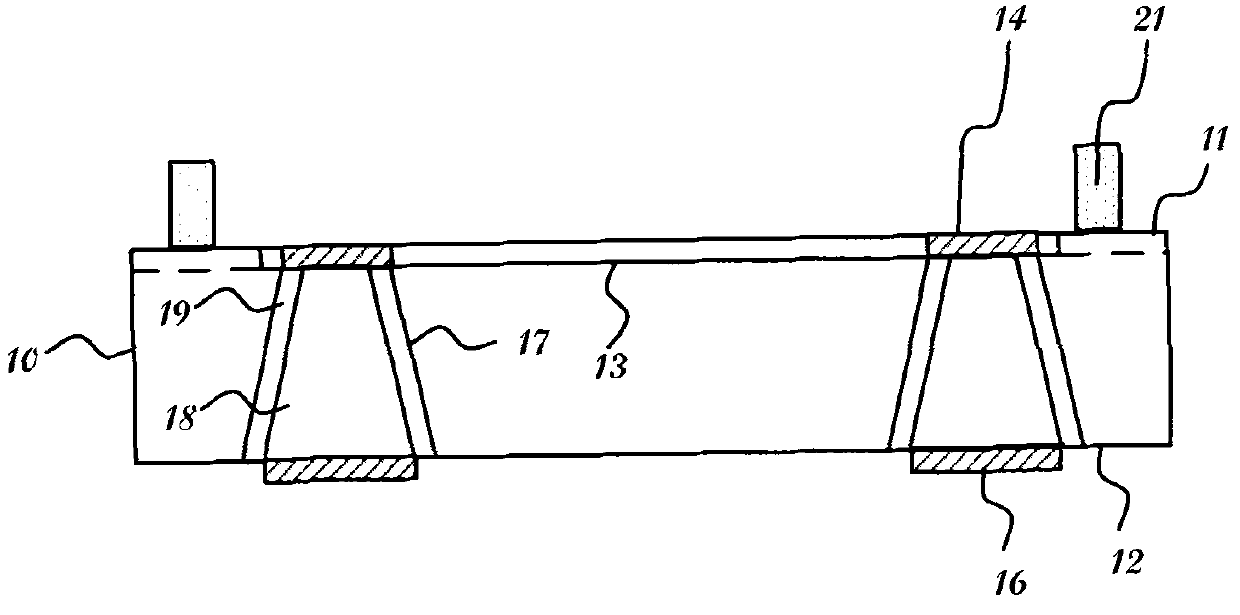

[0053] Step 310, prepare a sealing grid 21 on the top surface 11 of the first silicon wafer 10, and the sealing grid 21 surrounds the outside of the micro-device 13, such as Figure 4a As shown, provide sidewalls for the subsequently generated shielding cavity 30;

[0054] Step 320, attach and fix the packaging chip 20 on the sealing grid 21 on the top surface 11 of the first silicon wafer 10, and the packaging chip 20, the sealing grid 21 and the top surface 11 of the first silicon wafer 10 are completely closed and closed. The sealed shielding cavity 30, specifically, the shielding cavity 30 takes the bottom surface of ...

Embodiment 3

[0058] Figure 5 It is a flow chart of the packaging method for wafer-level micro-devices provided in Embodiment 3 of the present invention, forming Figure 2e There are many ways of the structure shown, and this embodiment provides another specific implementation way, and packaging the package chip 20 on the top surface 11 of the first silicon chip 10 includes:

[0059] Step 510, prepare the sealing grid 21 on the surface of the packaging chip 20, such as Image 6 shown;

[0060] Step 520, attach and fix the top surface 11 of the first silicon wafer 10 on the sealing grid 21 of the packaging chip 20, the packaging wafer 20, the sealing grid 21 and the top surface 11 of the first silicon wafer 10 are surrounded to shield the cavity 30. Encapsulate the micro-device 13 in the shielding cavity 30, see Figure 4b shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More