System and method for extracting parasitic components in analog integrated circuit layout

An integrated circuit and extraction system technology, applied in the fields of instruments, electrical digital data processing, special data processing applications, etc., can solve the problems of special parasitic device extraction, spending a lot of time and energy, etc., and achieve the effect of design optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings.

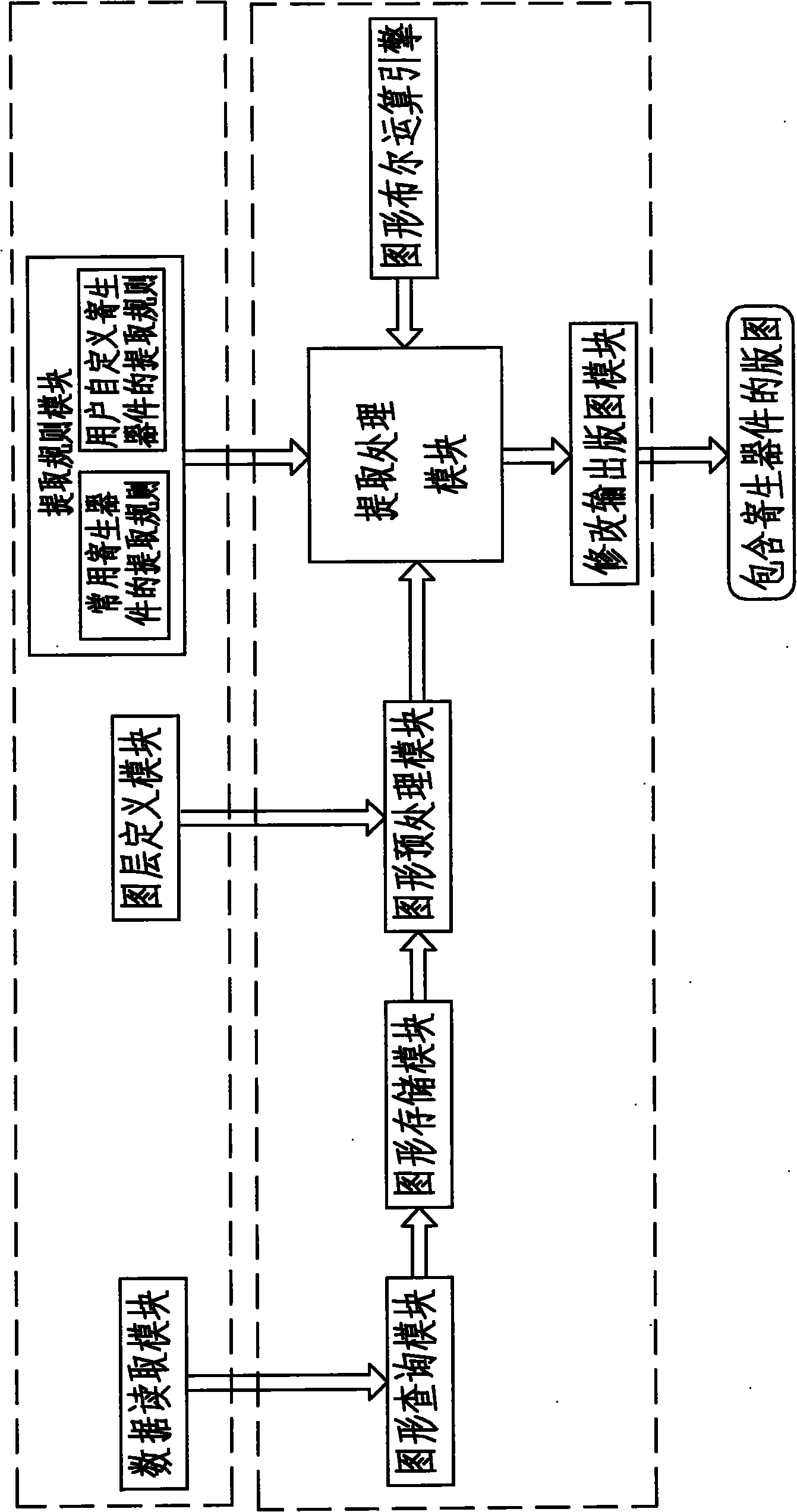

[0045] figure 1 As shown, the principle diagram of the system for extracting special parasitic devices of analog integrated circuit layout according to the present invention. As can be seen from the figure, the present invention consists of the following parts.

[0046] 1. The input includes data reading module, layer definition module and extraction rule module.

[0047] 1.1 Data reading module

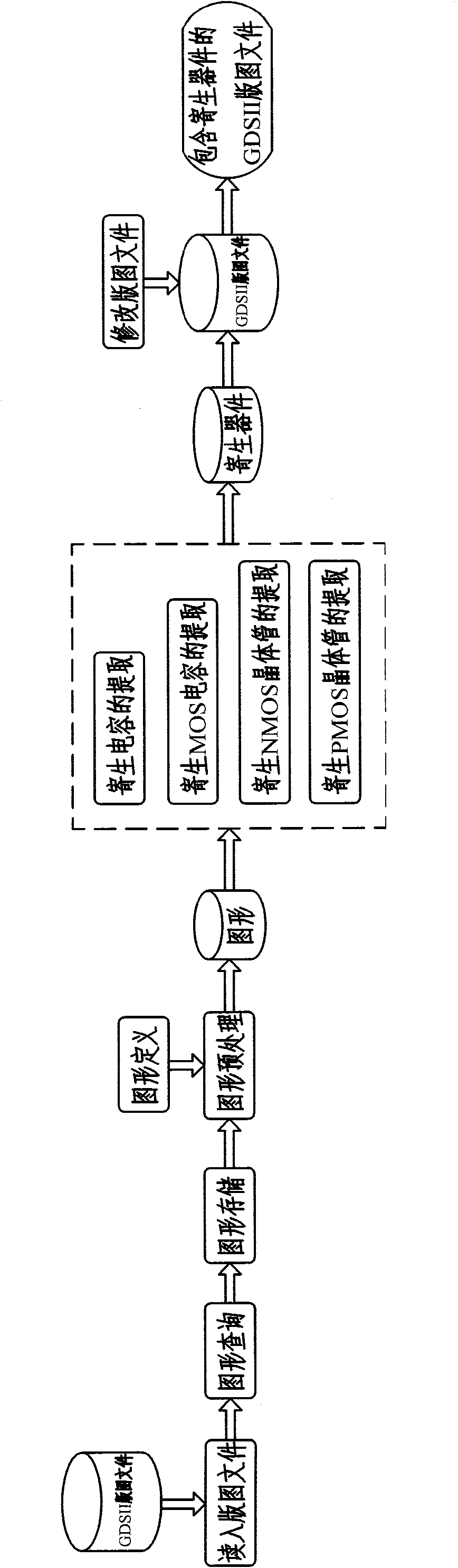

[0048] The standard layout description format is GDSII format. The data reading module of the present invention is based on the OpenAccess (OA) platform, and uses the built-in stream2oa command to convert the GDSII format into the data structure inside the OA. The file in GDSII format is a kind of data stream (stream) for OA. After being converted into the data structure of OA, various API functions provided by OA can be used to op...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More