Phase frequency detector (PFD), phase frequency detection method thereof, phase locking loop (PLL) and frequency synthesizer

A frequency discriminator, phase-locked loop technology, applied in the field of frequency discriminator, phase discriminator, frequency synthesizer, frequency discriminator and phase discriminator, phase-locked loop field, can solve the deterioration of phase noise and spurious and other problems to achieve the effect of improving in-band phase noise and spurious

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

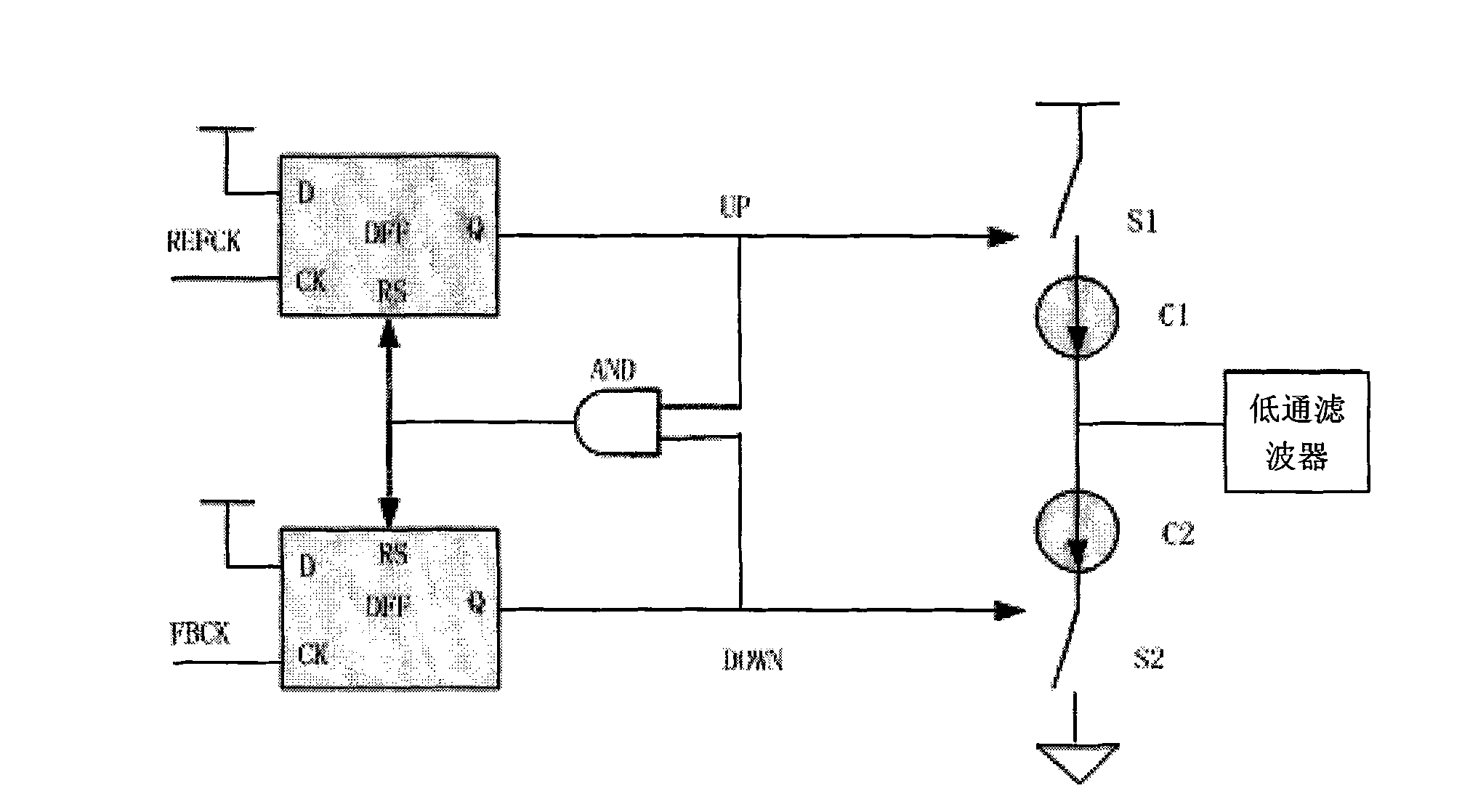

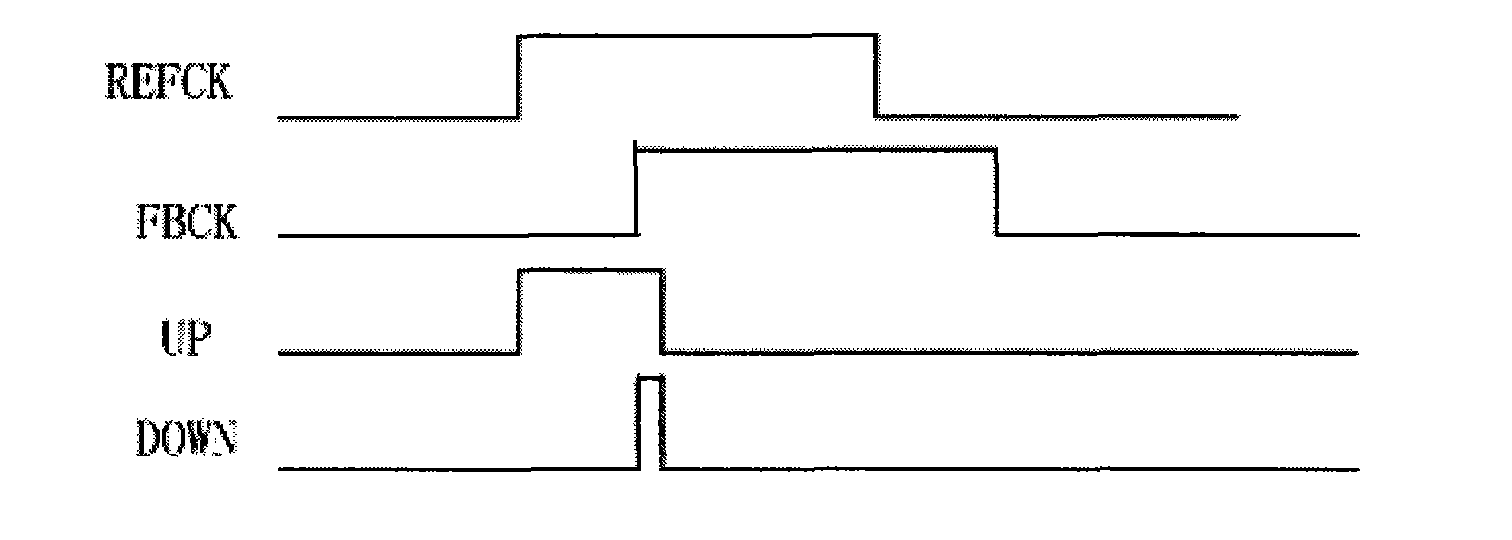

[0046] see Figure 7 , the present invention discloses a frequency and phase detector, and the frequency and phase detector is used for comparing the phases of a reference clock and a frequency divider feedback clock. When the phase of the feedback clock lagged behind the phase of the reference clock, the frequency detector phase detector output was used to increase the frequency of the pulse signal UP signal; when the phase of the feedback clock exceeded the phase of the reference clock, the frequency detector phase detector output used It is used to reduce the frequency of the pulse signal DOWN signal. The phase frequency detector includes two resettable DFFs; when both the UP signal and the DOWN signal are high, at least one of the two DFFs is delayed so that the two DFFs are reset; thus, when the PLL is at When locked, the frequency and phase detector works in the linear region.

[0047] Correspondingly, the frequency and phase detector further includes at least one dela...

Embodiment 2

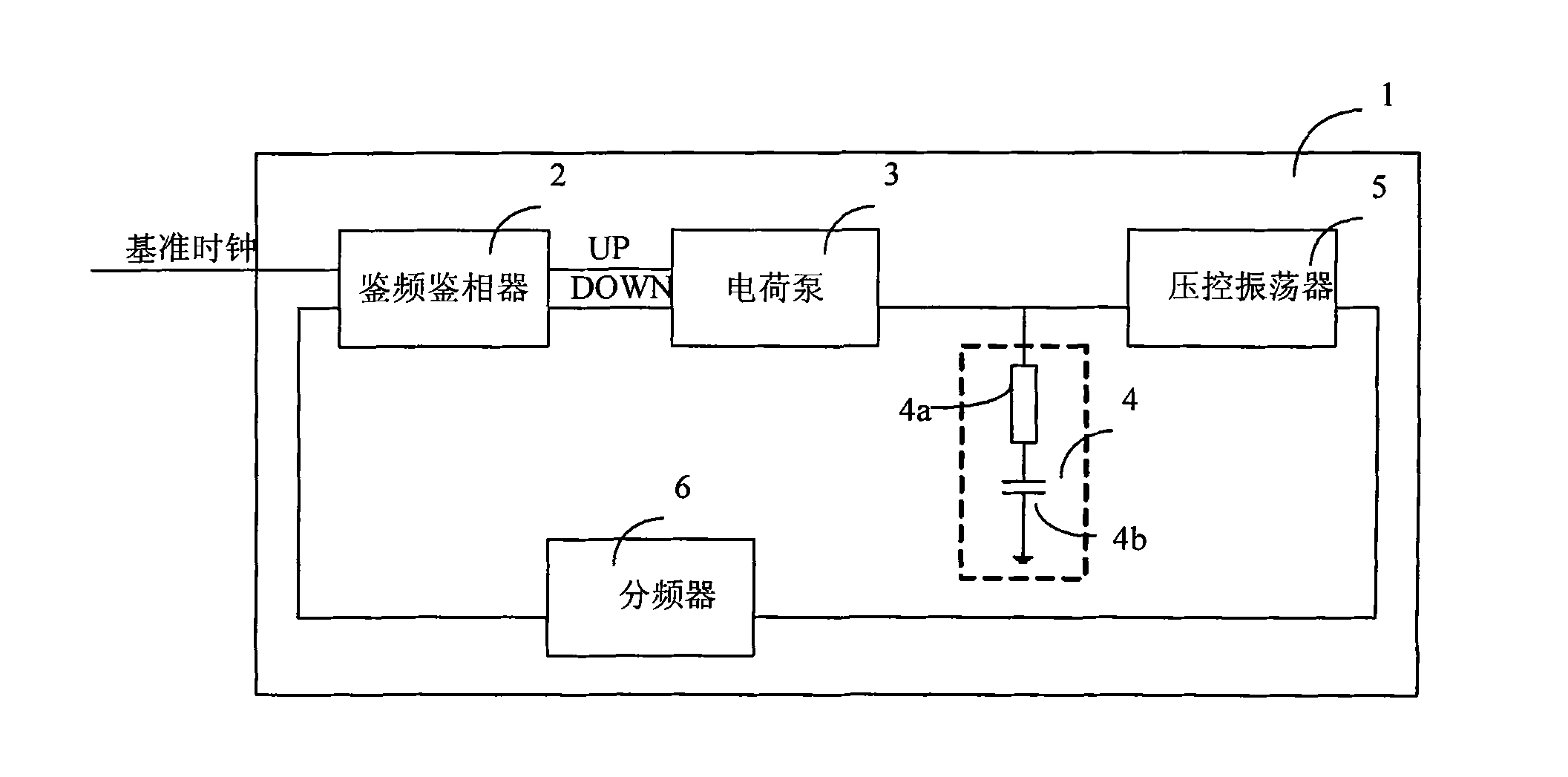

[0056] This embodiment discloses a phase-locked loop including the frequency and phase detector described in Embodiment 1. At the same time, this embodiment further improves the above-mentioned phase-locked loop. The improved phase-locked loop is as follows Figure 5 shown.

[0057] see Figure 5 , Figure 6 , the present invention discloses a phase-locked loop, the phase-locked loop includes a reference clock frequency divider 11, a frequency and phase detector 12, a charge pump 13, a low-pass filter 14, a voltage-controlled oscillator 15, and a divider connected in sequence. A frequency divider 16; the voltage-controlled oscillator 15 is connected with an AFC automatic frequency controller 17, and the frequency divider 16 is connected with a ΔΣ modulator 18.

[0058] read on Figure 5 , the crystal oscillator clock first passes through a reference clock divider to generate CKREF. The reference clock frequency divider 11 is a programmable frequency divider, and different ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More