Semiconductor device, semiconductor device manufacturing method, printed circuit board and electronic device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of large number of decoupling capacitors, large parasitic inductance, large installation area, etc., to achieve Effects of reducing parasitic inductance, reducing switching noise, and reducing voltage fluctuations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

[0208] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings.

Embodiment approach 1

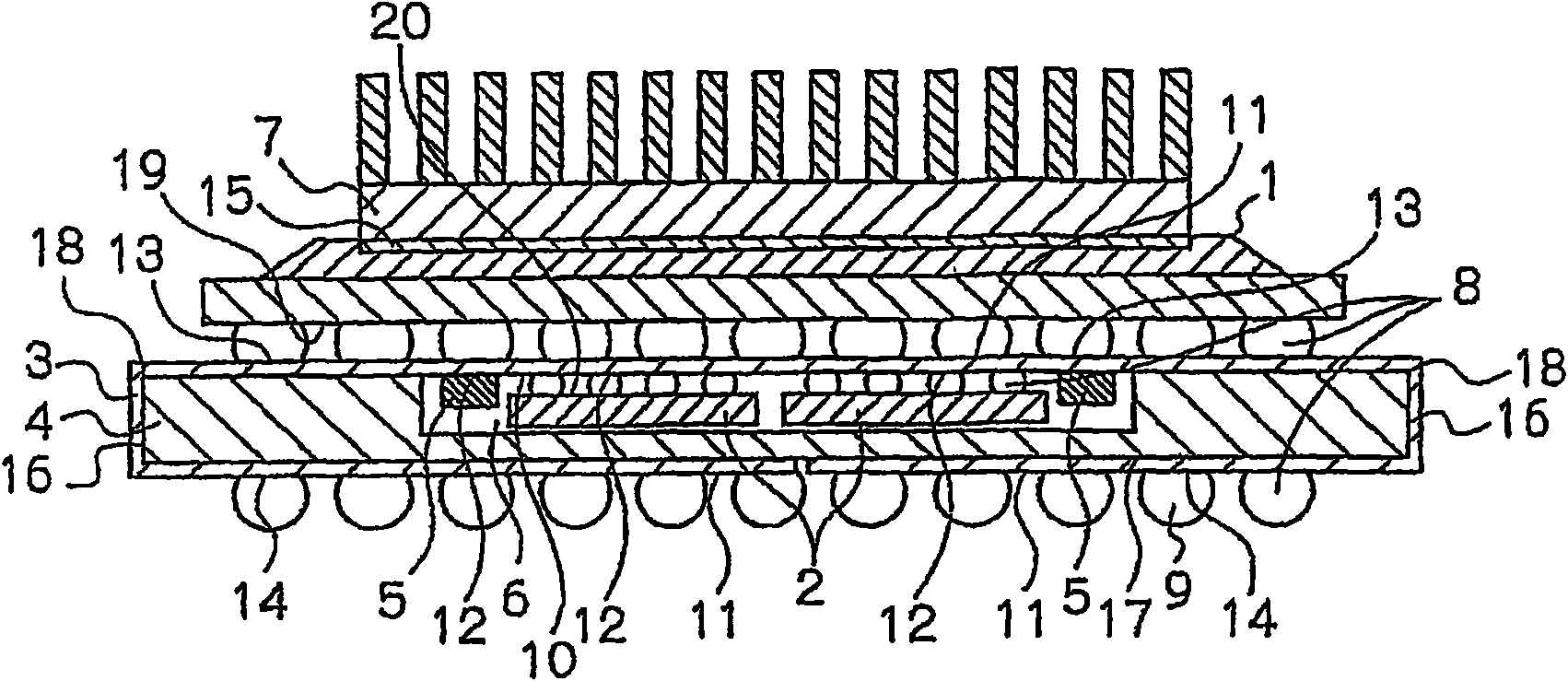

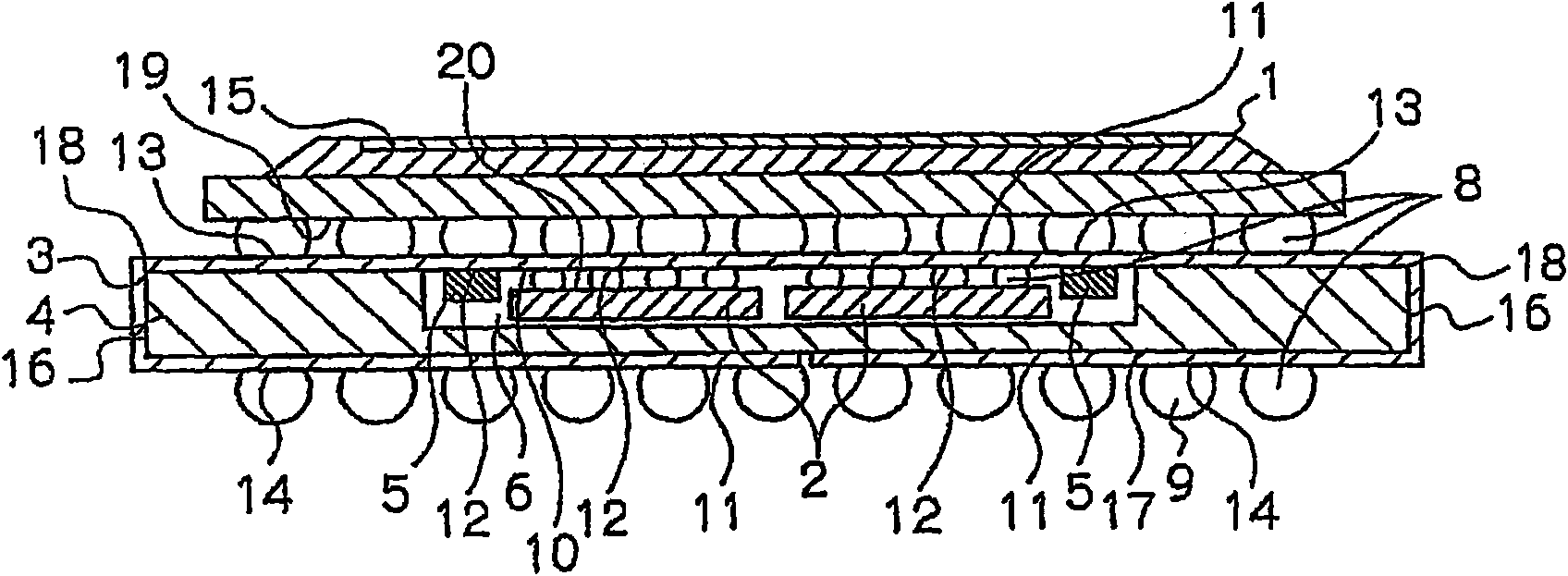

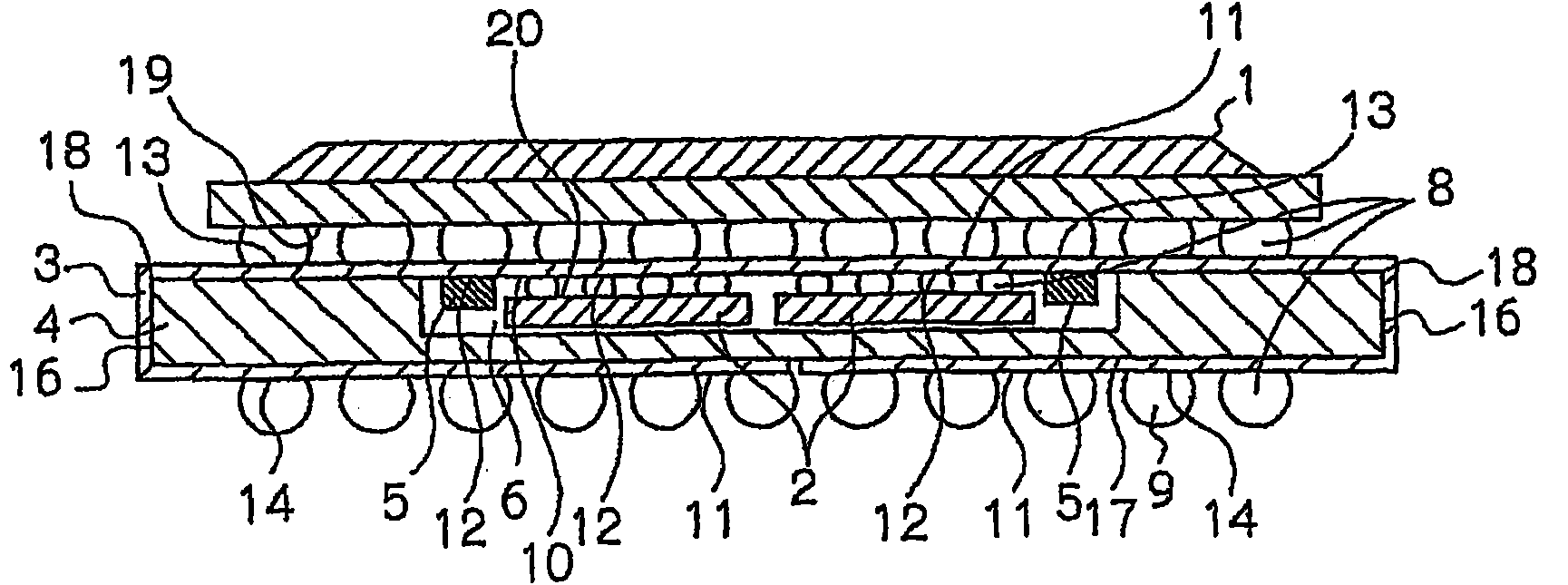

[0210] Figure 1A ~ Figure 1C It is a cross-sectional view showing the semiconductor device according to Embodiment 1 of the present invention. figure 2 It is a plan view (viewed from directly above) when a plurality of memory devices 2 and a plurality of passive components 5 are planarly mounted on the first surface of the flexible circuit board 3 used in the semiconductor device of the present invention. image 3 After a plurality of storage devices 2 and a plurality of passive components 5 are mounted on the flexible circuit board 3, the support body 4 provided with the groove 6 for accommodating these components is bonded to the flexible circuit board 3 in a manner to surround these components. A plan view (viewed from directly above) on the first surface 10 or after being connected to the first external electrode 12 formed on the first surface 10 . Figure 4 is shown along image 3 A diagram of the profile of the line A-A' in.

[0211] Figure 1A The shown semiconduc...

Embodiment approach 2

[0247] Figure 11 It is a cross-sectional view showing a semiconductor device according to Embodiment 2 of the present invention. Figure 11 Embodiment 2 of the present invention shown has a structure similar to Embodiment 1 of the present invention shown in FIG. package) structure) is different from Embodiment 1.

[0248] exist Figure 11 2 shows a structure in which BGA-type packages are stacked in two stages, however, it is not limited to BGA-type packages, and may be a structure in which TSOP-type packages having wiring on external terminals are stacked. also, Figure 11 2 shows a method in which two sets of packages are stacked in two stages, but three or more sets may be used as long as the area limit permits. In addition, as long as the height limit allows, the package can also be stacked more than 3 levels, and it can also include non-stacked packages. Furthermore, even a single package may include a multi-chip package including a plurality of memory dies inside. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Linear expansion rate | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More