Method and digital chip for generating multi-path SPWM signals

A digital chip and signal technology, applied in electrical components, pulse technology, pulse modulation, etc., can solve the problems of increased volume of frequency converter, complex software and hardware structure, and large CPU time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0060] The present invention will be further described below with reference to the accompanying drawings and embodiments. The following description is only used to understand the technical solutions of the present invention and is not used to limit the scope of the present invention.

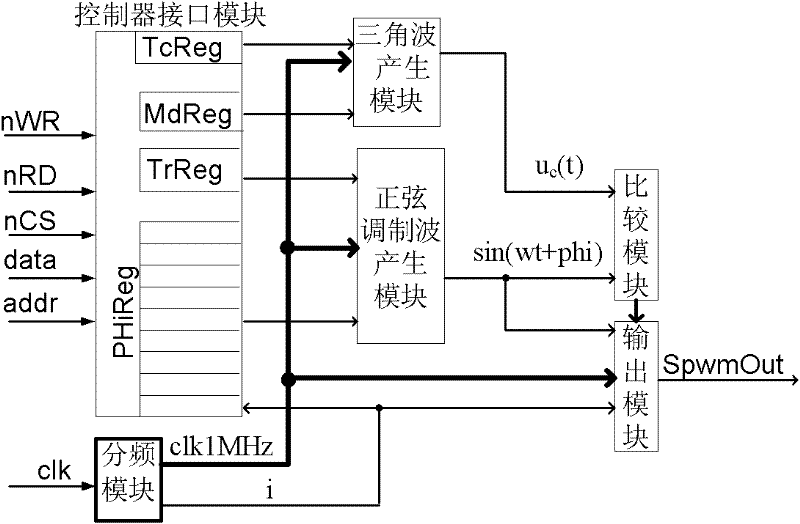

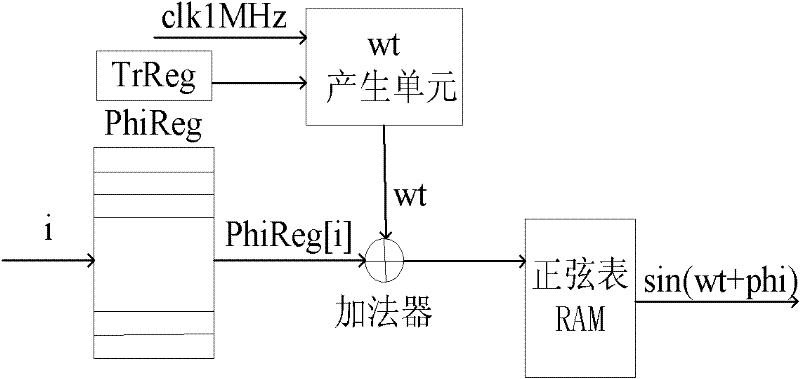

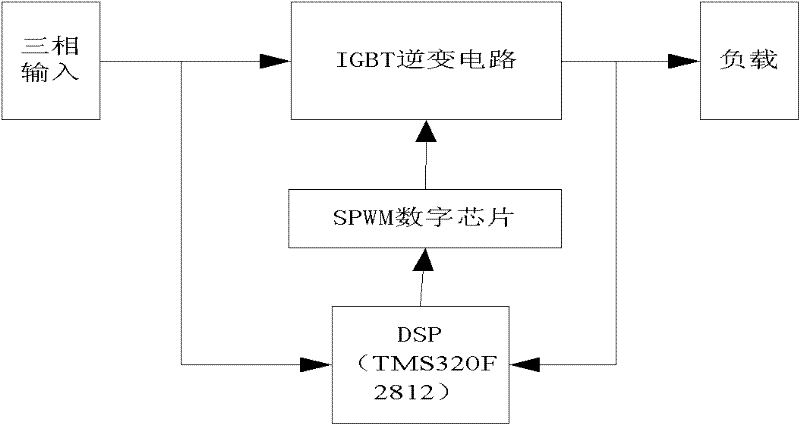

[0061] figure 1 To utilize the method for generating multiple SPWM signals and an embodiment of the digital chip disclosed in the present invention. The embodiment describes the functional block diagram of the 48-channel SPWM generator chip, which uses a 50MHz external clock signal, is designed as the trigger time error is less than 1us, and the sampling period is 1us. The 48-channel SPWM signal generator chip FPGA implementation is mainly composed of a controller interface module, a triangle wave generation module, a sine modulation wave generation module, a frequency division module, a comparison module, and an output module. The instructions are as follows:

[0062] Controller interface module: P...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More