Memory-cell array, nonvolatile storage device, memory-cell, and manufacturing method of memory-cell array

A memory cell array and memory cell technology, which is applied to electrical components, electric solid-state devices, circuits, etc., can solve the problems of large peripheral circuit ratio, large leakage current, and obstacles to the high integration of non-volatile memory devices, and achieve electric Excellent characteristics, prevention of leakage paths, and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

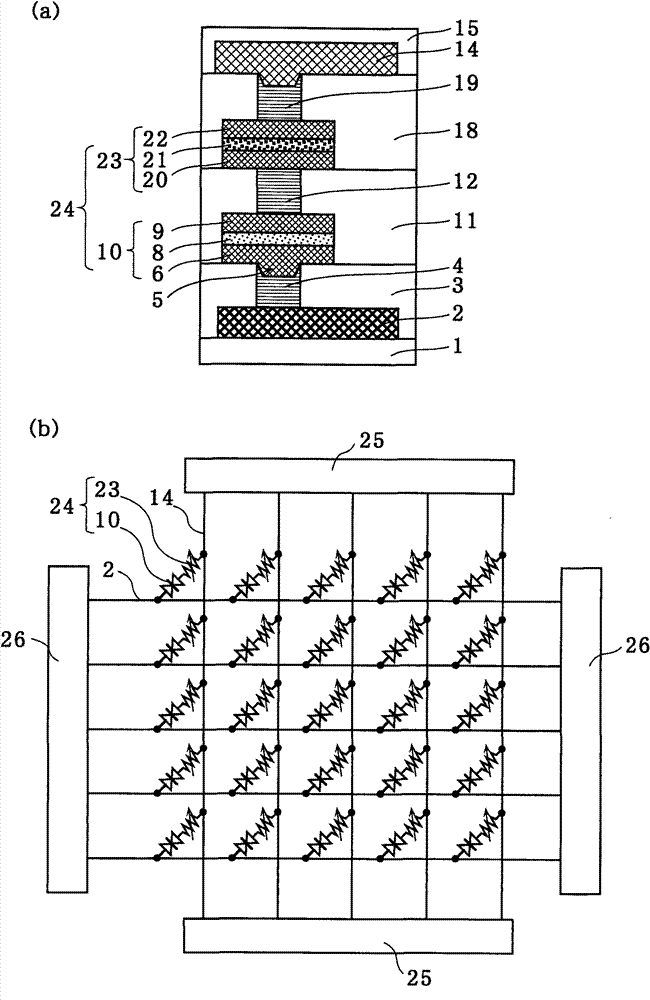

[0091] use Figure 1 to Figure 2 A memory cell array using a nonvolatile memory element in which a variable resistance element and a diode are connected in series and a method for manufacturing the memory cell array according to Embodiment 1 of the present invention are described. formed by connection.

[0092] figure 1 (a) is a schematic cross-sectional view showing an example of the structure of one memory cell used in the memory cell array according to Embodiment 1 of the present invention. figure 1 (b) is a block diagram showing an example of a functional configuration of a nonvolatile memory device configured by arranging these memory cells in a matrix.

[0093] Such as figure 1 As shown in (a), the memory cell of the first embodiment is formed on the semiconductor substrate 1 . For example, semiconductor substrate 1 is composed of a silicon substrate. A first conductor layer 2 is formed above a semiconductor substrate 1 , and a first interlayer insulating film 3 is ...

Embodiment approach 2

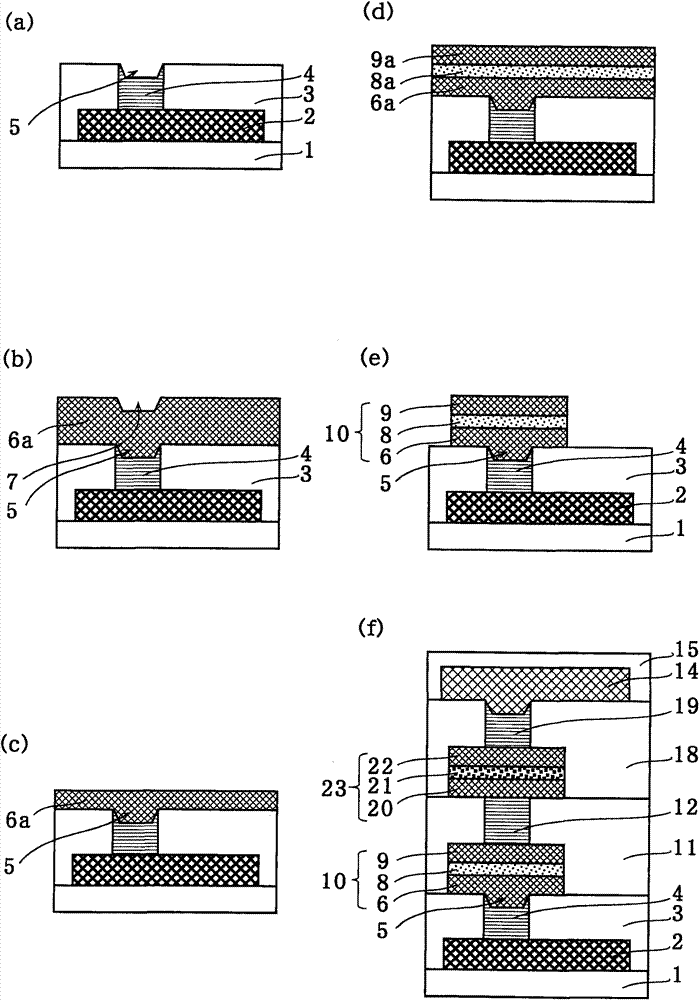

[0133] For the memory cell according to Embodiment 2 of the present invention, using Figure 3 to Figure 4 Be explained.

[0134] image 3 It is a schematic cross-sectional view showing an example of the structure of the memory cell according to the second embodiment.

[0135] Such as image 3 As shown, the memory cell of the second embodiment is different from the memory cell of the first embodiment in that the upper surface of the first electrode 6 located directly above the first plug 4 is concave toward the substrate. This recess is called a second recess 7 . The depth of the second concave portion 7 is formed smaller than the depth of the first concave portion 5 .

[0136] Compared with the memory cell of Embodiment 1, the memory cell of Embodiment 2 has the second recess 7 on the top of the first electrode 6, and the current control layer 8 and the second electrode 9 located on the top of the second recess 7 Except for the difference in shape, the number of laminate...

Embodiment approach 3

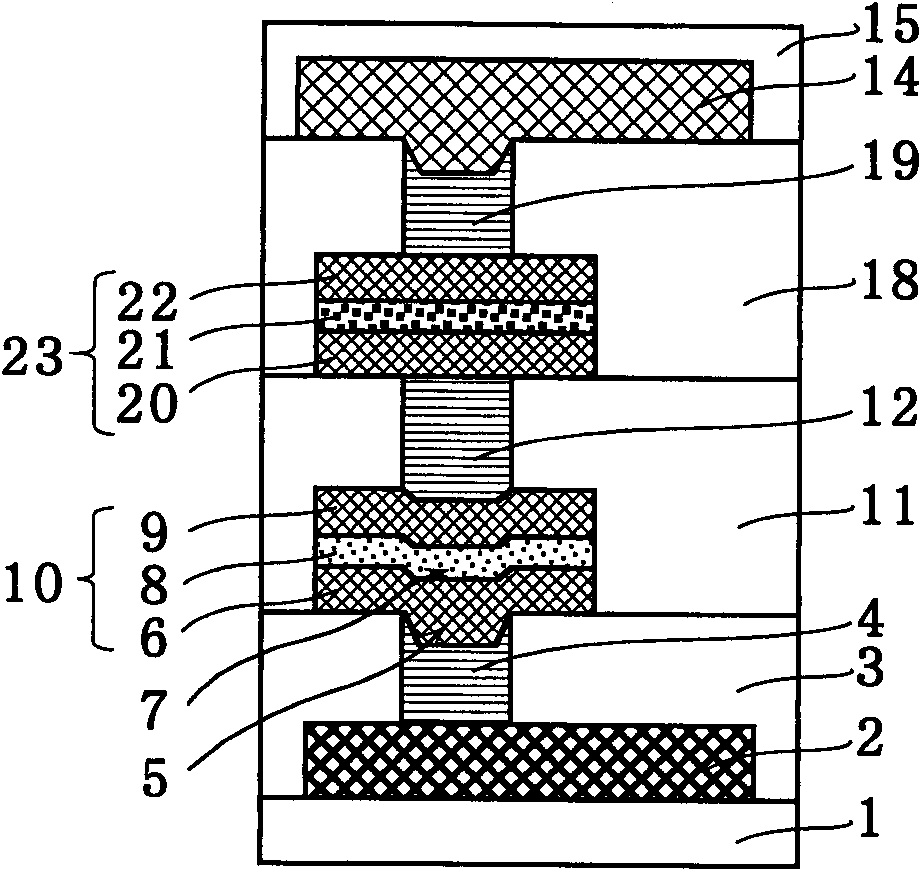

[0152] For the memory cell according to Embodiment 3 of the present invention, using Figure 5 to Figure 6 Be explained.

[0153] Figure 5 It is a schematic cross-sectional view showing an example of the structure of the memory cell according to the third embodiment.

[0154] Such as Figure 5 As shown, the memory cell of the third embodiment shares the second electrode 9 of the current steering element 10 and the lower electrode 20 of the variable resistance element 23 in the memory cell of the first embodiment, so that the current steering element 10 and the variable resistance element 23 formed as one. Furthermore, the second interlayer insulating film 11 and the second plug 12 in the memory cell of Embodiment 1 are omitted.

[0155] The structure of the memory cell of Embodiment 3 is the same as the structure of the memory cell of Embodiment 1 except for the differences described above. Hereinafter, for convenience of explanation, the respective constituent elements ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More