Circuit simulation method for realizing parallel computation through time domain division

A circuit simulation and circuit technology, which is applied in the field of analysis to obtain the time domain characteristics of circuits, and can solve problems such as improved efficiency and large amount of calculation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The specific content of this method will be further described in detail below in conjunction with the accompanying drawings and examples.

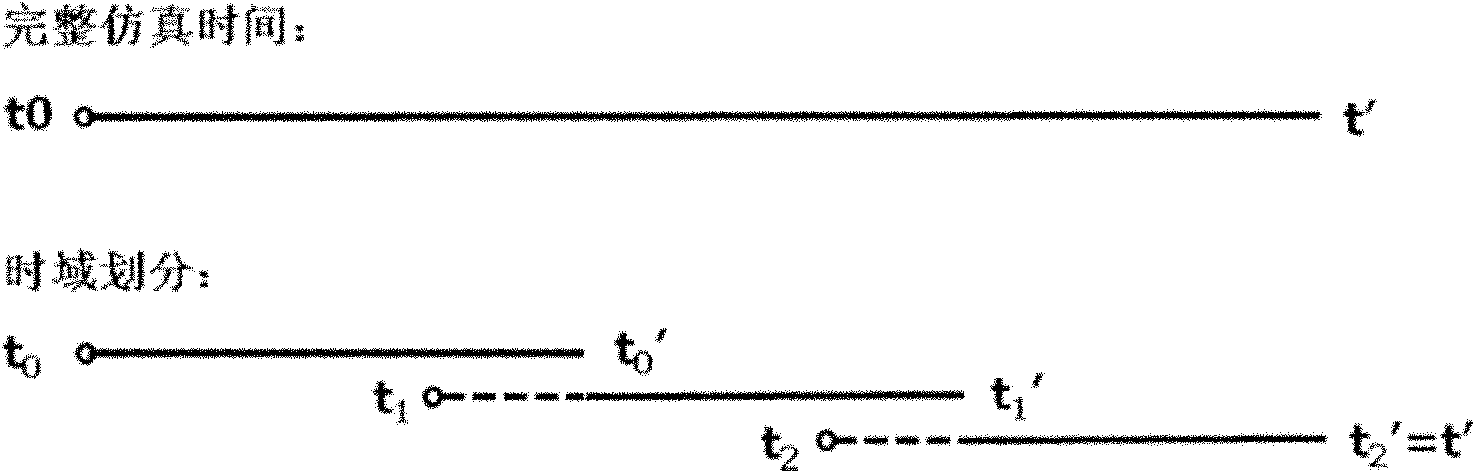

[0033] The circuit emulation method that the present invention proposes realizes parallel computing through time domain division, comprises the following steps:

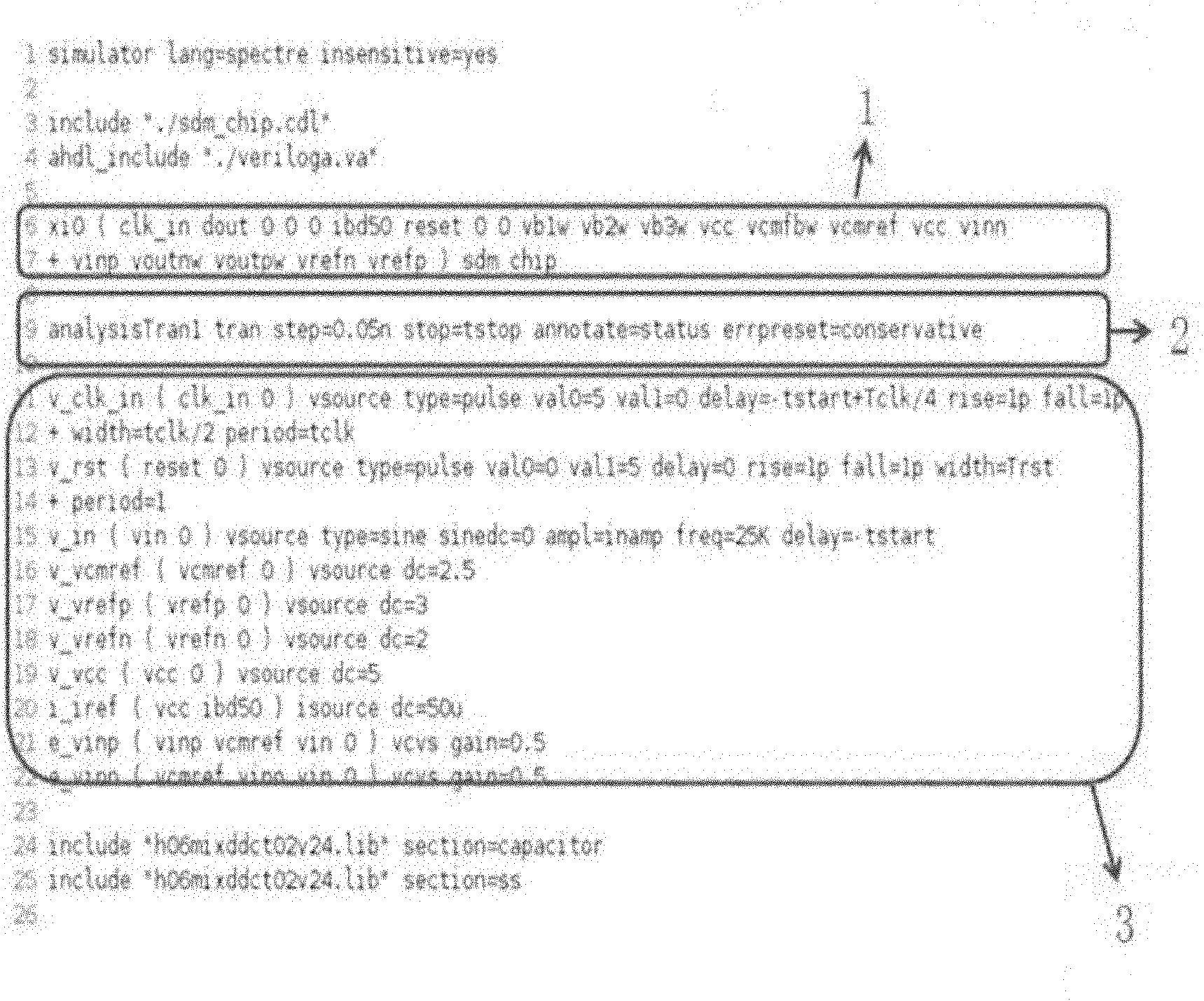

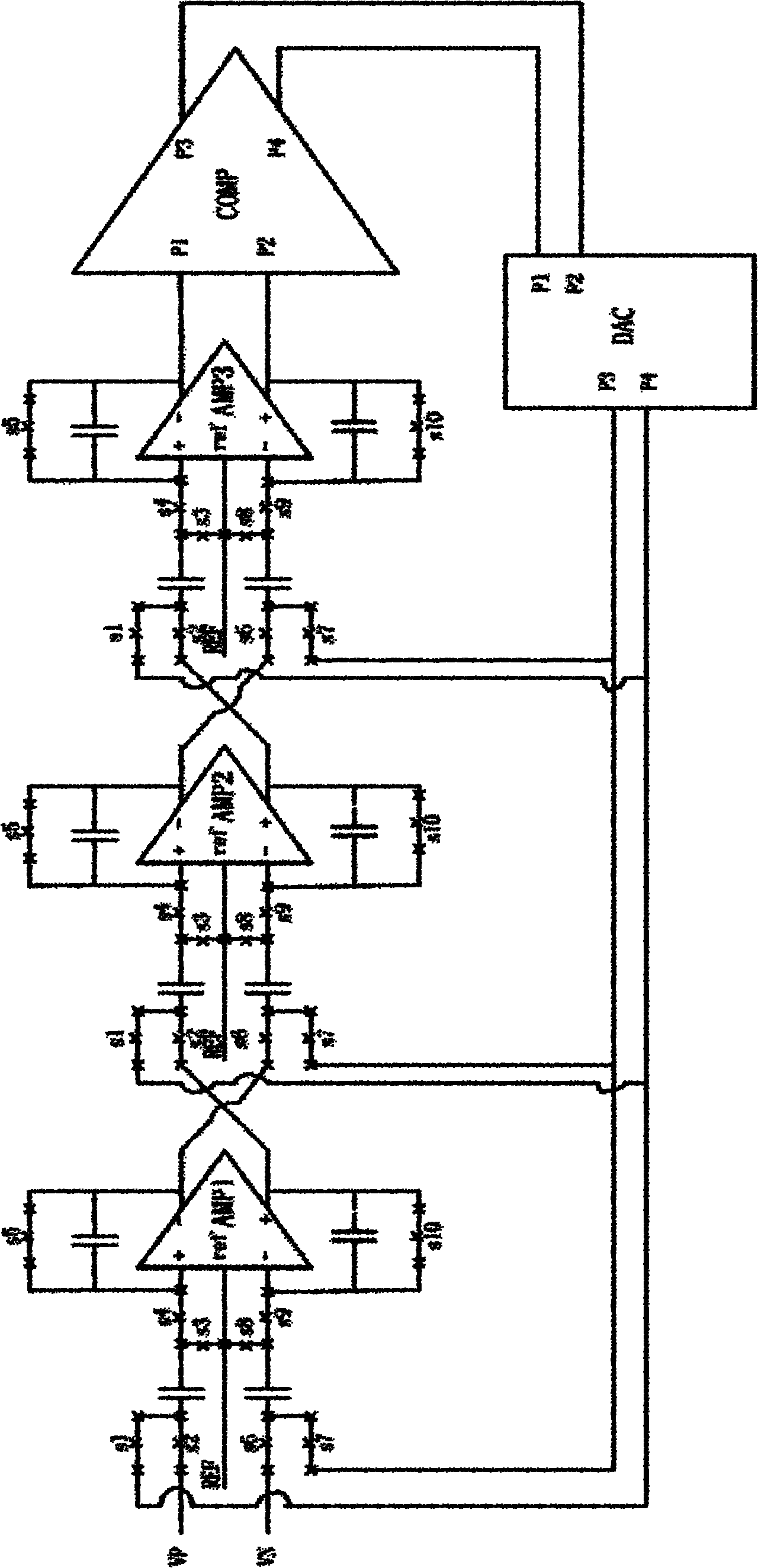

[0034] 1) Given an input file for circuit simulation, the file is used to describe the topology of the circuit to be simulated, external excitation signals and simulation parameters (usually such files are in the form of a circuit net list, but not limited to this form); Among them, the topology of the circuit is the circuit itself to be analyzed, the external excitation signal is the excitation waveform used to simulate the response of the circuit under a certain input, and the simulation parameters are calculations such as initial time, termination time, and simulation accuracy and other parameters. An example of an input file is figure 1 shown. This document describe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More