Switch-body PMOS switch with switch-body dummies

A switch and body technology, applied in electronic switches, transistors, electrical components, etc., can solve the problem of not reaching the performance of S/H devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

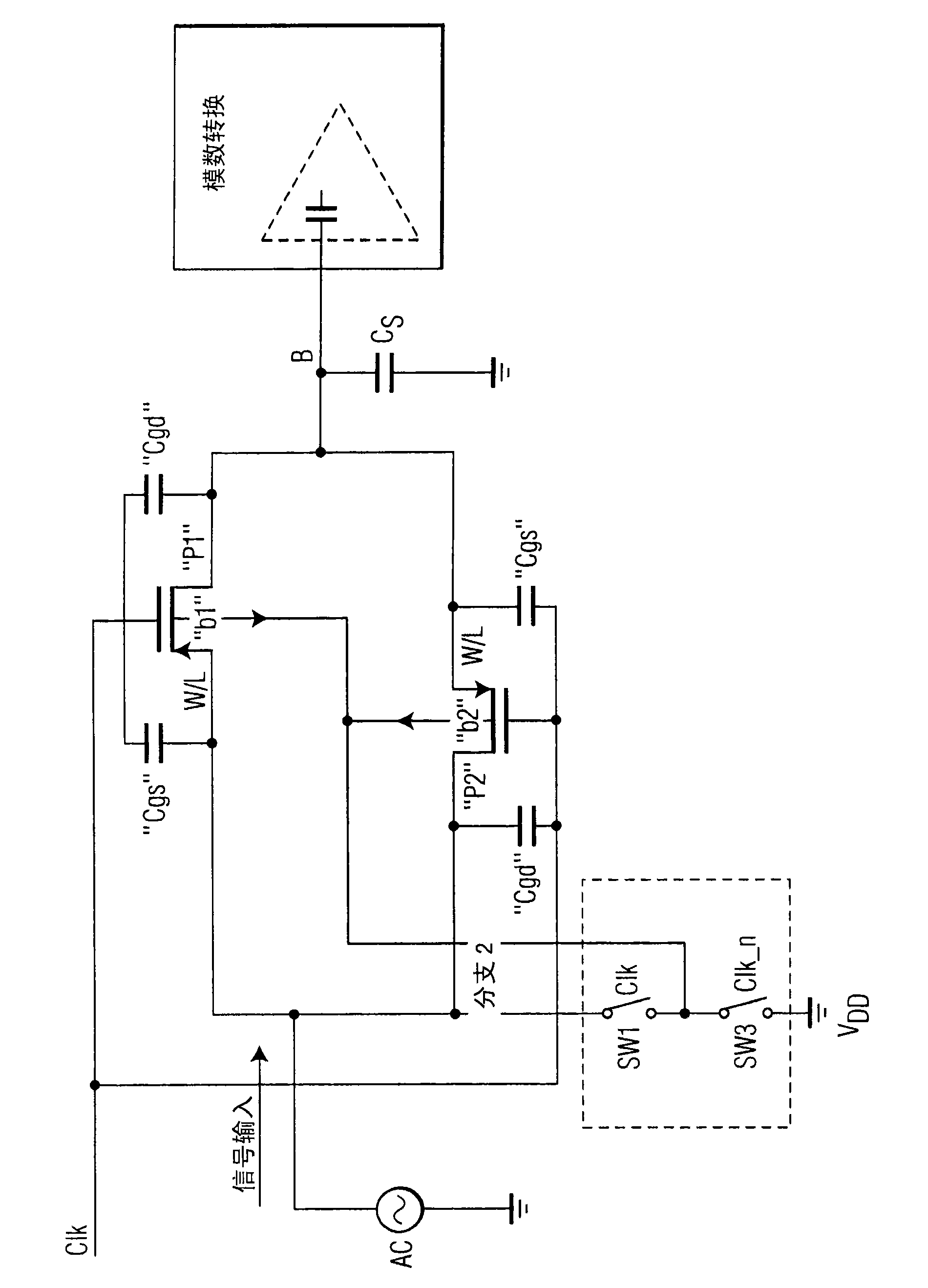

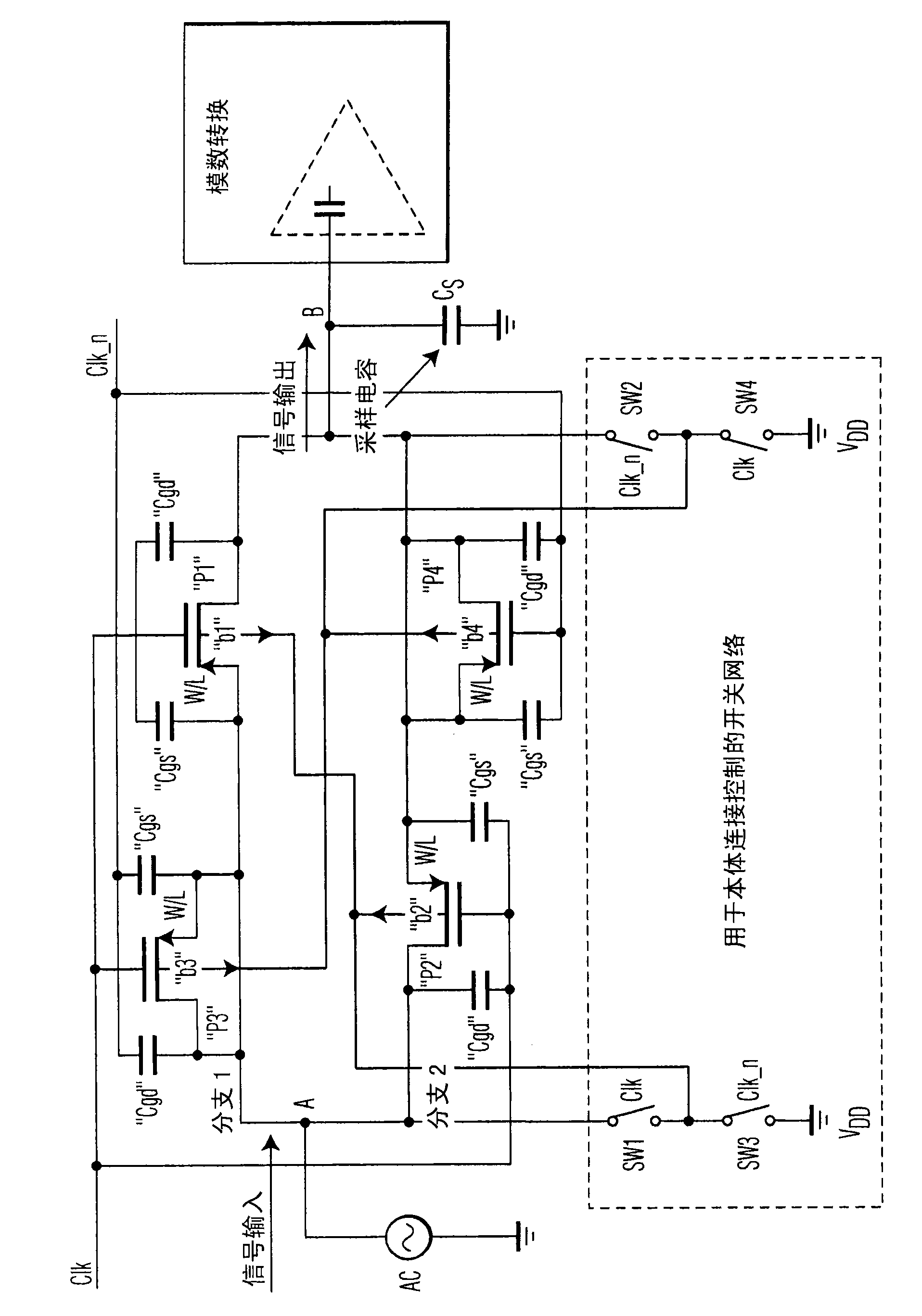

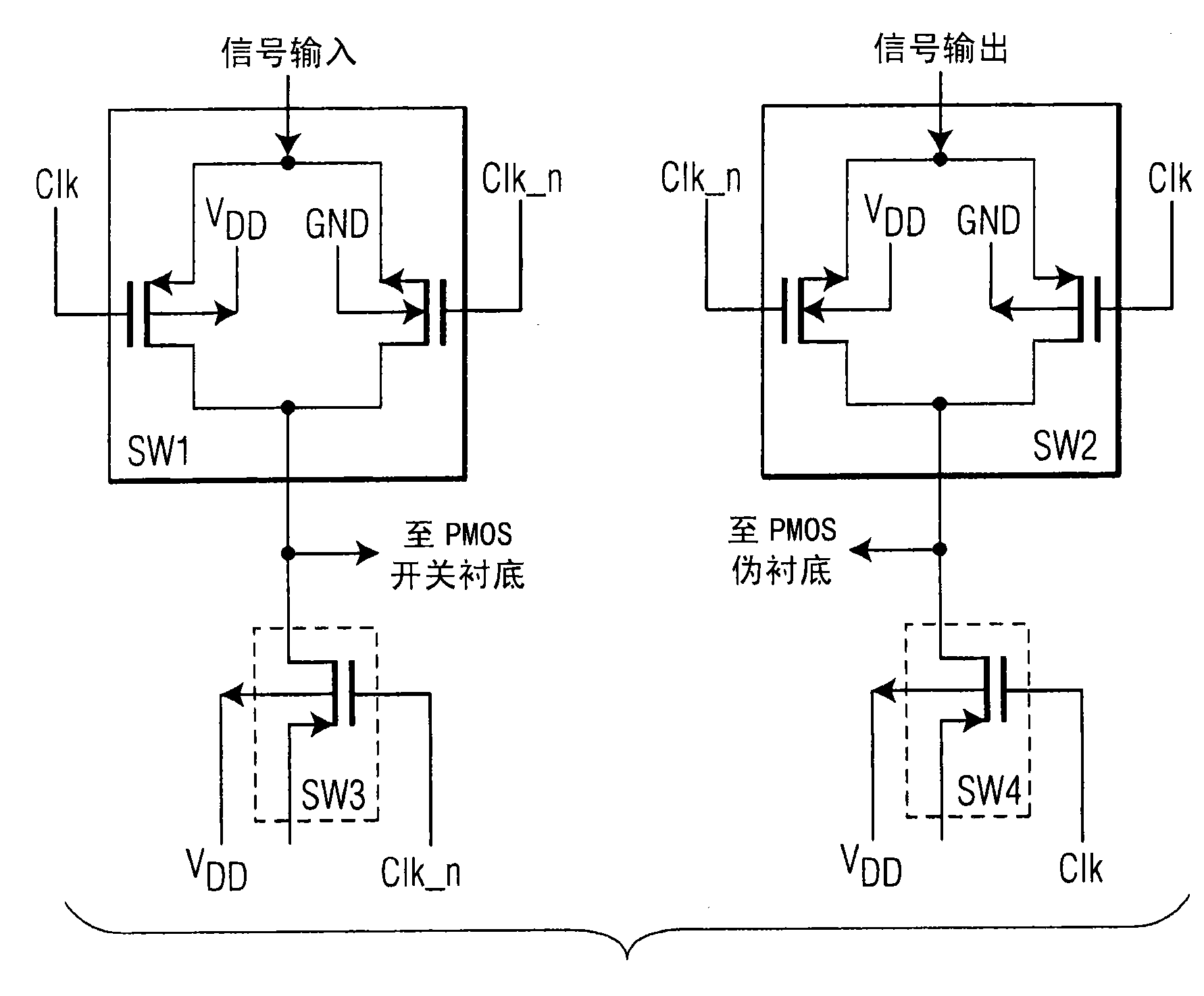

[0033] Various examples with one or more example embodiments are described with reference to specific example configurations and arrangements. For illustrative purposes only, specific examples are selected to further assist those of ordinary skill in the field of sampling and holding circuits to develop an understanding of the concept of the present invention, which is sufficient to enable these technicians to apply their knowledge and skills to practice the present invention. However, the scope of the embodiments and the scope of implementation are not limited to these specific illustrative examples. On the contrary, those of ordinary skill in the sampling and holding field will recognize when reading this specification that other configurations, arrangements, and implementations of one or more embodiments and one or more aspects of each embodiment can be designed and constructed. .

[0034] The accompanying drawings are used to clearly illustrate the exemplary subject matter s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More