Pipeline ADC employing integral non-linear error correction

A nonlinear error and assembly line technology, applied in the direction of physical parameter compensation/prevention, analog/digital conversion calibration/test, analog-to-digital converter, etc., can solve the problems of rapid error movement and detection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] The present invention will now be described with reference to particular embodiments and certain drawings but the invention is not limited thereto but only by the claims.

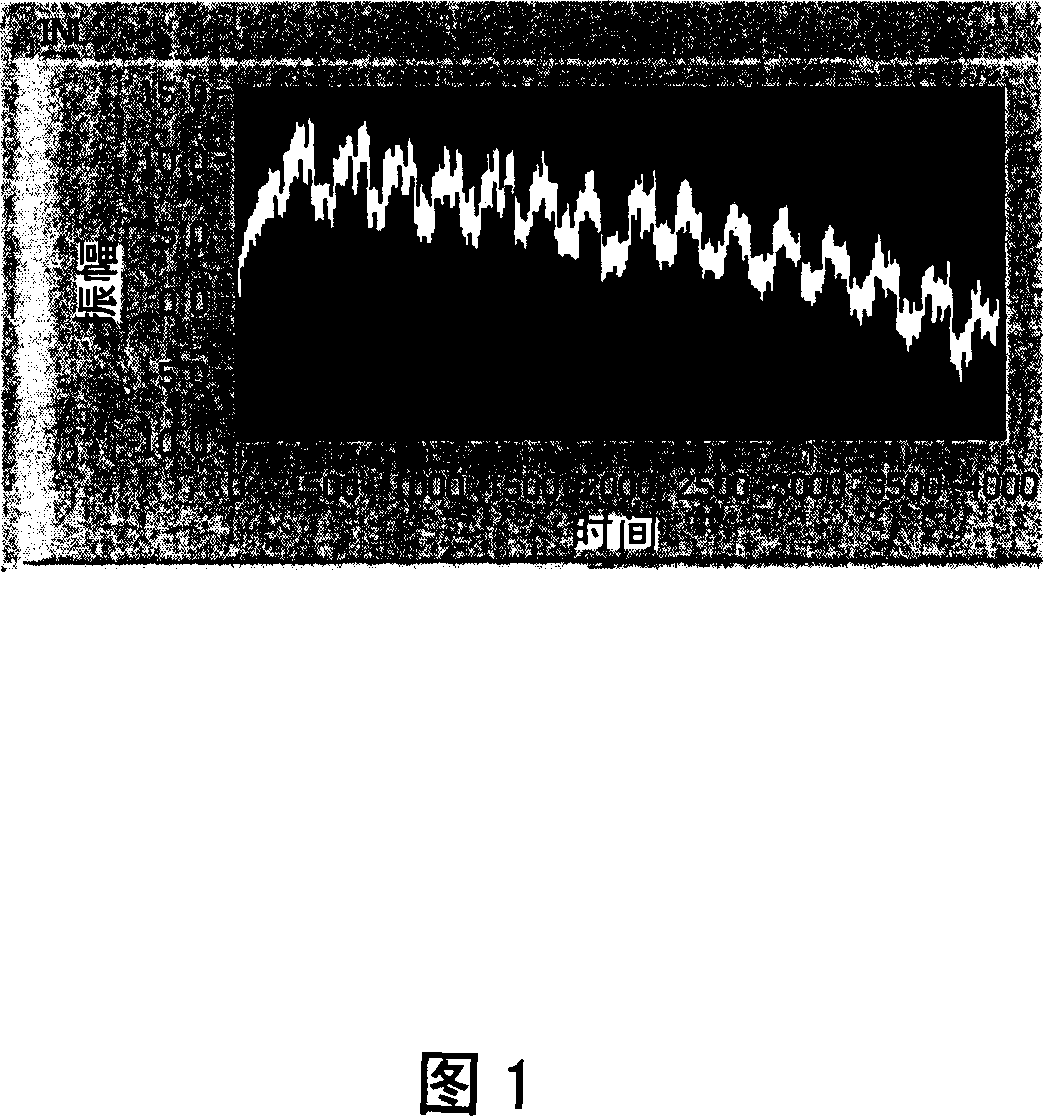

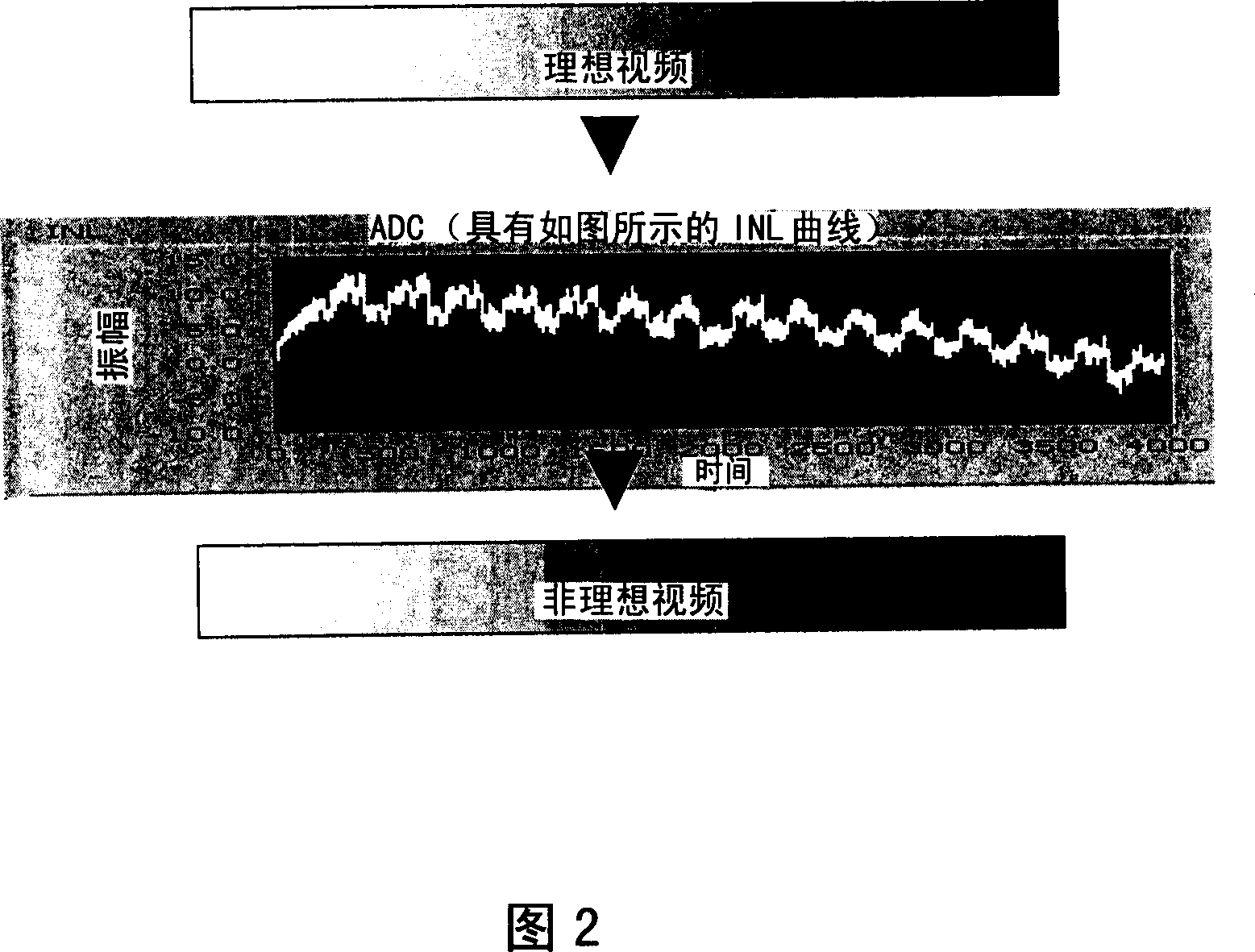

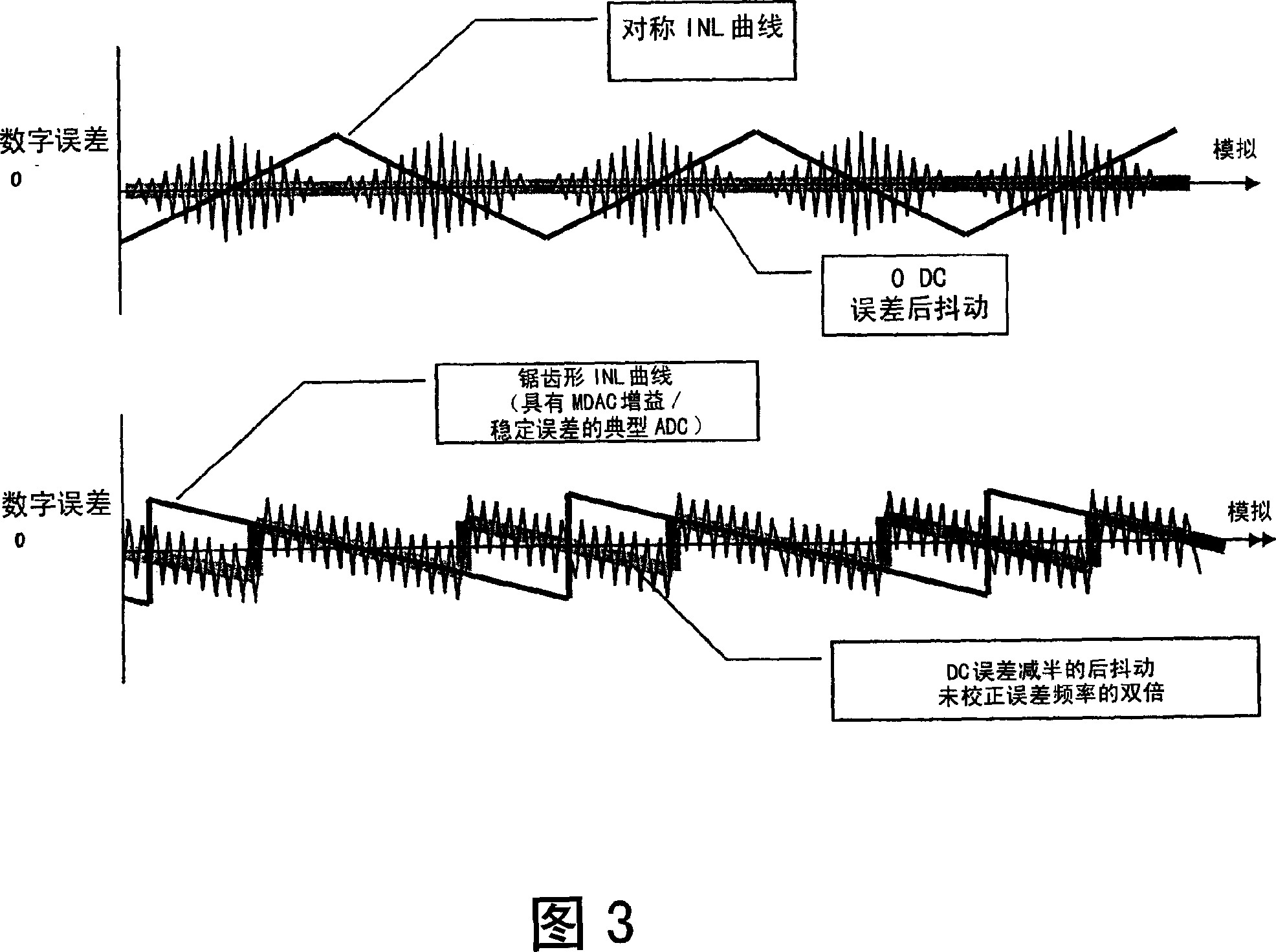

[0059] As discussed in the background section, the dithering method consists of adding a fixed dither of Fs / 2 in the analog domain, and selecting the amount of dithering that matches the ADC INL characteristic, and removing the dithering in the digital domain. The effect of the dithering method depends on the INL Properties of the curve properties. It has been determined that square or triangular waveforms are all corrected. However, for a sawtooth waveform, this scheme results in half the error signal being modulated to fs / 2, although the frequency of the residue is doubled. This means that as the ADC sampling rate increases, the dithering scheme cannot fully effectively account for distortion and settling errors related to amplifier gain. This can be seen from the graph of Figure 3, which shows h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More