Digital downconverter with variable bandwidth and implementation method thereof

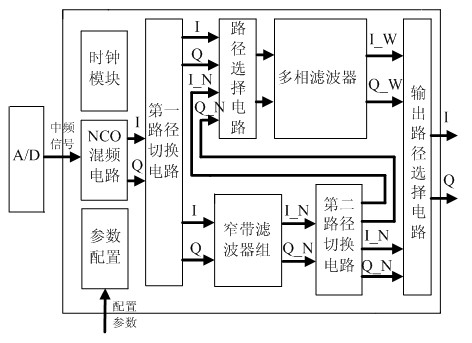

A digital down-converter and variable bandwidth technology, applied in the electronic field, can solve the problems of multiplier operating frequency reduction, fixed processing bandwidth, unsuitable for wideband digital receivers, etc., and achieve the effect of flexible configuration, high-efficiency and high-speed processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

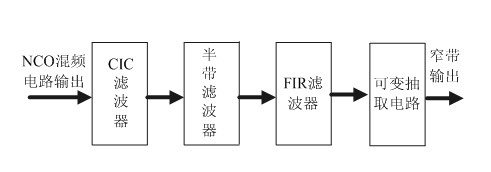

specific Embodiment 1

[0054] Set the system parameters as follows:

[0055] (1) Realize digital down-conversion, reduce the signal data rate, reduce the AD sampling rate of 100MSPS by 131072 times, and output the baseband signal data rate of 762.94SPS.

[0056] (2) The carrier frequency of the intermediate frequency signal is 32.4MHz, and the signal bandwidth is 150Hz.

[0057] (3) Complete output signal shaping to meet subsequent signal processing requirements.

[0058] Receive external signals to set the parameter configuration module, the required parameters are as follows:

[0059] (1) The width of the NCO phase accumulation word (phi_inc_i) is 27 bits, and the frequency of the NCO output local oscillator signal can be changed by changing the value of the phase accumulation , whose calculation formula is: . When the NCO output local oscillator frequency is 32.4MHz, . NCO is implemented using the CORDIC algorithm, and the structure is as follows Image 6 As shown, a 16-stage pipeline i...

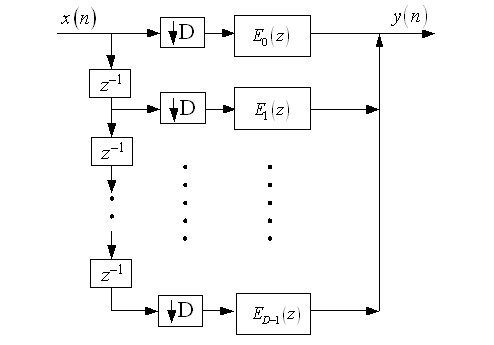

specific Embodiment 2

[0067] Set the system parameters as follows:

[0068] (1) Realize digital down-conversion, reduce the signal data rate, reduce the AD sampling rate 100MSPS by 2 times, and output the baseband signal data rate 50MSPS.

[0069] (2) The carrier frequency of the intermediate frequency signal is 21.4MHz, and the signal bandwidth is 40MHz.

[0070] (3) Complete output signal shaping to meet subsequent signal processing requirements.

[0071] Receive external signals to set the parameter configuration module, the required parameters are as follows:

[0072] (1) The width of the NCO phase accumulation word (phi_inc_i) is 27 bits, and the frequency of the NCO output local oscillator signal can be changed by changing the value of the phase accumulation , whose calculation formula is: . When the NCO output local oscillator frequency is 21.4MHz, . NCO is realized by CORDIC algorithm, the structure is as follows Figure 4 As shown, a 16-stage pipeline is adopted.

[0073] (2) Co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More