Preparation method of field effect transistor

A field-effect transistor and bulk substrate technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of poor miniaturization capability, complex process and high cost, and achieve the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0036] The preparation method of the field effect transistor of the present invention can be applied to N-type transistors and P-type transistors, the difference between the two is that the type of doping of the substrate and the source and drain regions is exchanged, that is, the substrate of the N-type transistor is doped with P Type impurities, P-type transistor substrate doped with N-type impurities.

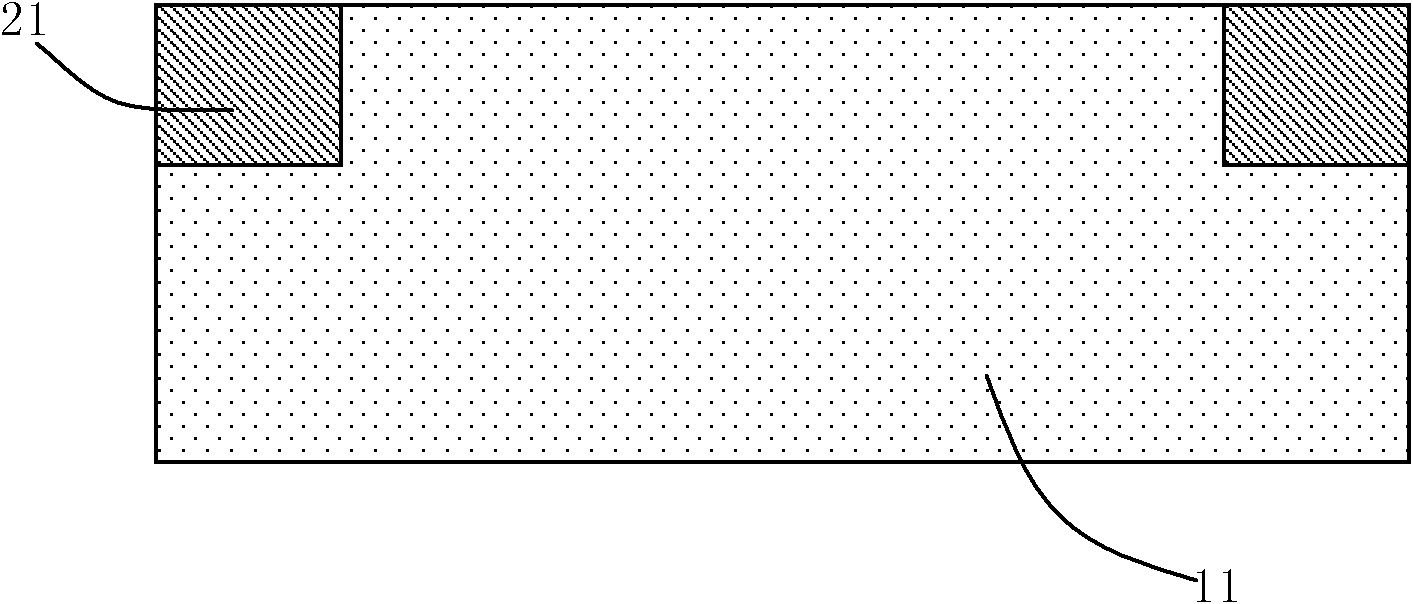

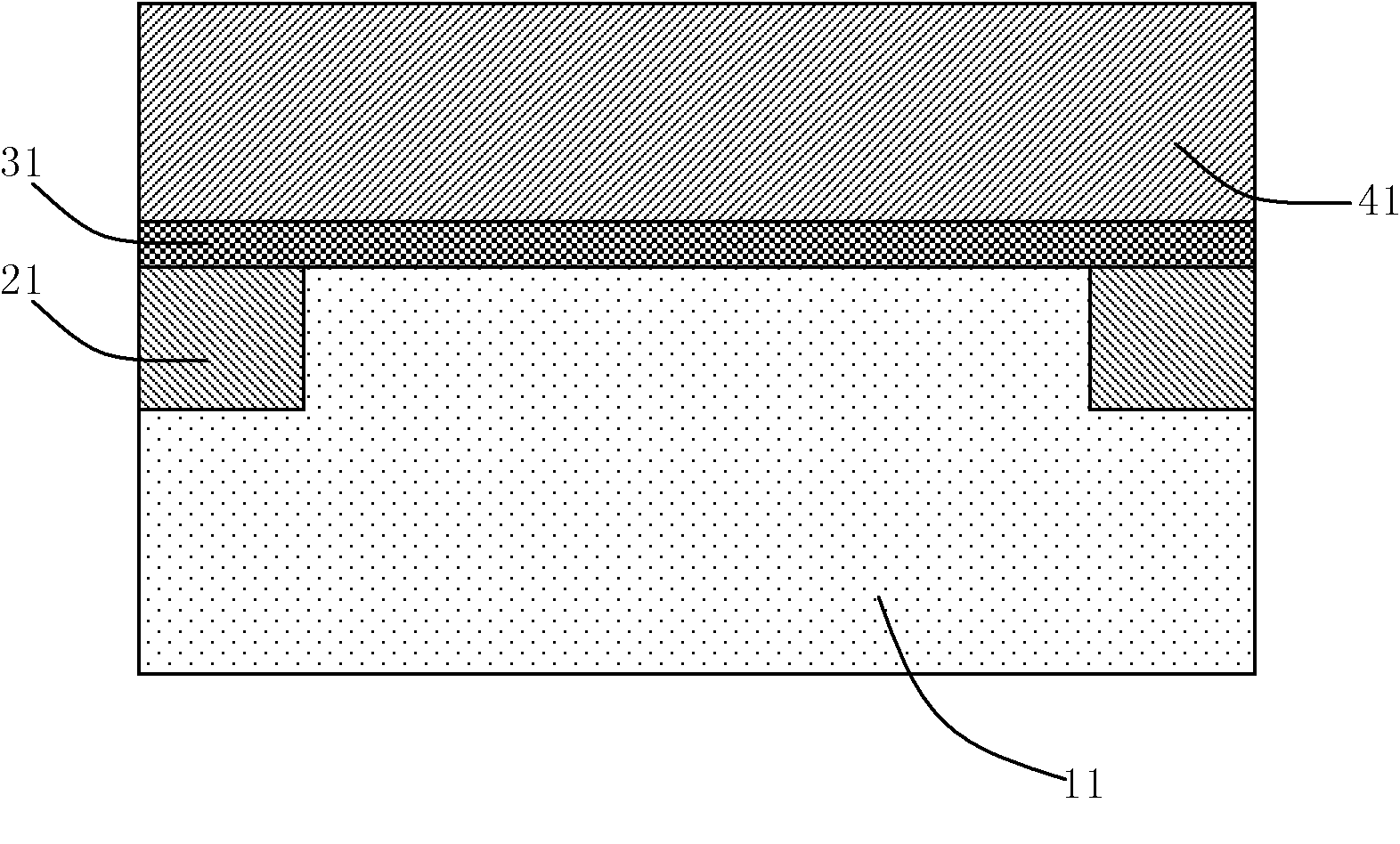

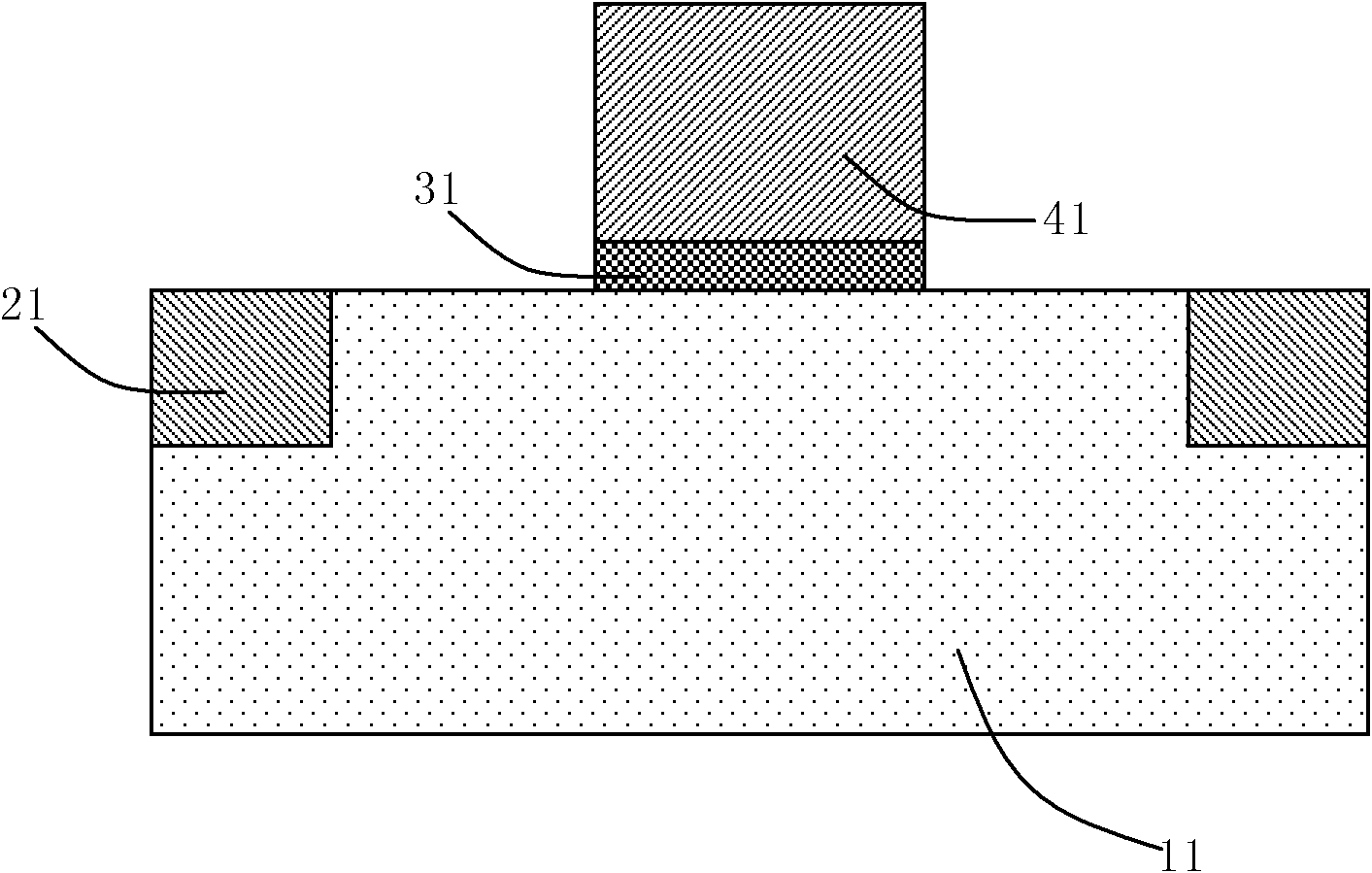

[0037] Please refer to Figure 1-6 , taking the N-type field effect transistor as an example, the preparation method of the field effect transistor of the present invention comprises the following steps:

[0038] (1) Provide a P-type bulk silicon substrate 11, use photolithography and etching methods to form shallow trenches, and grow silicon dioxide in the shallow trenches to form shallow trench isolation structures 21 (Shallow TrenchIsola...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More