Low voltage differential signaling (LVDS) interface circuit based on field programmable gate array (FPGA) and data transmission method

An interface circuit and data technology, applied in the direction of logic circuit connection/interface layout, etc., can solve the problems between difficult efficiency and training time, maintain balance, complex clock design scheme, etc., achieve high transmission rate, simplify PCB design, save effect of numbers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In the following, the principle and implementation of the present invention will become apparent by describing specific embodiments of the present invention in conjunction with the accompanying drawings. It should be noted that the present invention should not be limited to the specific examples described below.

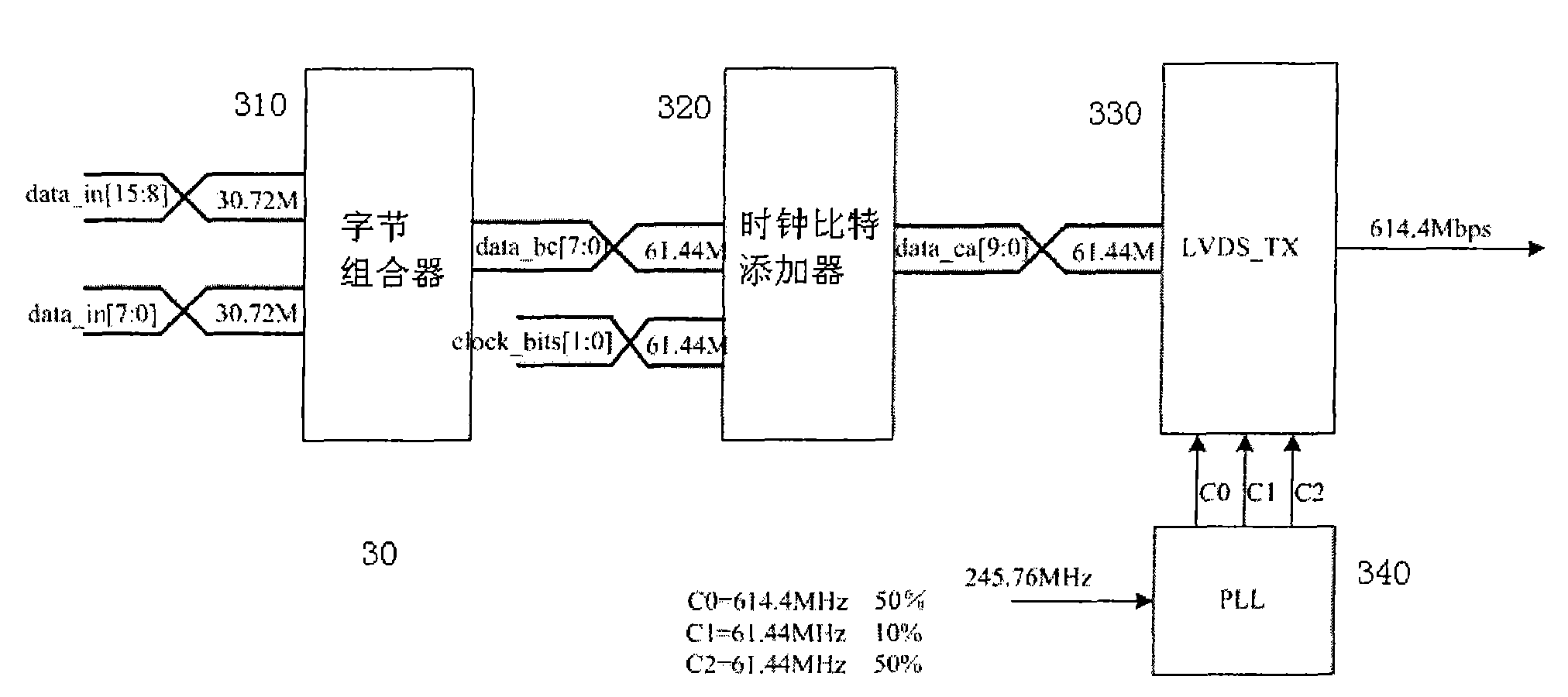

[0030] image 3 is a block diagram showing an FPGA-based LVDS interface circuit for converting parallel data into serial data according to one embodiment of the present invention. Such as image 3 As shown, LVDS interface circuit 30 includes byte combiner 310 , clock bit adder 320 , LVDS-TX interface 330 and PLL 340 . The byte combiner 310 converts multiple channels of low-speed parallel data into one channel of high-speed parallel data for subsequent processing. For illustration, take two-way parallel data as an example. Such as image 3As shown, the byte combiner combines two channels of 8-bit data with a frequency of 30.72MHz into one channel of 8-bit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More