Circuit for parallelly encoding quasi-cyclic low-density parity check code

A low-density parity and coding circuit technology, which is applied in the field of quasi-cyclic low-density parity-check code parallel coding circuits, can solve the problems of high storage cost, unsatisfactory matrix rank, slow speed, etc., and achieves low coding complexity and low storage cost. , fast effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be described in detail below in conjunction with the accompanying drawings.

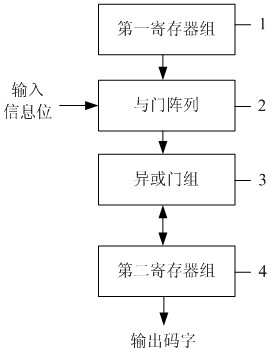

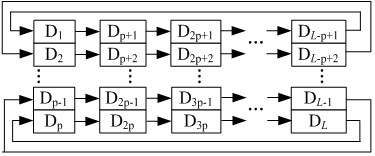

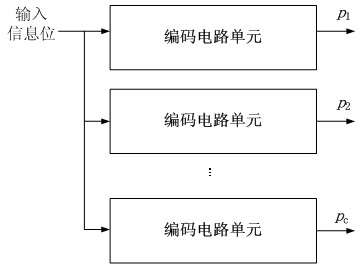

[0018] Such as figure 1 As shown, the quasi-cyclic low-density parity-check code parallel encoding circuit is characterized in that it includes one or more encoding circuit units, and the encoding circuit unit includes a first register group 1, an AND gate array 2, an exclusive OR gate group 3 and a second Register group 4; the first register group 1 and the second register group 4 according to the dimension of the cyclic permutation matrix L Both by L registers; the XOR gate group 3 is based on the dimension of the cyclic permutation matrix L Depend on L An XOR gate is formed; the output end of the first register group 1 is connected to the input end of the AND gate array 2, the output end of the AND gate array 2 is connected to the input end of the XOR gate group 3, and the XOR gate group 3's input end is connected. The output end is connected with the input en...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More