Method for carrying out optimized speed classification for digital integrated circuit with transparent latch

A technology of integrated circuits and latches, applied in electrical digital data processing, instruments, special data processing applications, etc., can solve problems such as not necessarily satisfied, time-consuming, difficult to obtain random clock cycle distribution, etc., to minimize test costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

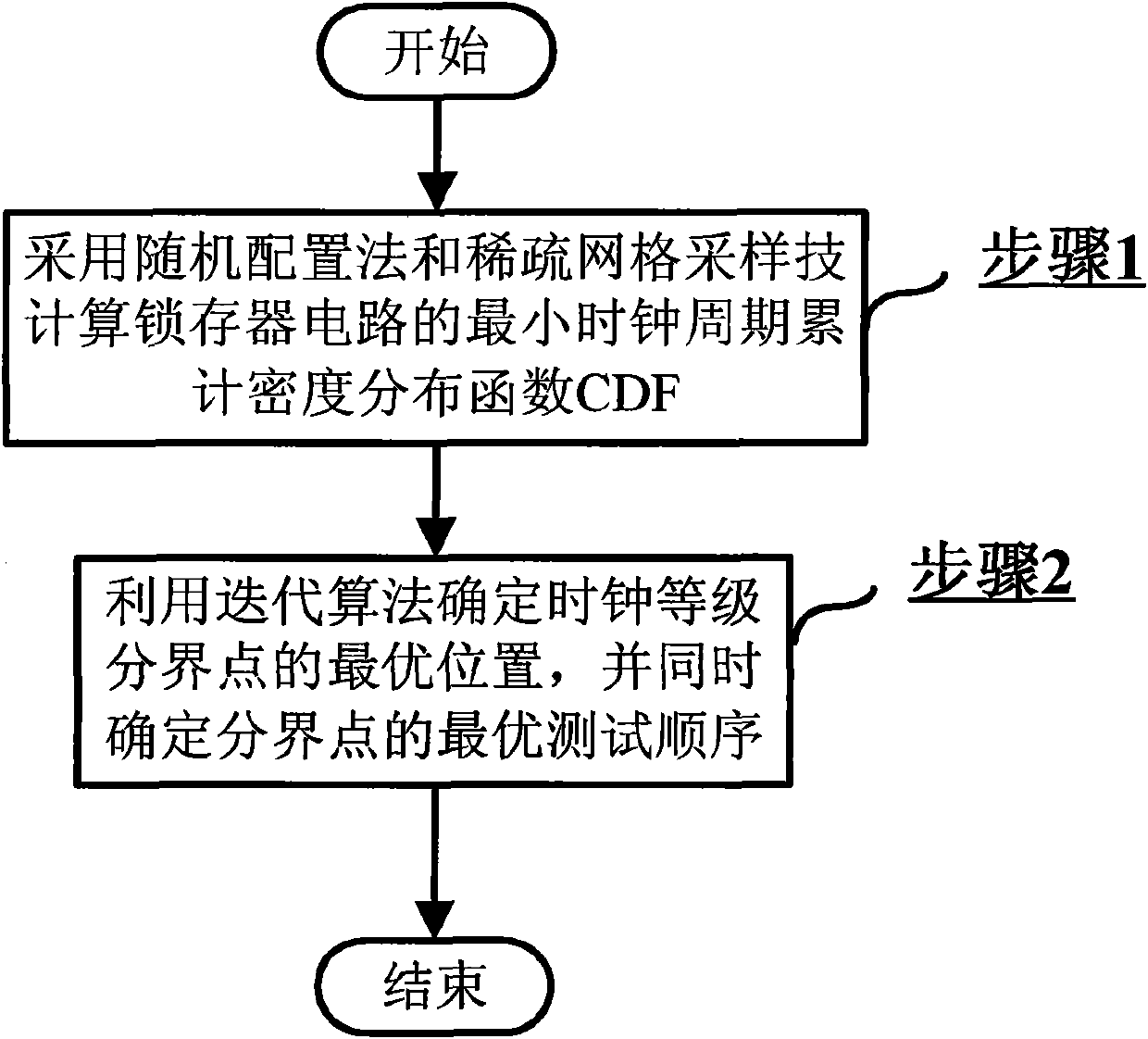

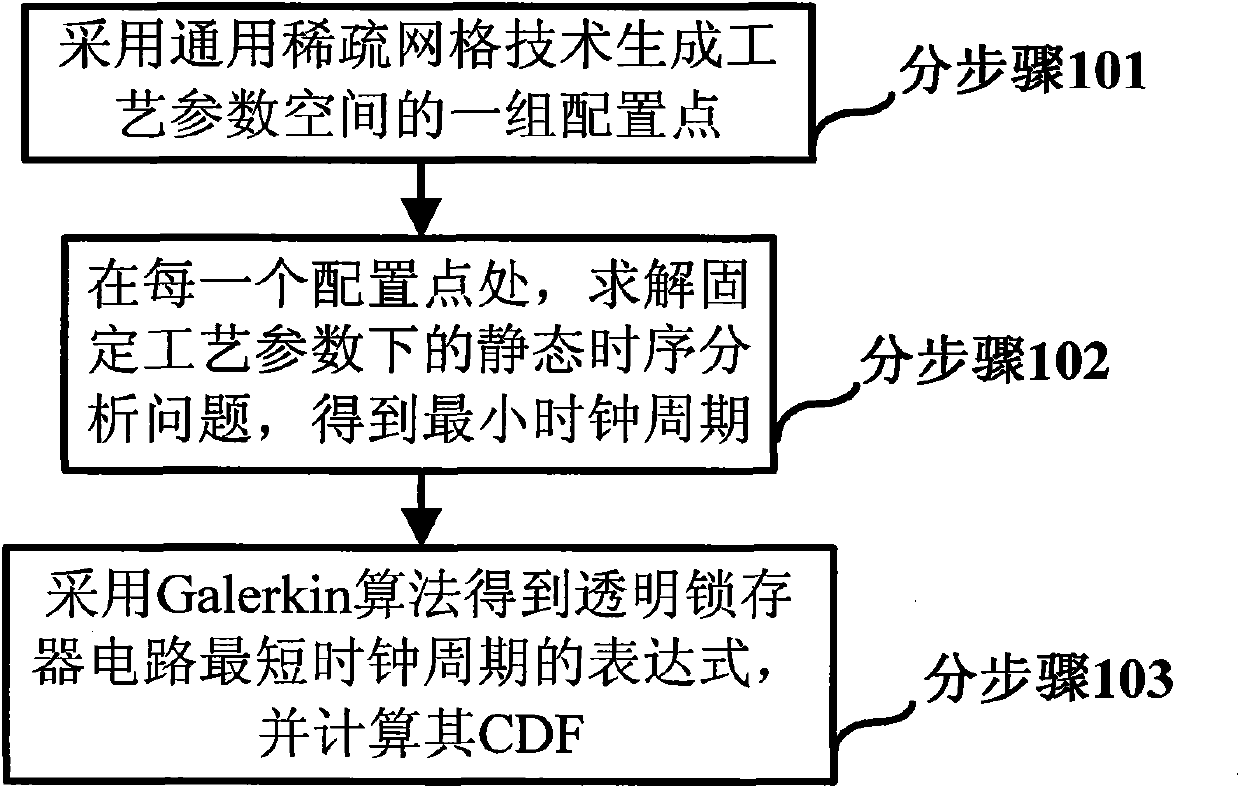

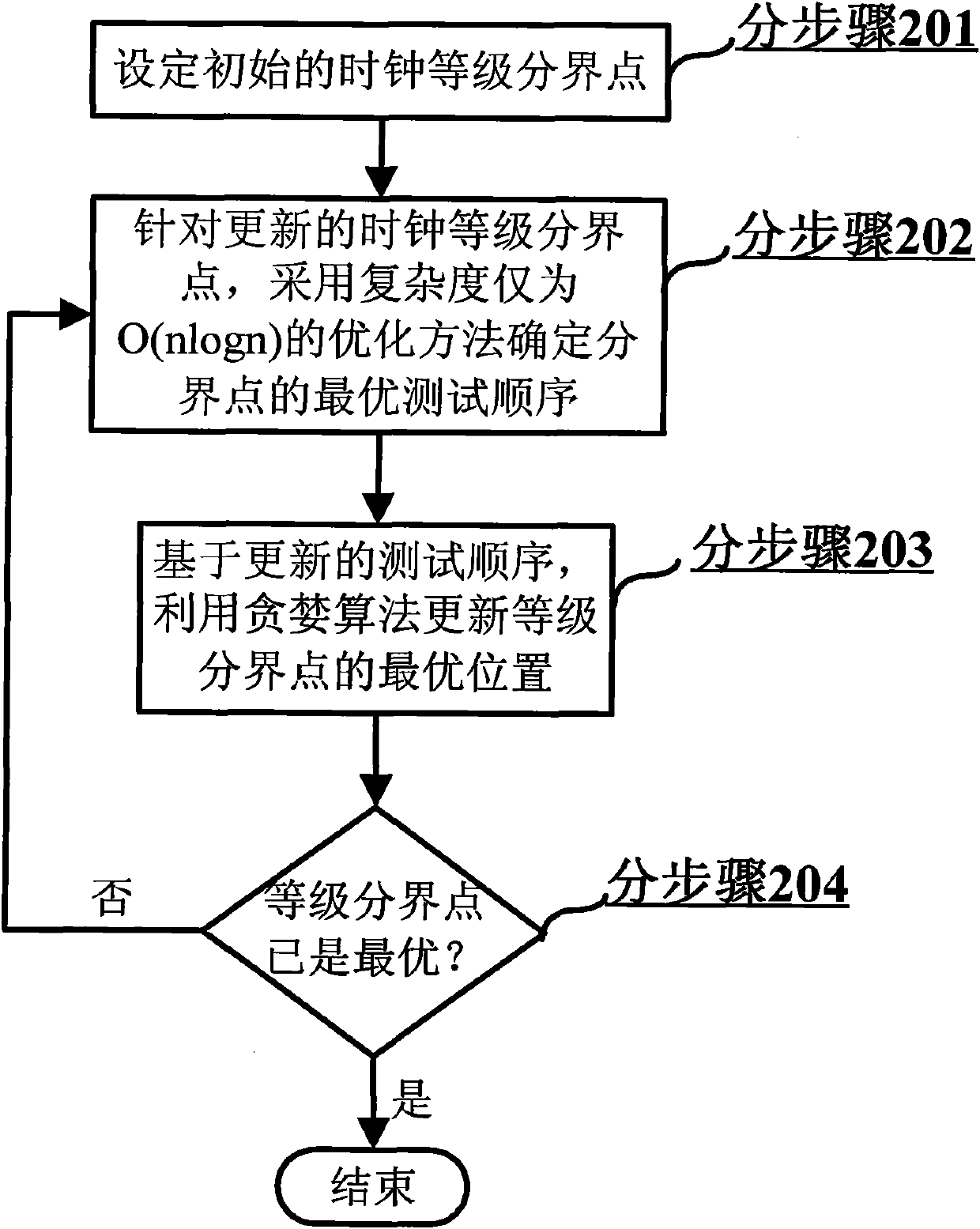

[0043] According to the principle of the present invention, its technical solution mainly includes two aspects: the calculation of the statistical clock cycle, the position of the boundary point of the clock cycle level and the optimization of the test sequence. Combine below Figure 1-Figure 4 The method flowchart to describe its following specific steps:

[0044] step 1 : To calculate the statistical distribution of the minimum clock period of a digital integrated circuit with a transparent latch, statistics based on the generalized Stochastic Collocation Method (gSCM, generalized Stochastic Collocation Method) and sparse grid sampling technology (Sparse-Grid Sampling) can be used The static timing analysis method computes the statistical distribution of the minimum clock period for a transparent latch circuit.

[0045] Assume Represents a set of independent random variables with arbitrary distribution obtained after PCA or ICA processing the process deviation with corr...

Embodiment 2

[0131] In order to make the features and advantages of the present invention more comprehensible, the present invention will be further described below in conjunction with specific test circuits and implementations.

[0132] For the s13207 circuit in the ISCAS'89 test circuit example under the 65nm process, it is assumed that all edge trigger units in the circuit are replaced with level-sensitive transparent latches, and are driven by a single-phase clock with a 50% duty cycle. At the same time, it is assumed that a second-order delay model is used, which contains 6 independent random variables obtained by PCA or ICA (ie (1.1) where N=6, M=2), and these 6 random variables are assumed to have the characteristics of Gaussian distribution , and the variance is set to 10% of the corresponding mean. Then adopt the method of the present invention, the concrete steps that this circuit is carried out speed classification optimization are as follows:

[0133] step 1 : Computes the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More