Method for determining circuit fault based on PSPICE

A circuit fault and judgment method technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., to achieve the effects of improving efficiency, strong applicability, and reducing burden

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment example

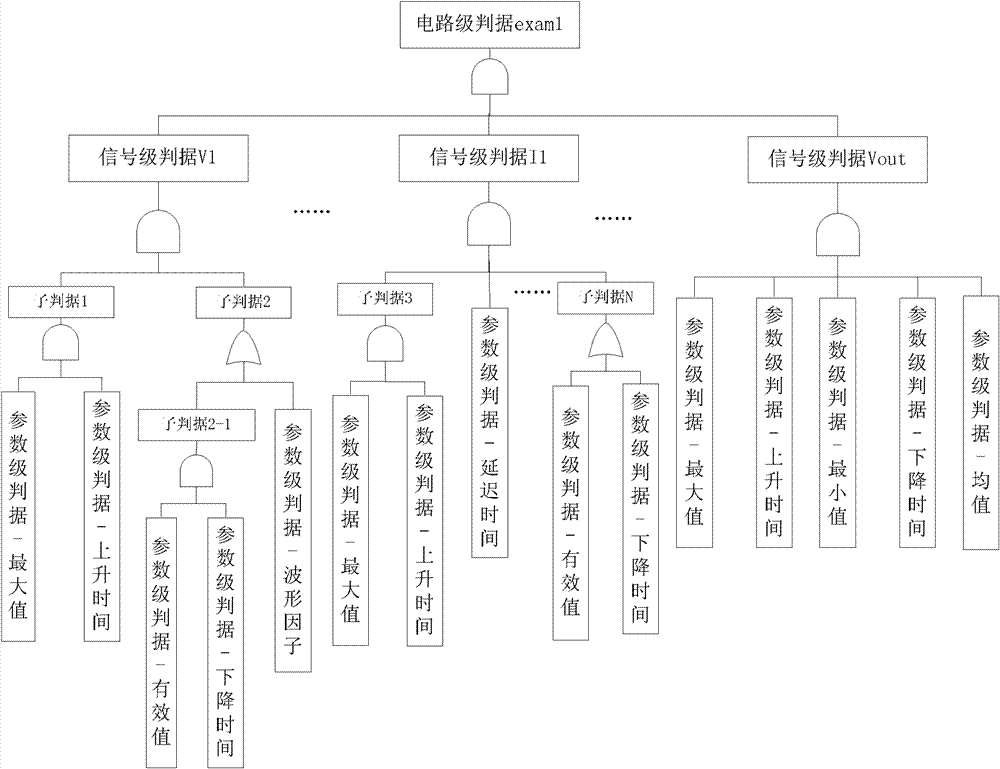

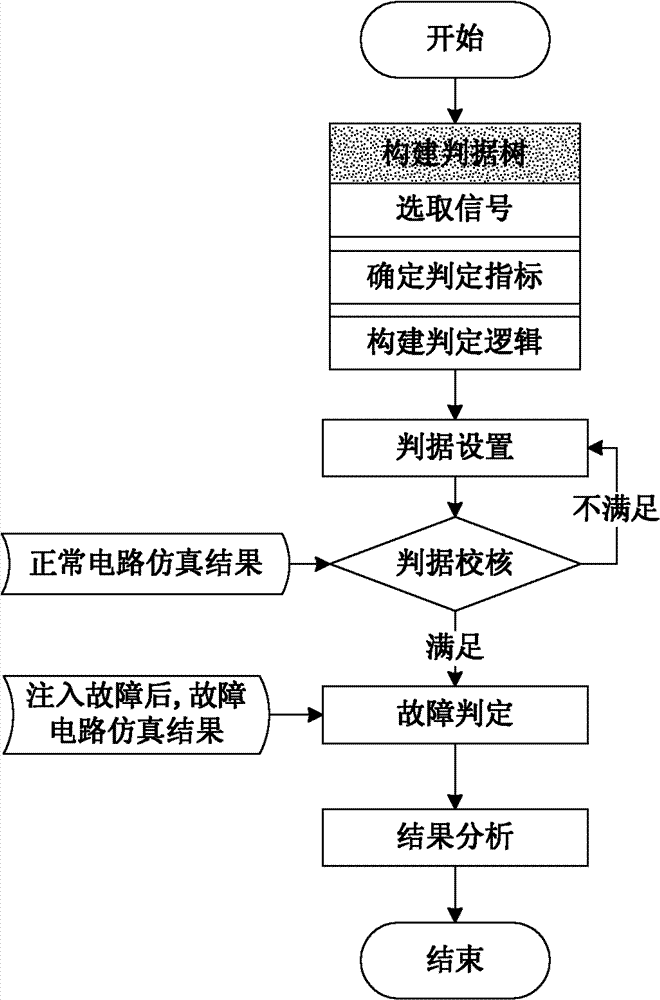

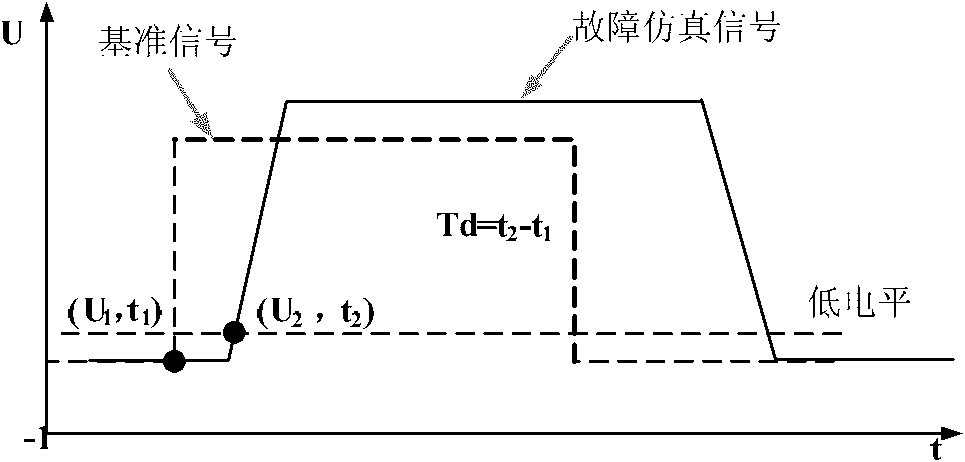

[0122] Taking the digital-analog hybrid circuit as an example, the circuit fault judgment method is explained. The schematic diagram of the circuit is shown in Figure 6 As shown, the oscillating circuit composed of inverter, Schmitt trigger, resistor, capacitor and JK trigger, its input signal is a digital pulse with a downward transition, and the output is a periodic digital signal. The steps of the case implementation process are the above three steps. For this case, the selected failure mode is the open circuit of capacitor C1. Step 1 Select the nodes I(R1), OUT and V(C1:2), and select the maximum value, duty cycle and pulse amplitude for the criterion indicators respectively. The normal waveform of the signal is as follows: Figure 7 As shown, the criterion tree is as Figure 8 shown.

[0123] Among them, I(R1) is a periodic analog signal; V(C1:2) is an analog digital signal, and it can be found that its waveform shape is roughly a square wave, but the description met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More