Quick LU factorization method for circuit sparse matrix in circuit simulation

A technology of sparse matrix and circuit simulation, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the time-consuming problems of circuit matrix LU decomposition, and achieve the effect of reducing the time of LU decomposition and reducing the time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Although many scholars have considered the characteristics of the circuit matrix when writing LU decomposition software, they have made corresponding improvements on the basis of the left-looking algorithm (for example, KLU has abandoned Supernode in SuperLU and used Block Triangular Form , BTF) method), but no scholars have combined the characteristics of the circuit simulation process to separate the symbolic analysis and numerical decomposition in the LU decomposition to reduce the number of executions of the same symbolic analysis, thereby reducing the LU in the entire circuit simulation process. Break down the complexity and reduce the processing time.

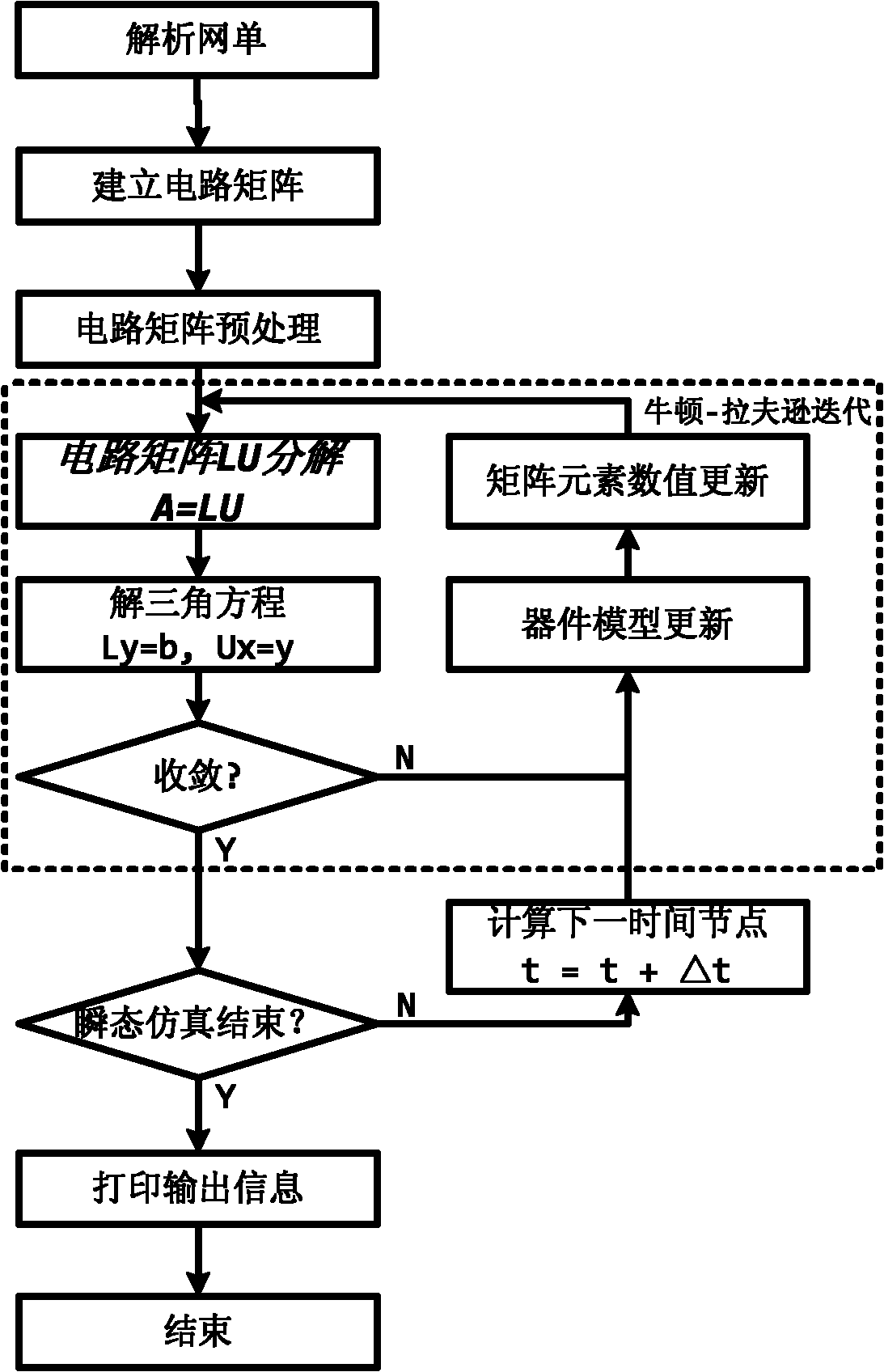

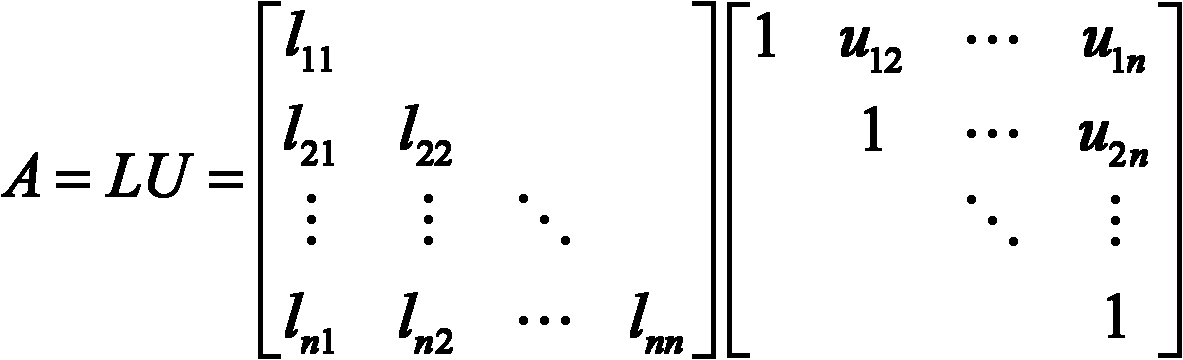

[0031] The LU decomposition method for reducing the overall complexity of circuit simulation proposed by the present invention is described as follows in conjunction with the accompanying drawings, and its implementation steps are as follows:

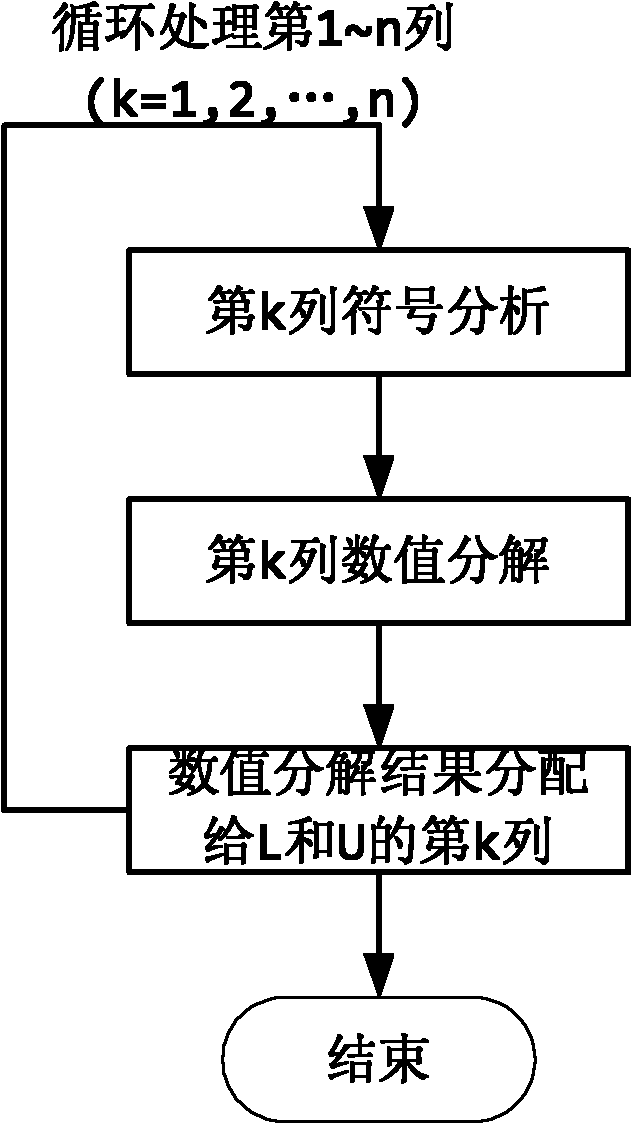

[0032] Step 1: Perform symbolic analysis on the matrix after preprocess...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More