Semiconductor structure having an air-gap region and a method of manufacturing the same

An air-gap pattern, semiconductor technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as IC failure, electronic or structural integrity problems, demarcation cracks, etc., to achieve coverage The effect of increased rate and small effective dielectric constant

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] The making and using of several illustrative embodiments are discussed in detail below. It should be appreciated, however, that the present disclosure provides many applicable concepts that can be embodied in a wide variety of specialized fields. The specific embodiments discussed are illustrative only, and do not limit the scope of the present disclosure. Alternative embodiments will also be appreciated by those skilled in the art.

[0068] As mentioned above, it is very important to reduce the parasitic capacitance in the metal interconnection. In some cases, for logic ICs using 22nm manufacturing technology, a 1% reduction in parasitic capacitance means a 0.6% increase in computing speed.

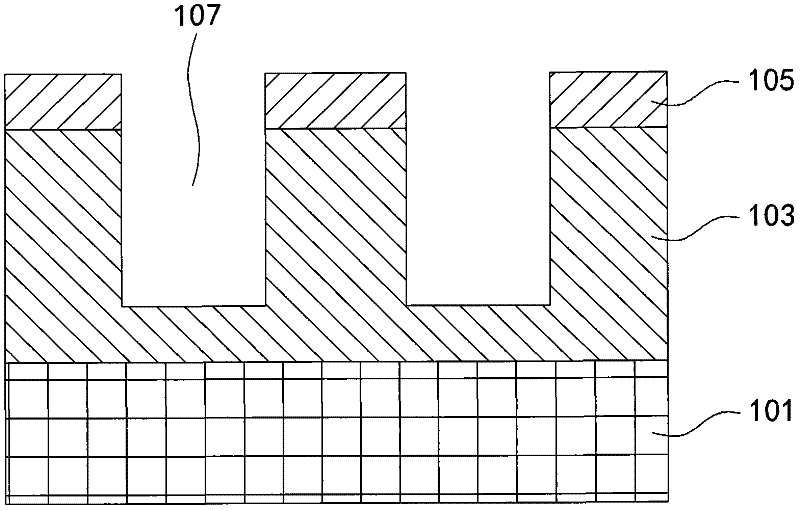

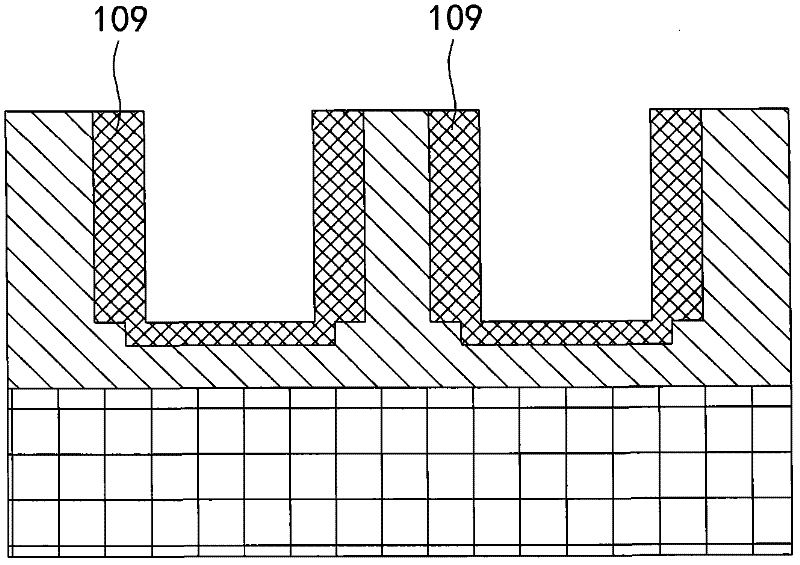

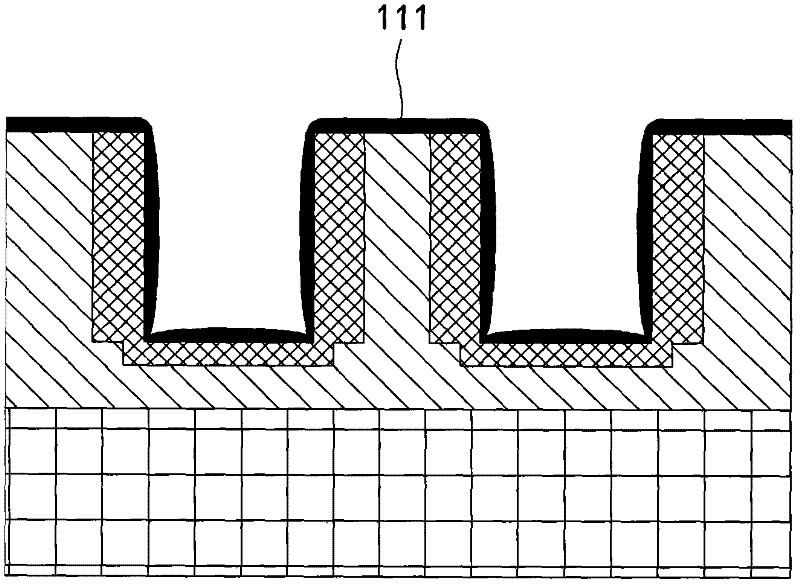

[0069] Figures 1A-1G is a cross-sectional view of a semiconductor structure illustrating a method of fabricating a semiconductor structure with an air gap region according to a conventional method.

[0070] refer to Figure 1A , a partially fabricated integrated circuit include...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com