Solution and method for displaying outline of electrostatics discharge (ESD) positive-negative (PN) junction in power metal oxide semiconductor (MOS)

A solution and profile technology, applied in the preparation of test samples, scanning probe technology, instruments, etc., can solve the problem that the ESDPN junction profile in power MOS cannot be clearly displayed, and achieve the effect of less damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

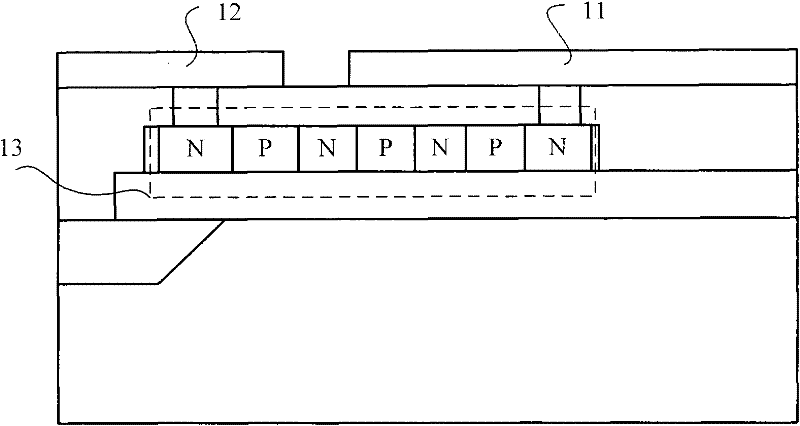

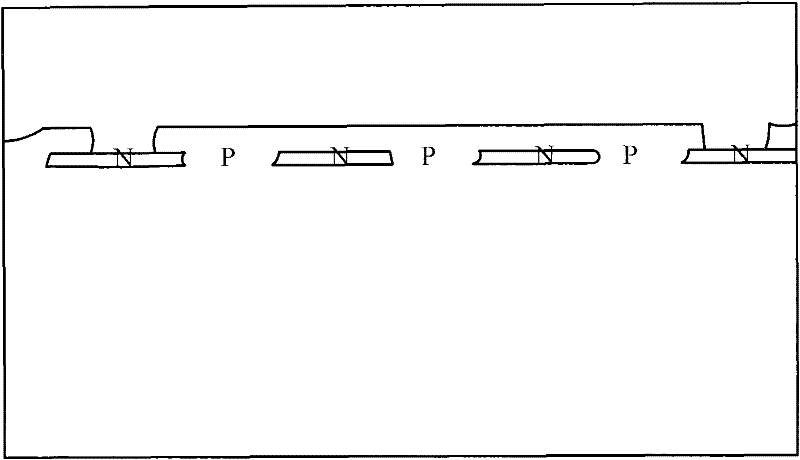

[0016] In order to make the purpose and features of the present invention more comprehensible, the specific implementation manners of the present invention will be further described below in conjunction with the accompanying drawings.

[0017] It has been mentioned in the background art that when the traditional contour visualization solution is applied to the ESDPN junction in the power MOS, the contour of the junction cannot be clearly visualized.

[0018] The solution for developing the outline of the ESD PN junction in the power MOS of the present invention includes an HF solution with a mass percent concentration of 49% and a mass percent concentration of 70% HNO 3 solution, the HF solution and HNO 3 The volume ratio of the solution ranges from 1:300 to 5:100. Among them, HNO 3 As an oxidizing agent (oxidizing agent), and HF as a complexing agent (complexing agent). The oxidizing agent reacts silicon to silicon oxide, and the complexing agent reacts with silicon oxide....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More