Semiconductor device and manufacturing method thereof

A semiconductor and device technology, which is applied to high-k/metal gate asymmetric semiconductor devices and their manufacturing fields, can solve problems such as driving current reduction, and achieve the effect of improving control ability and reducing EOT

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

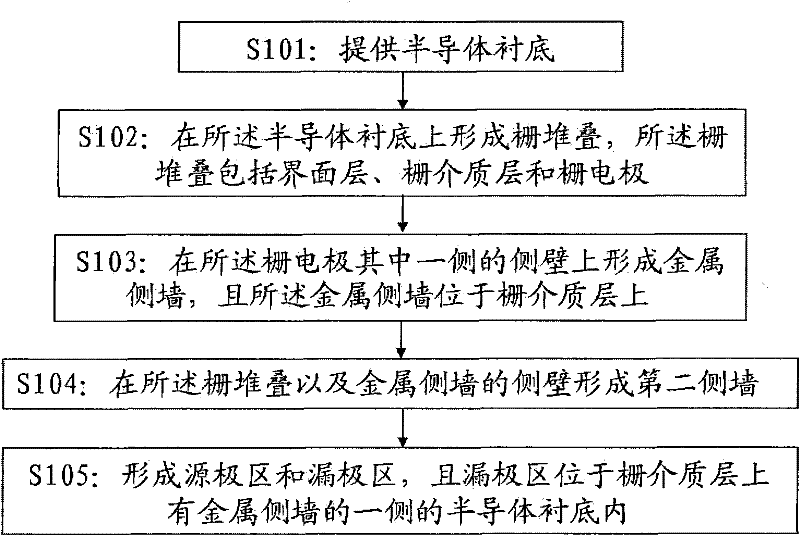

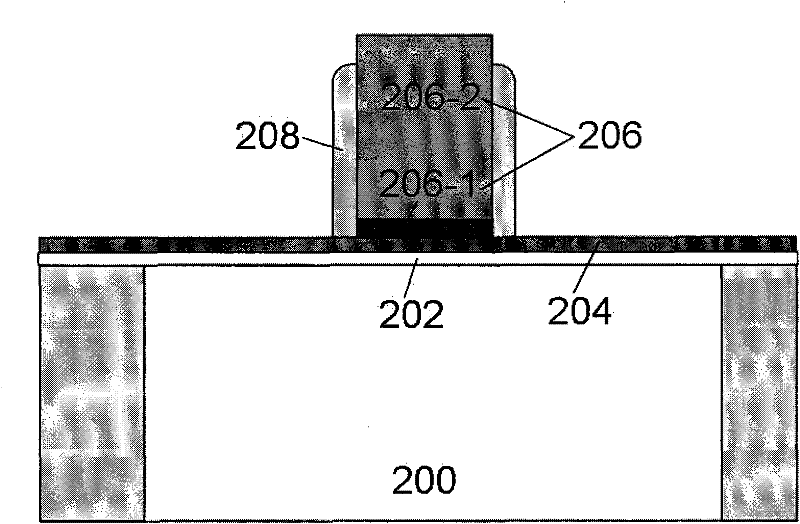

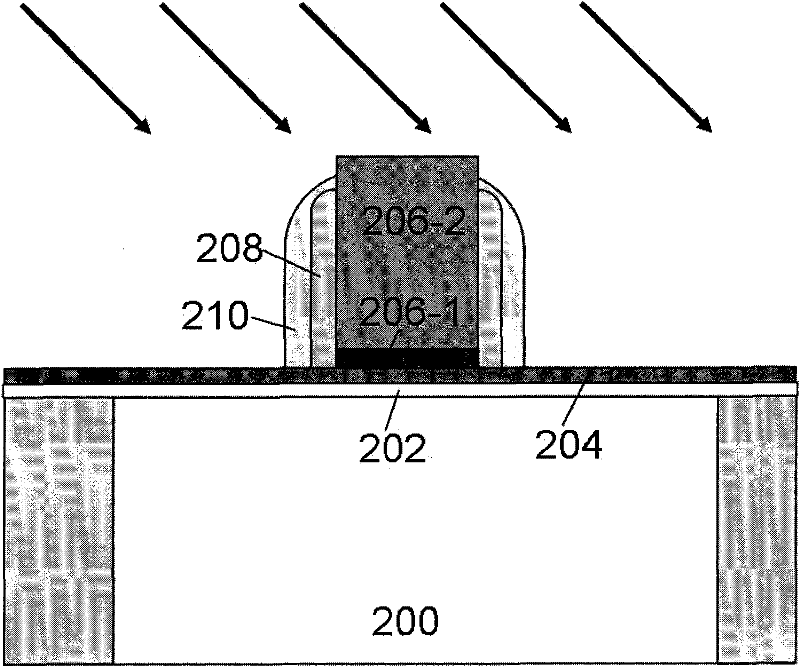

[0017] According to the first embodiment of the present invention, refer to figure 1 , figure 1 A flowchart showing a method of manufacturing a semiconductor device according to an embodiment of the present invention. In step S101, a semiconductor substrate is provided, referring to figure 2 . In the present invention, the substrate 200 includes a silicon substrate (such as a wafer) in a crystal structure, and the substrate 200 may also include other basic semiconductors or compound semiconductors, such as Ge, GeSi, GaAs, InP, SiC, or diamond. The substrate 200 may include various doping configurations according to design requirements known in the art (eg, p-type substrate or n-type substrate). Further, optionally, the substrate 200 may include epitaxial layers, may be altered by stress to enhance performance, and may include a silicon-on-insulator (SOI) structure.

[0018] In steps S102 and S103, a gate stack 300 is formed on the semiconductor substrate 200, the gate sta...

no. 2 example

[0029] Only the aspects of the second embodiment that differs from the first embodiment will be described below. Parts not described should be considered to be performed using the same steps, methods or processes as those in the first embodiment, so details will not be repeated here.

[0030] According to the second embodiment of the present invention, refer to Figure 10 , Figure 10 A flow chart of a method for manufacturing a common-source semiconductor device according to an embodiment of the present invention is shown. In step S202, the interface layer 202, the gate dielectric layer 204, the first gate layer 206-1, and the sacrificial layer 230 are sequentially formed on the semiconductor substrate 200, and the sacrificial layer 230 is photolithographically etched. Figure 12 .

[0031] Specifically, firstly, the interface layer 202, the gate dielectric layer 204, the first gate layer 206-1, the sacrificial layer 230, the first stop layer 232, and the second stop layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More