Method for analyzing and checking local pattern density of chip

A technology of pattern density and inspection method, applied in the field of pattern density analysis and inspection, can solve problems such as manual screening, false alarms, and inability to achieve inspection results, and achieve the effect of improving inspection capabilities and avoiding false alarms.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

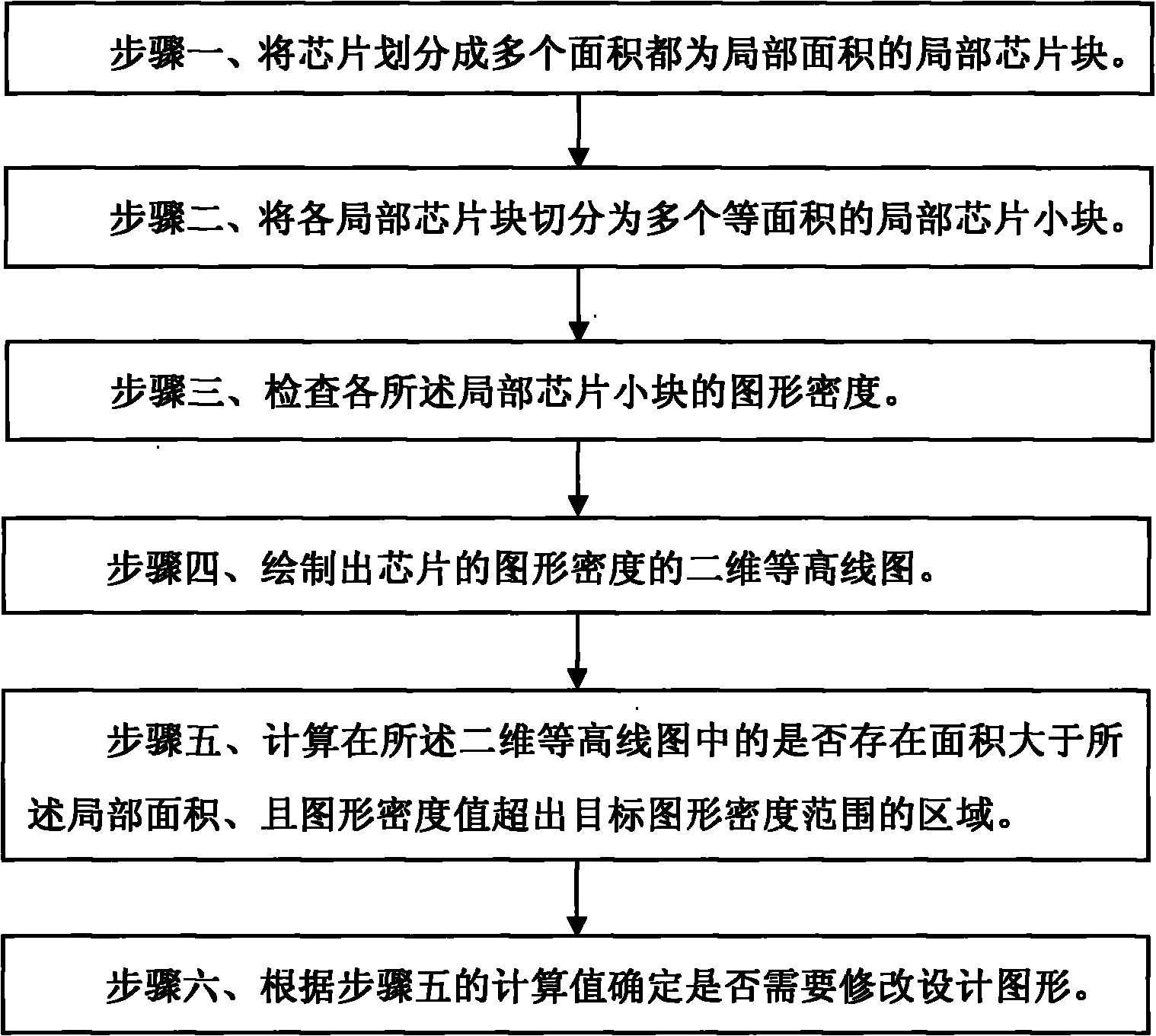

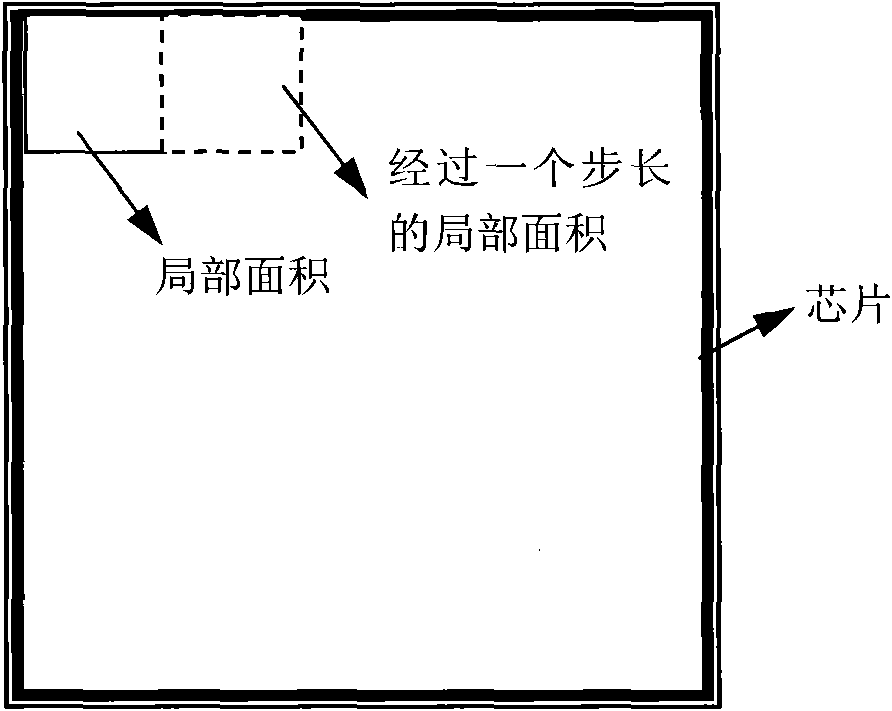

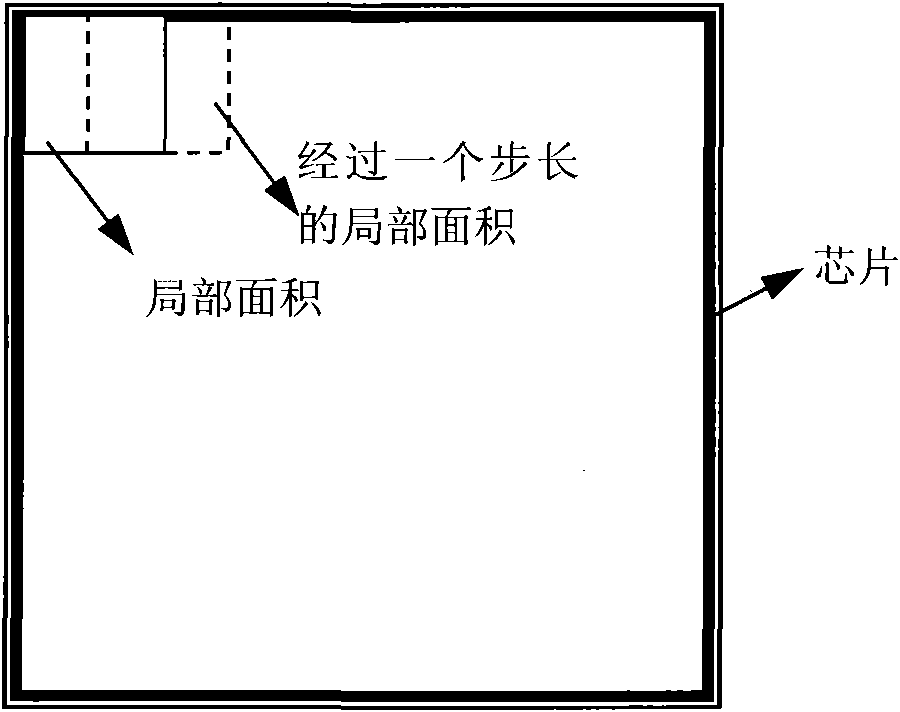

[0023] An embodiment of the present invention is listed below and the advantages of the present invention are described in combination with the prior art. For a chip that requires measurement, the chip is divided into a plurality of rectangular local chip blocks according to the size of a local area, and it is assumed that the target pattern density range of the local chip blocks with a local area size of this type of chip is <= 30%. In the embodiment of the present invention, the chip is divided into 12 identical local chip blocks in 3 equal parts in the X direction and 4 equal parts in the Y direction according to the size of the local area.

[0024] One, adopt the local pattern density inspection method of prior art chip to check a pair of described chip, obtain the data as described in table 1, can find out that the pattern density of 12 each described local chip block has been checked altogether, and all The pattern densities of the local chip blocks are all less than 30...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More