A Transient Voltage Suppressor Based on Zener Diode

A transient voltage suppression, Zener diode technology, applied in the direction of electric solid devices, circuits, electrical components, etc., can solve the problems of loss of ESD protection performance, slow data transmission speed, affecting signal integrity, etc., to achieve short response time , The effect of reducing parasitic capacitance and high surge absorption capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to describe the present invention more specifically, the technical solution of the present invention and its related principles and manufacturing process will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

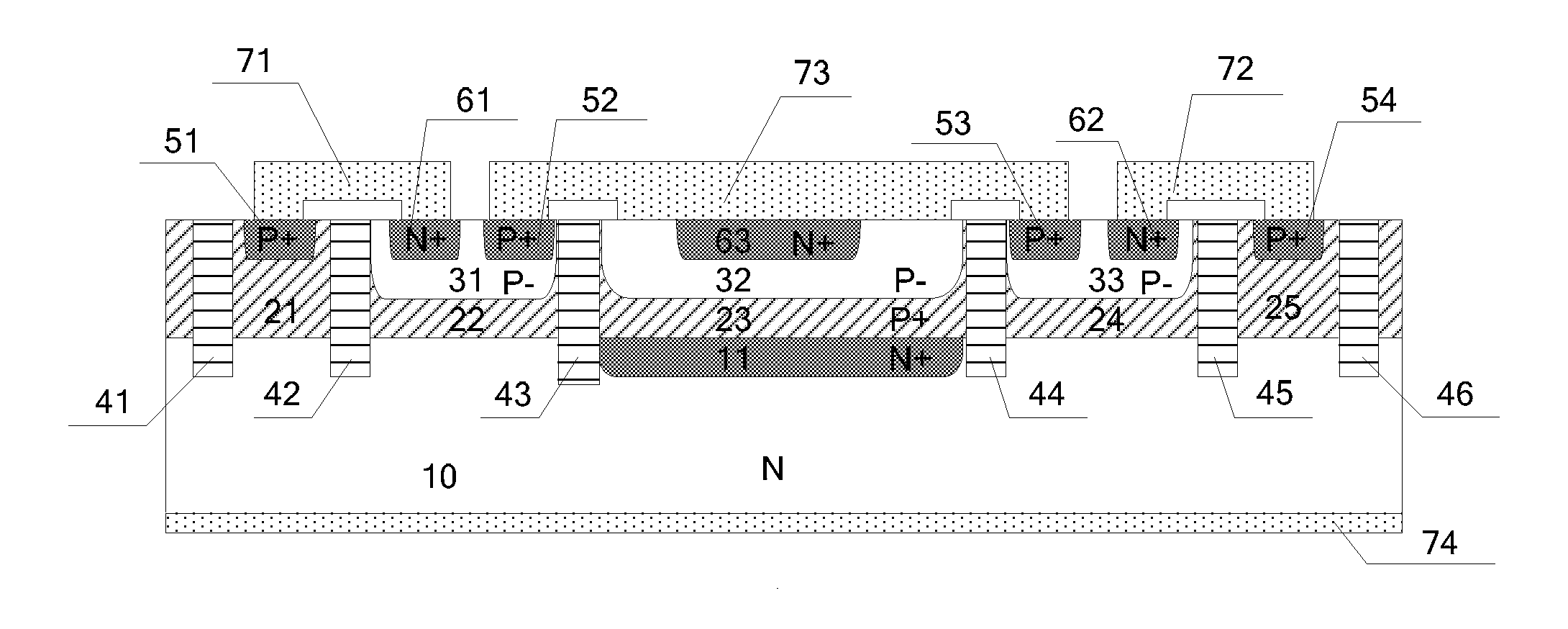

[0030] like figure 1 As shown, a transient voltage suppressor based on a zener diode includes an N substrate layer 10, and the N substrate layer 10 is sequentially provided with a first isolation groove 41, a first P+ epitaxial region 21, and a second isolation groove from left to right. Groove 42, second P+ epitaxial region 22, third isolation trench 43, N+ buried layer 11, fourth isolation trench 44, fourth P+ epitaxial region 24, fifth isolation trench 45, fifth P+ epitaxial region 25, sixth isolation slot 46;

[0031] The second P+ epitaxial region 22 and the fourth P+ epitaxial region 24 are respectively provided with a first P-well 31 and a third P-well 33; the N+ buried layer 11 is sequentially pro...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More