Method for fabricating metal oxide semiconductor device with epitaxially grown stress-induced source and drain regions

A stress-induced, semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to solve problems such as increased possibility of channel contamination, recession, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] The following detailed description of the invention is merely exemplary in nature and is not intended to limit the invention or the application and uses of the invention. Furthermore, there is no intention to be bound by any theory presented in the preceding background or the following embodiments.

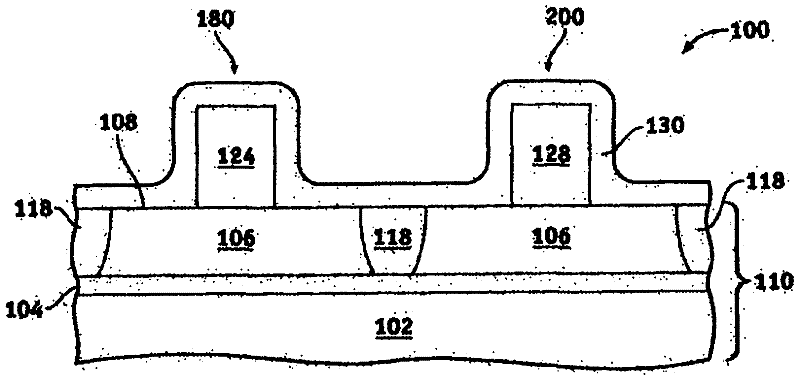

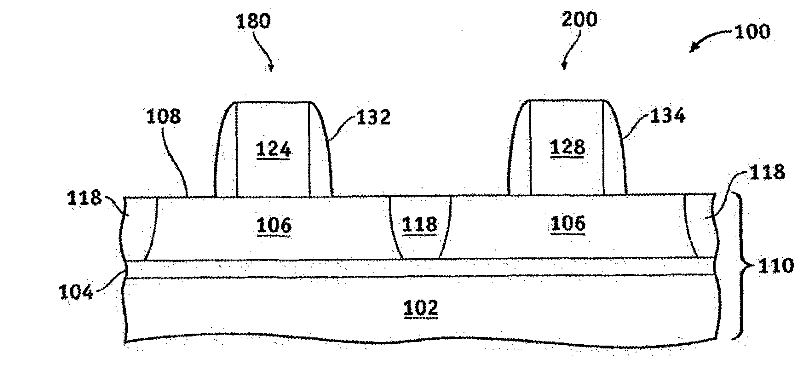

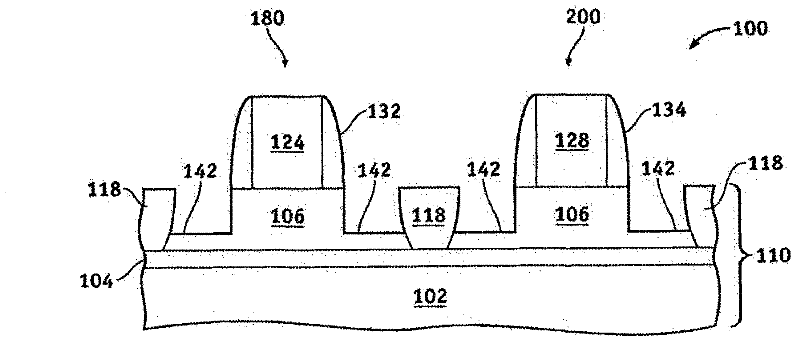

[0010] Historically, epitaxially forming regions for source and drain regions of NFET and PFET devices involved separate sets of process steps for each device type. After forming the gate stacks in both the PFET and NFET regions, the first set of process steps are then used to form the source and drain of one of these device types. In this sequence, a second set of similar steps is followed to form the source and drain of another device type. Each set of process steps typically includes: 1) depositing a blanket dielectric layer in both the PFET and NFET regions, 2) lithographically forming a soft mask to cover the first ( PFET or NFET region), 3) anisotropically etch the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com