Pipeline a/d converter and its digital correction method with overflow flag

A pipeline and converter technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve the problem that A/D conversion samples cannot be digitally corrected, multi-time, etc., so as to reduce the correction time, reduce the number, and improve the correction accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] In order to describe the present invention more specifically, the pipeline A / D converter and its digital correction method of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0050] Such as Figure 11 As shown, a 14-bit pipeline A / D converter includes 12 1.5-bit pipeline sub-levels and a 2.5-bit Flash A / D converter.

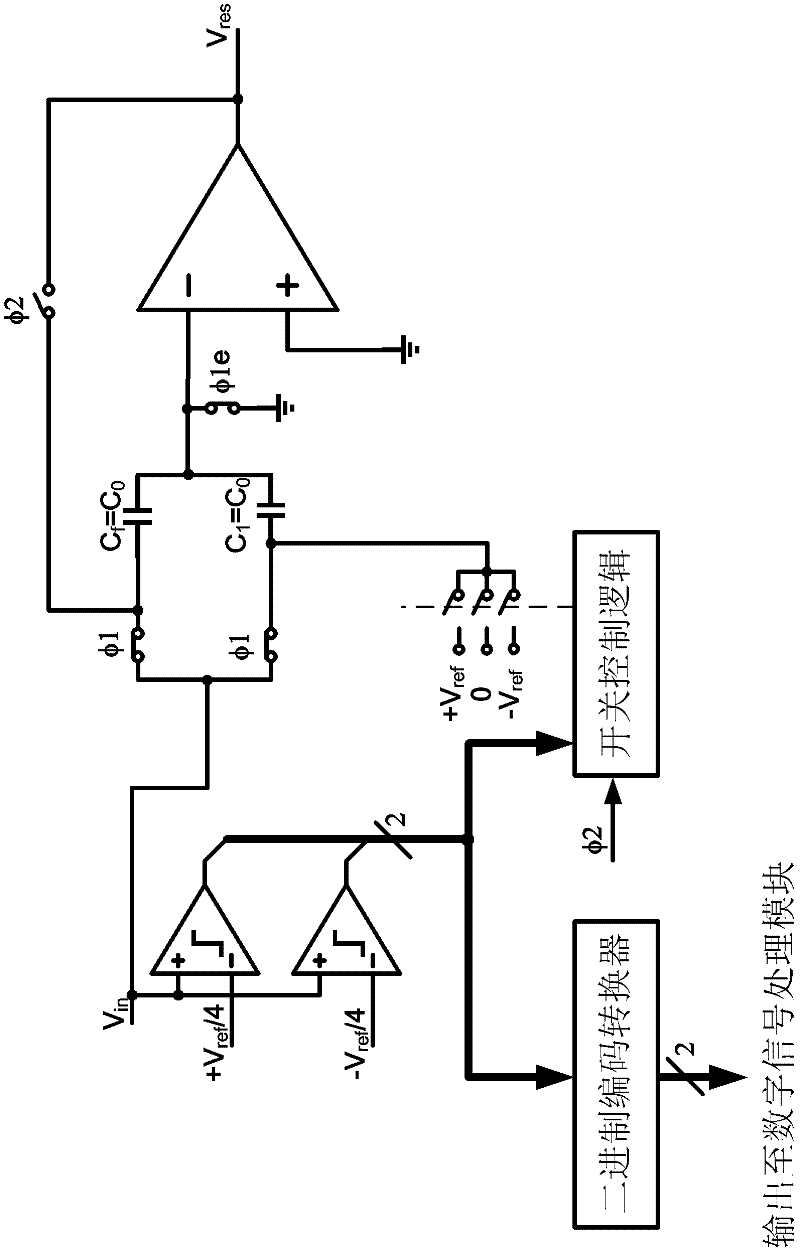

[0051] Such as Figure 4 As shown, the 1.5-bit pipeline sub-stage consists of an operational amplifier, a binary code converter, a switch control logic, a ground switch, a feedback switch, a feedback capacitor, an idle switch, an idle capacitor, a sampling capacitor, two Sampling switch, two three-selection switches and two comparators; among them, the non-inverting input terminal of the operational amplifier is grounded, the inverting input terminal of the operational amplifier is connected to one terminal of the grounding switch, and the feedback capacitor C f One end of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More