Memory circuit and method for reading data by applying same

A memory circuit and circuit technology, applied in the field of memory, can solve the problems of difficulty in guaranteeing the yield rate of memory circuits, errors in the data reading and writing process, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0091] In order to make the above objects, features and advantages of the present invention more clearly understood, the present invention will be described in further detail below with reference to the accompanying drawings and specific embodiments.

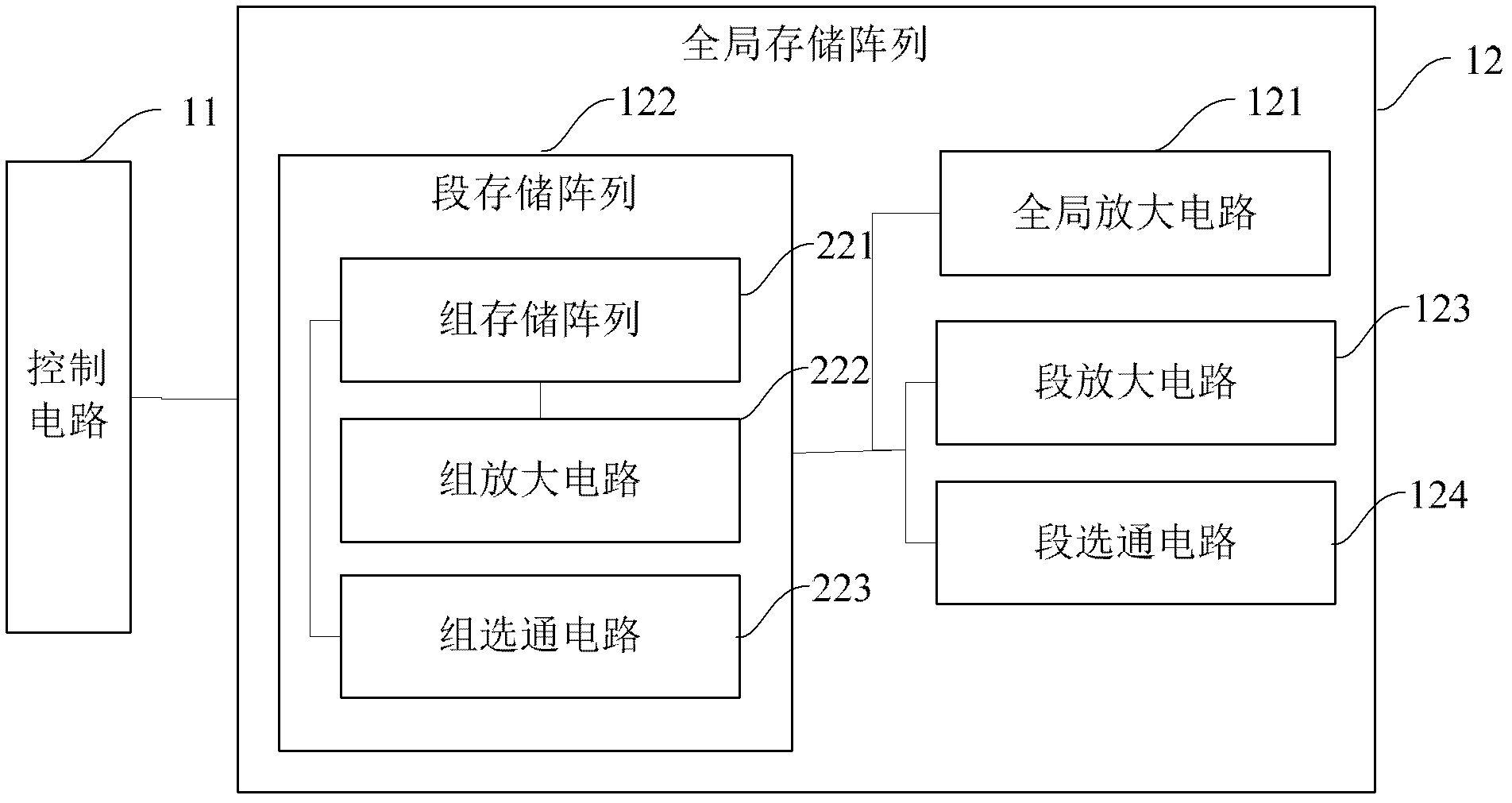

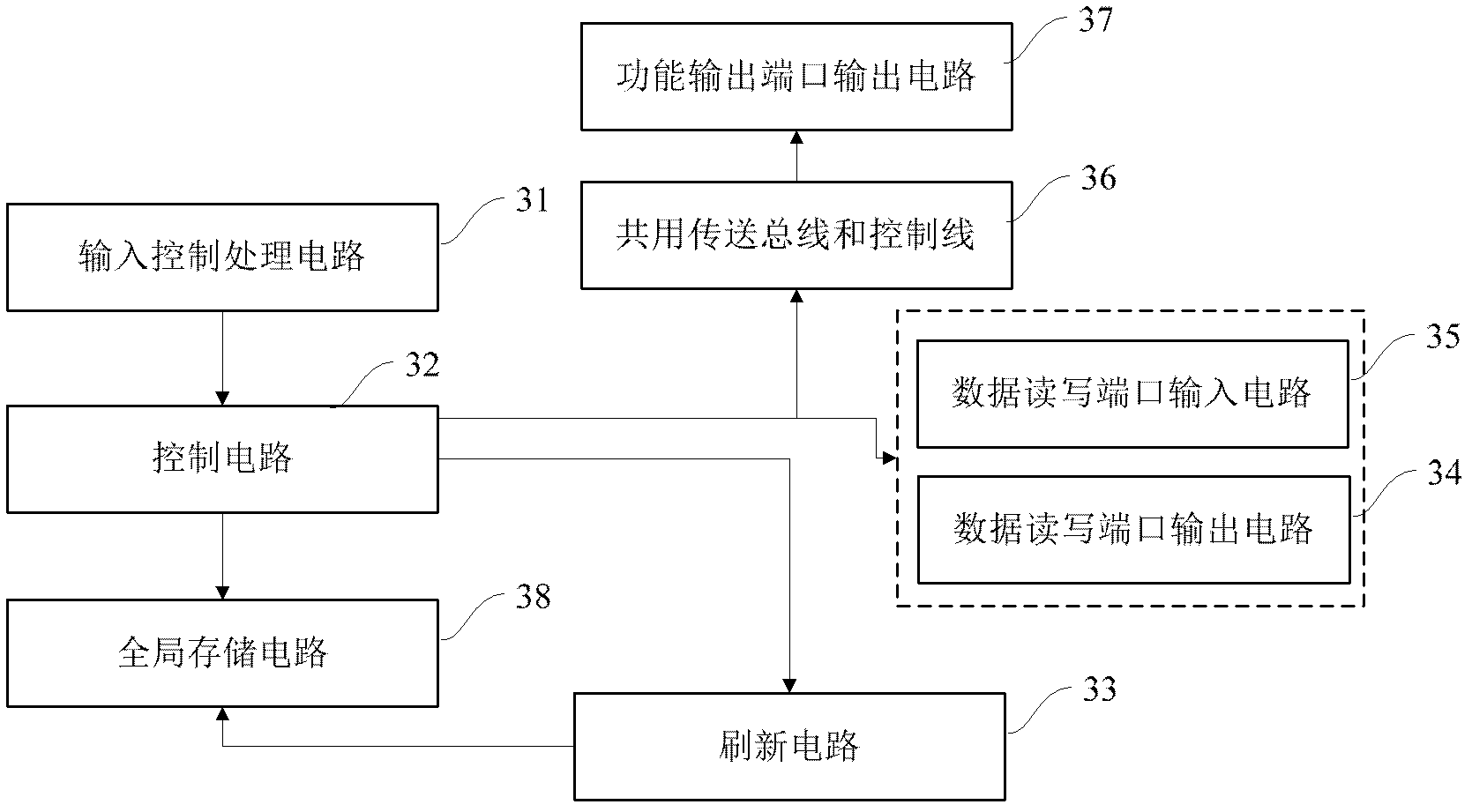

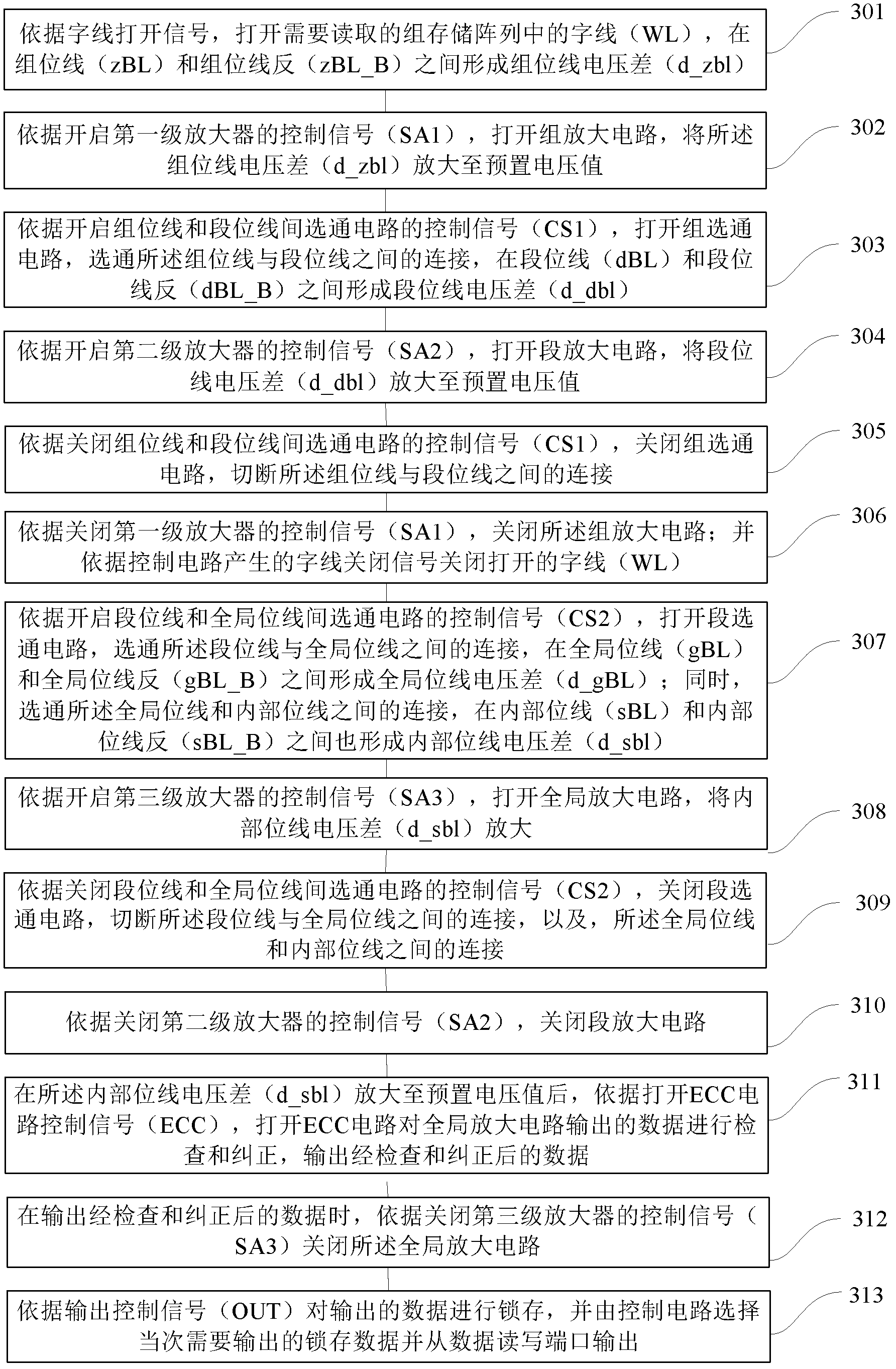

[0092] One of the core concepts of the embodiments of the present invention is to design a control circuit with an ECC circuit and a multi-level segmented global memory array in the memory circuit. Specifically, the global storage array is divided into a group storage array and a segment storage array. The segment storage array includes a group storage array and a group amplification gate circuit; the global storage array includes a segment storage array, a segment amplification gate circuit and a global amplification circuit. . The global amplification circuit is connected with the segment amplification gate circuit through the global bit line, the segment amplification gate circuit is connected with the group amplification gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More