Digital-analog hybrid mode clock duty ratio calibration circuit

A digital-analog hybrid and calibration circuit technology, which is applied in the direction of analog/digital conversion calibration/testing, can solve the problems of discrete calibration accuracy and inability to obtain calibration results, etc., achieve continuous adjustable delay time, and take into account adjustment accuracy and phase resolution rate, the effect of overcoming discreteness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Embodiments of the present invention will be described below with reference to the drawings.

[0031] The purpose of the present invention is to propose a circuit structure capable of performing duty cycle calibration in a wider frequency and duty cycle range under a specified process, aiming at the shortcomings of existing digital duty cycle calibration circuits. In addition, the proposed scheme also has a good suppression of process mismatch and other phenomena.

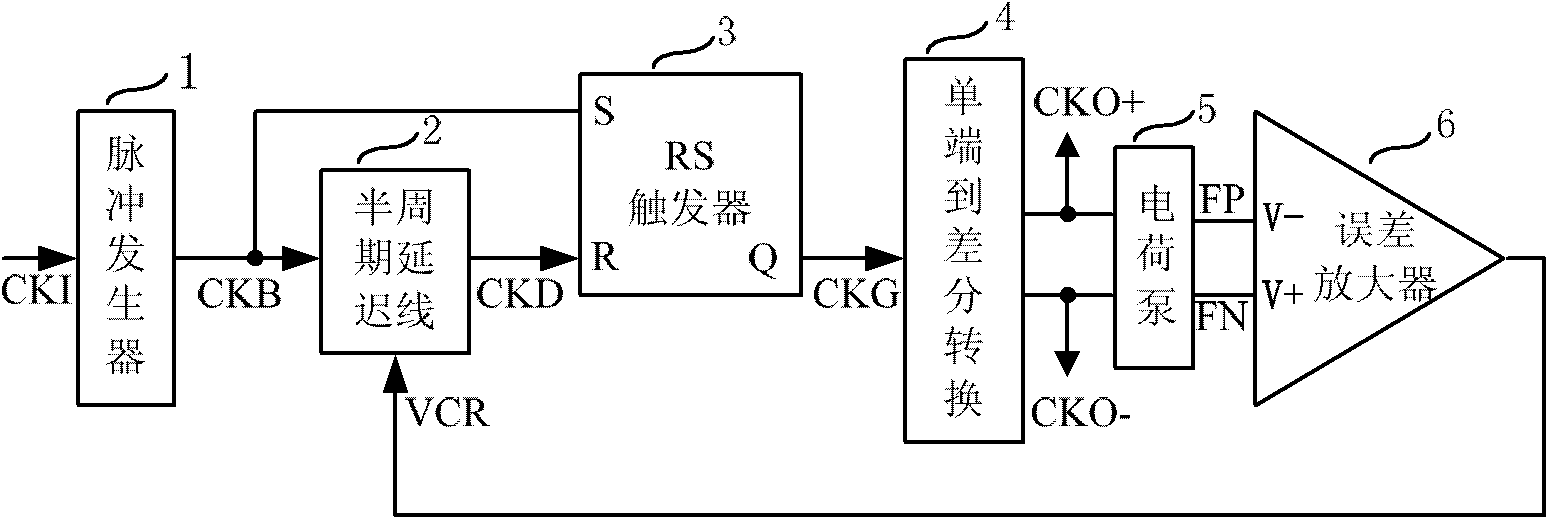

[0032] The digital-analog mixed mode clock duty cycle calibration circuit of the present invention includes a pulse generator PG 1, a half-period delay line HCDL 2, an RS flip-flop 3, a single-end to differential conversion circuit STD 4, and a digital-analog mixed charge Pump CCP 5, Error Amplifier 6.

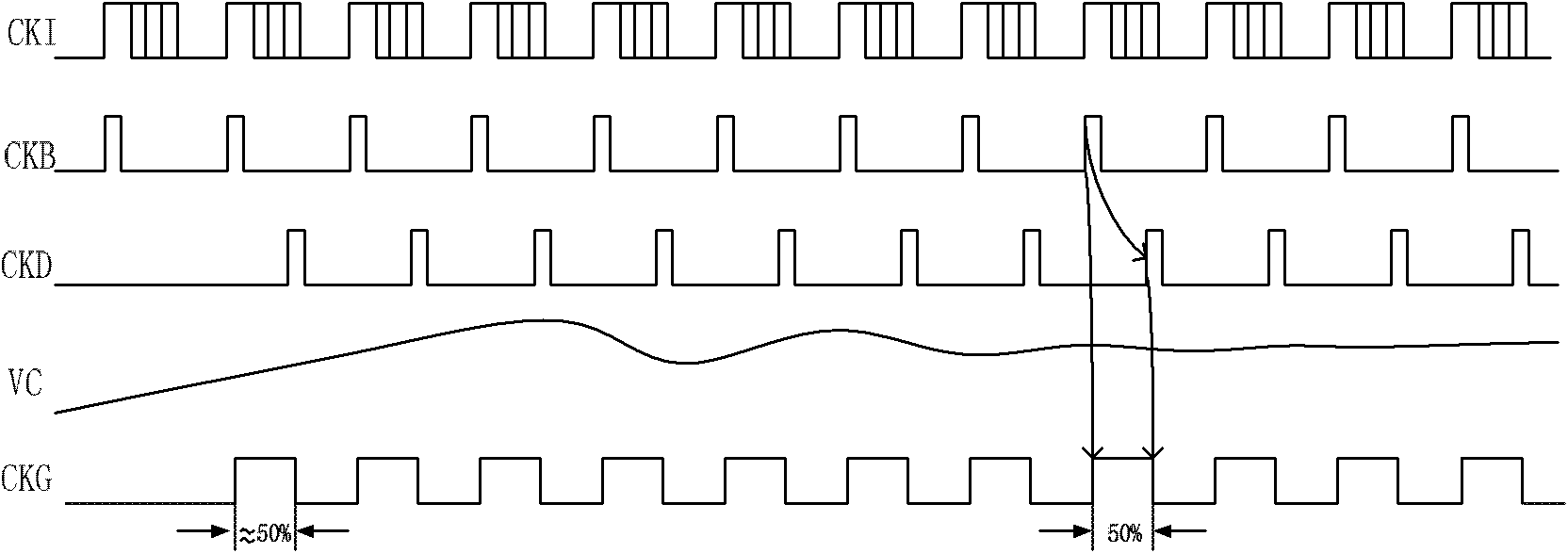

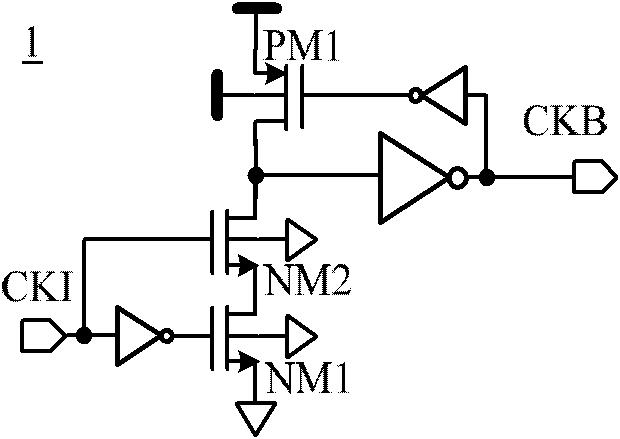

[0033]In this circuit, the input terminal of the pulse generator 1 receives the calibrated original input clock signal CKI; the output signal of the pulse generator 1 is the buffered narrow pulse CKB with a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More