High-strength chip packaging structure

A chip packaging structure and high-strength technology, applied in electrical components, electrical solid devices, circuits, etc., can solve problems such as affecting the normal operation of the chip, reducing the service life of the chip, and lacking the stability of the chip packaging structure. Heat dissipation performance, reasonable effect of package structure design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

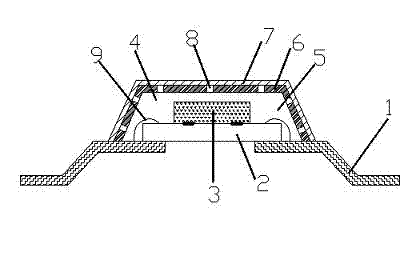

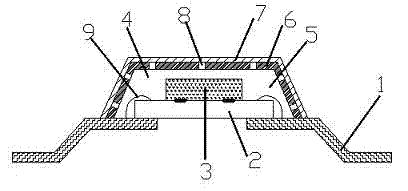

[0018] figure 1 It is a structural schematic diagram of a high-strength chip packaging structure in an embodiment of the present invention; the high-strength chip packaging structure mainly includes metal pins 1, a substrate 2, a chip 3 and a package body 4, and it is characterized in that the package body 4 adopts a multilayer Structural design, from the inside to the outside is composed of a sealant layer 5, a metal layer 6 and a heat dissipation layer 7, the metal layer 6 adopts a metal spraying process, and is formed on the surface of the sealant layer 5. The heat dissipation layer 7 is pasted On the outside of the metal layer 6, it plays the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More