Layout structure of power metal oxide semi-field effect transistor (power MOSFET)

A metal-oxygen semi-field, layout structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of poor transistor layout integration, large layout area, and increased manufacturing costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

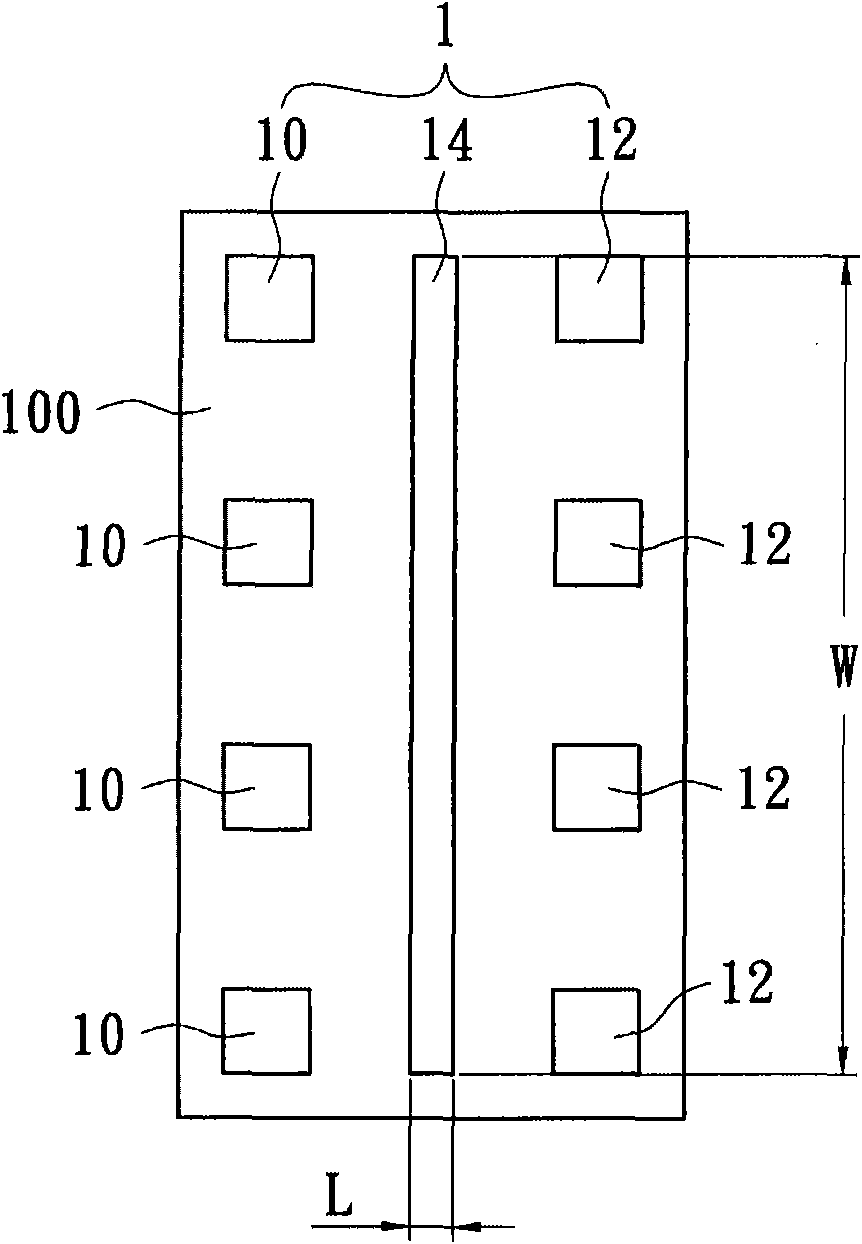

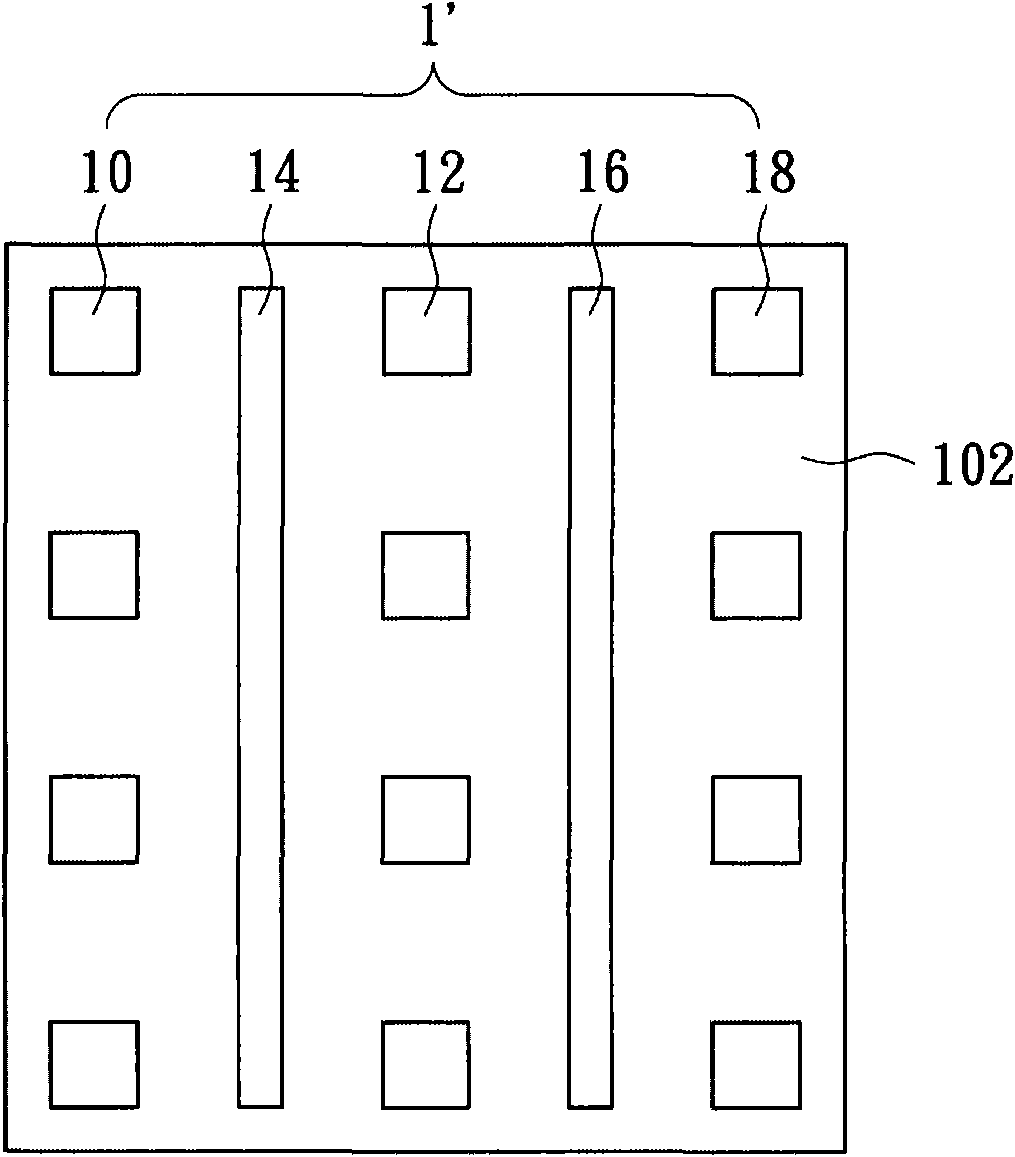

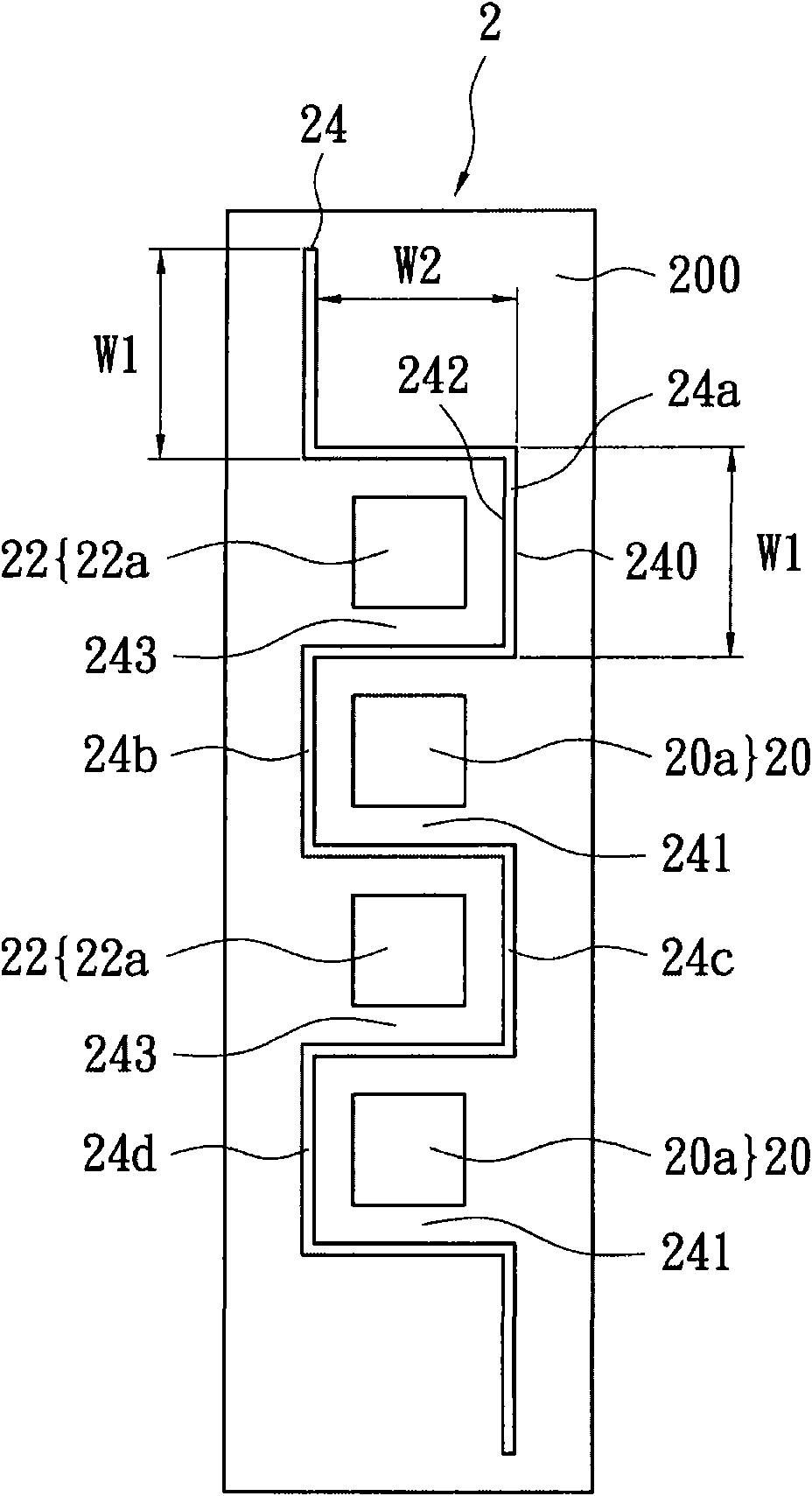

[0045] In order to effectively solve the problem of increased manufacturing cost caused by relatively large layout area required for traditional power metal oxide semiconductor field effect transistors in large sizes. The present invention provides a layout structure of a power metal-oxide-semiconductor field-effect transistor, in which the grid structure in a power metal-oxide-semiconductor field-effect transistor is laid out in a meandering form (such as a zigzag, an S-shape, a square waveform, etc.) on the substrate. With the aid of a snake-like layout structure, the power MOS field effect transistor of the present invention can increase the channel effective width (Channel Width) under the same layout area compared with conventional power MOS field effect transistors.

[0046] According to the formula (1), the output current I of the power MOSFET D It is directly proportional to the effective channel width W, therefore, under the same layout area, the output current capab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More