LDPC (low density parity check) decoder and decoding method based on layer decoding processing

A decoder and decoding technology, which are applied in the field of LDPC decoders and decoding based on layer decoding processing, can solve problems such as difficulty in generalization, consumption of hardware resources and interconnection complexity, and improve throughput, meet the needs of High-speed data processing requirements, the effect of reducing the clock cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

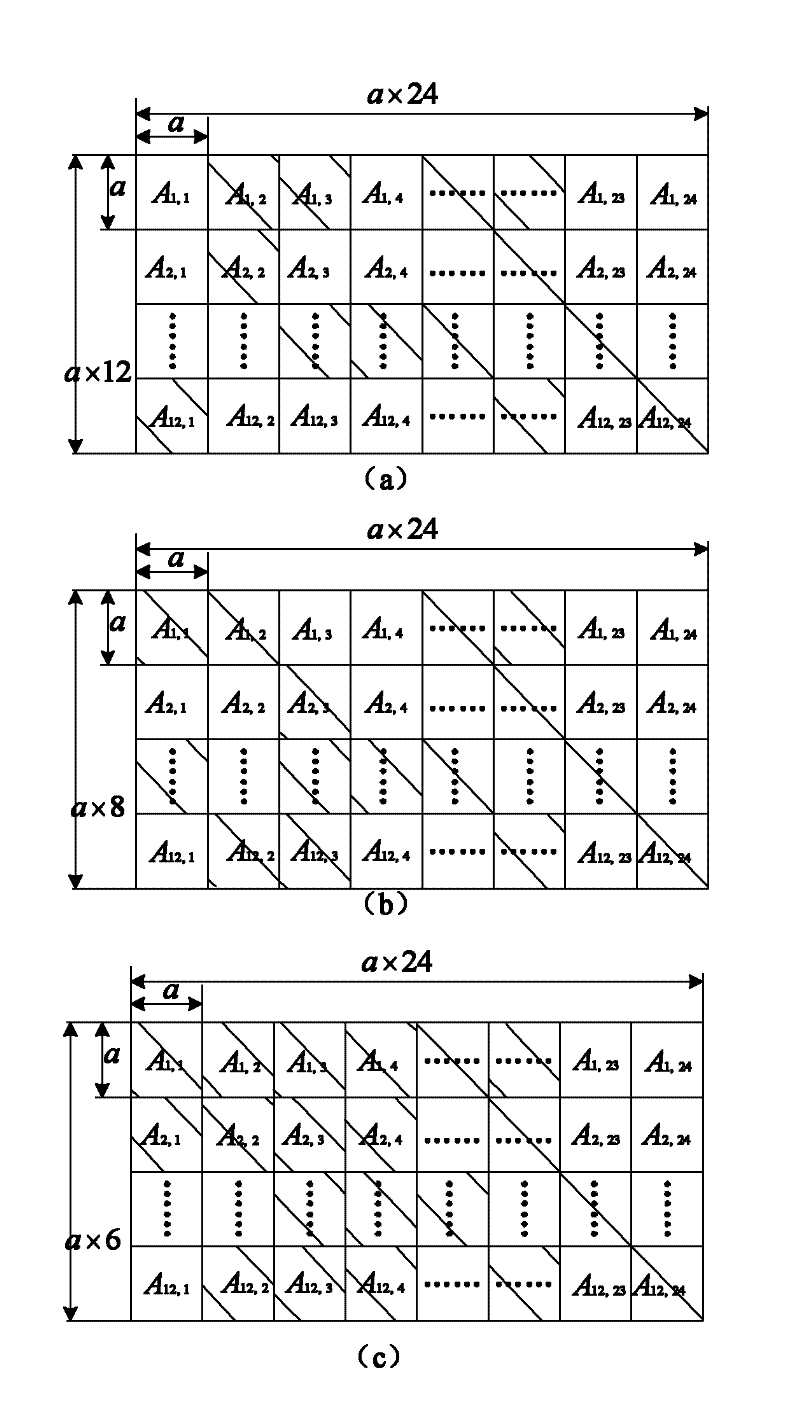

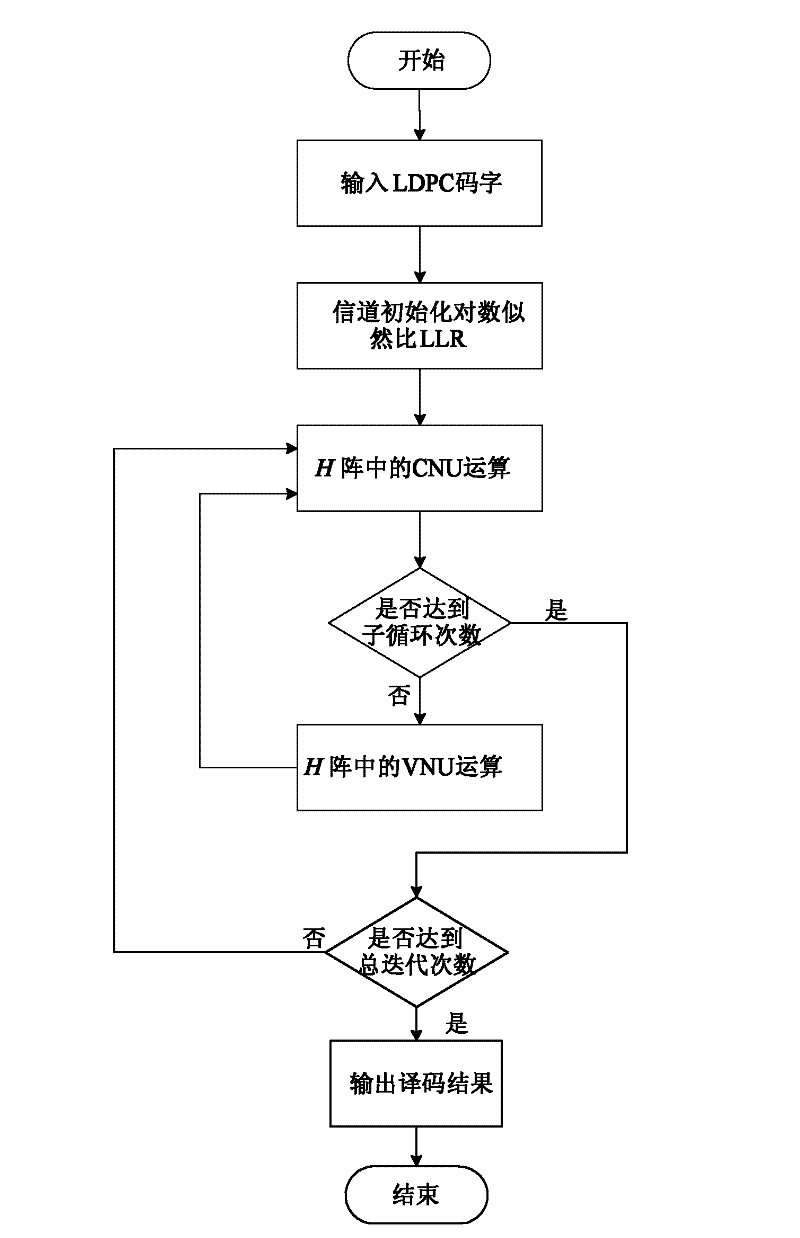

[0087] This embodiment is used figure 2 Shown H 0 The decoding of the 1 / 2 rate LDPC code corresponding to. Such as Figure 4 As shown, the decoder in this embodiment includes the following parts:

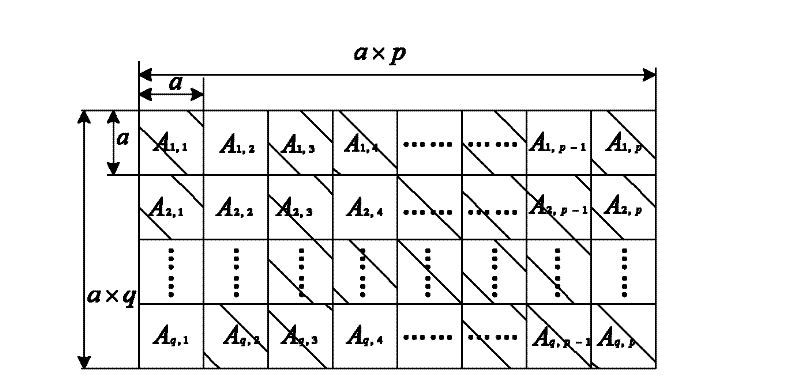

[0088] The node update processing unit CNPU set includes a total of node update processing units, which are 40_1,...40_x, 40_a. In this embodiment, the check matrix H 0 Number of row blocks q 0 Is 12, the number of columns p 0 It is 24, and the unit cyclic matrix size a is 96, so the number of CNPUs is equal to the unit cyclic matrix size a, and each CNPU corresponds to a row and column equation in the check matrix. CNPU completes the update operation of the check node information and variable node information corresponding to the Tanner graph in the iterative process; the check node update operation unit CNU set is 50, including a node update processing units, respectively 50_1, .. ....50_x, 50_a; check node storage unit, respectively 10_1,......10_x, 10_a; variable node storage uni...

Embodiment 2

[0123] This embodiment is used figure 2 Shown H 0 , H 1 , H 2 Decoding of LDPC codes of the corresponding mixed code rate. Where H 0 Is the check matrix corresponding to the code rate 1 / 2, H 1 Is the check matrix corresponding to the code rate of 2 / 3, H 2 It is a check matrix with a corresponding code rate of 3 / 4. Compared with Embodiment 1, the configuration process of addressing and offset parameter memory is different in this embodiment only in the initialization phase, which is described as follows: In this embodiment, the initialization configuration phase needs to be configured according to different code rates. Different control parameters. For different code rates, different parameter storage tables can be used, such as Table 1 for storing H 0 Corresponding control parameters, Table 2 is used to store H 1 Corresponding control parameters, Table 3 is used to store H 2 The corresponding control parameter. The storage mode of each storage table is still in the order of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More