Semiconductor device and method of producing same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as circuit malfunctions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

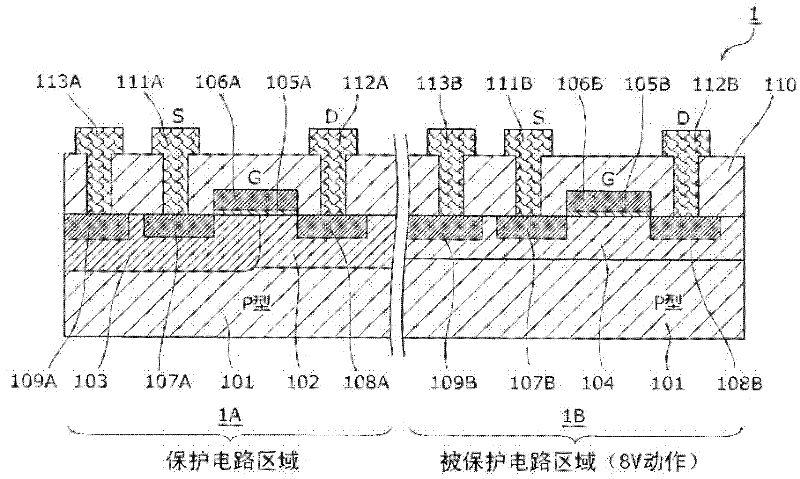

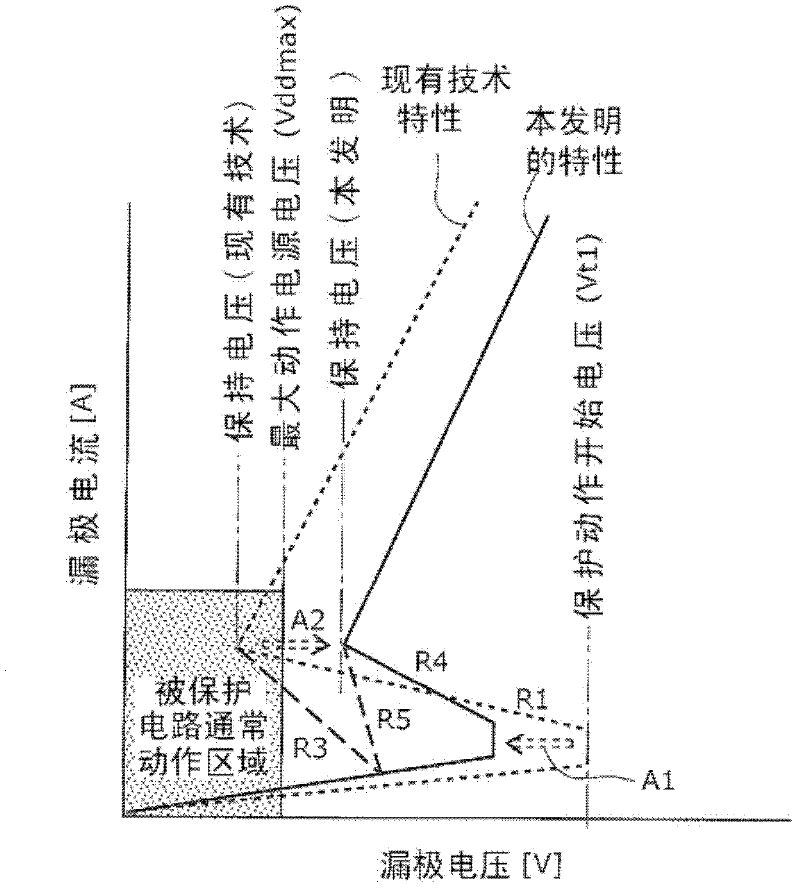

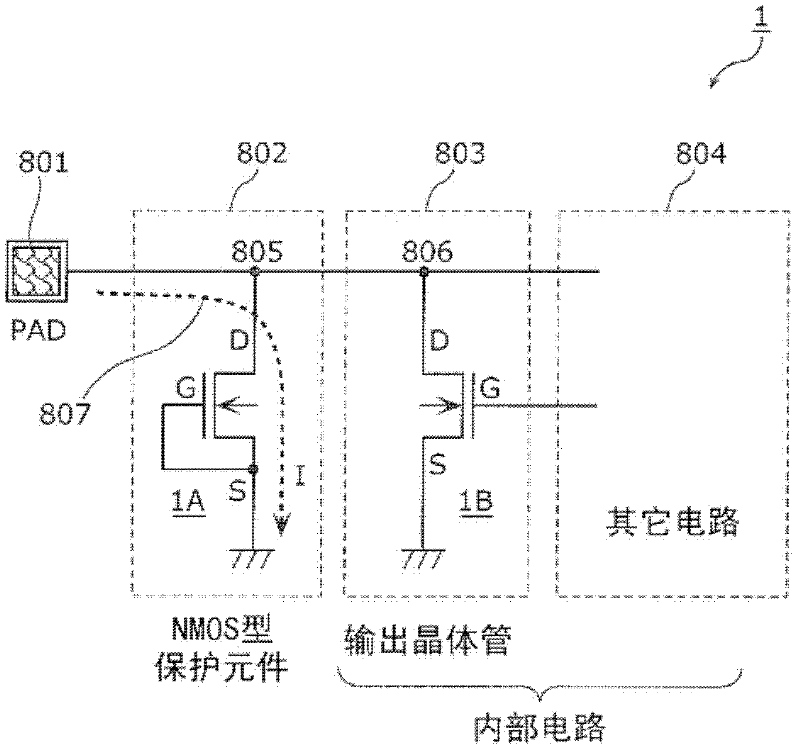

[0063] The semiconductor device of this embodiment has an internal circuit and a protection circuit using the same P-type semiconductor substrate. The above protection circuit has: a grounded first gate electrode, a grounded first source electrode, and a first drain electrode formed on the P-type semiconductor substrate; An N-type first diffusion region where the electrodes are connected; and a second diffusion region, which covers the first diffusion region in the P-type semiconductor substrate and is formed from below the first diffusion region to at least below the first gate electrode. part, and the P-type concentration is higher than the basic region of the P-type semiconductor substrate, and is grounded to the same level as the first diffusion region. And, the above-mentioned internal circuit has: a second gate electrode, a second source electrode, and a second drain electrode formed on the P-type semiconductor substrate; an N-type third diffusion region; and a P-type f...

Embodiment approach 2

[0117] Figure 5 It is a cross-sectional view showing the structure of the main part of the ESD protection element and the protected element included in the semiconductor device according to Embodiment 2 of the present invention. The semiconductor device 13 shown in this figure has an ESD protection element 13A and a protected element 1B. The ESD protection element 13A and the protected element 1B are formed on a continuous P-type Si substrate 101 . The semiconductor device 13 of this embodiment and the figure 1 Compared with the semiconductor device 1 of Embodiment 1 described in , only the structure of the diffusion region of the ESD protection element is different. Below, omit the description and figure 1 The same content as the ESD protection element 1A described in , only the differences are described.

[0118] In this embodiment, if Figure 5 As shown, the P-type diffusion region 162 in the P-type Si substrate 101 from the source electrode 111A to the drain electr...

Embodiment approach 3

[0134] Figure 7 It is a cross-sectional view showing the structure of the main part of the ESD protection element and the protected element included in the semiconductor device according to Embodiment 3 of the present invention. The semiconductor device 2 shown in this figure has an ESD protection element 2A and a protected element 2B. The ESD protection element 2A and the protected element 2B are formed on a continuous P-type Si substrate 101 . The semiconductor device 2 of this embodiment and the figure 1 Compared with the semiconductor device 1 of Embodiment 1 described in , only the structures of the diffusion regions of the ESD protection element and the protected element are different. Below, omit the description and figure 1 The same content as the ESD protection element 1A described in , only the differences are described.

[0135] The protected element 2B of this embodiment is used in a circuit operating at a medium voltage, and is composed of, for example, an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More