Testing system and testing method for optoelectronic integrated circuit chip

A technology of integrated circuits and test systems, applied in the field of test systems for optoelectronic integrated circuit chips, can solve the problems of unstable test and long test time, and achieve the effects of reducing test costs, shortening test time, and enhancing stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

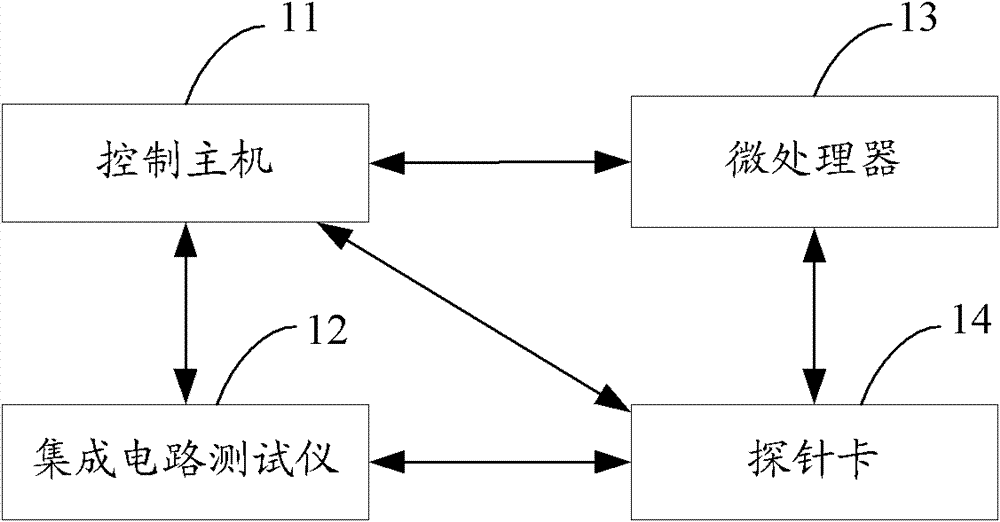

[0030] figure 1 The structure of the test system of the optoelectronic integrated circuit chip provided by the embodiment of the present invention is shown, and the details are as follows:

[0031] The test system of this optoelectronic integrated circuit comprises: control host computer 11, integrated circuit tester 12, with hardware internal integrated circuit bus 1 2 C or the microprocessor (MicroControl Unit, MCU) 13 of the system management bus SMBuS protocol module, and the probe card ProberCard 14 carrying the peripheral circuit of the chip to be tested.

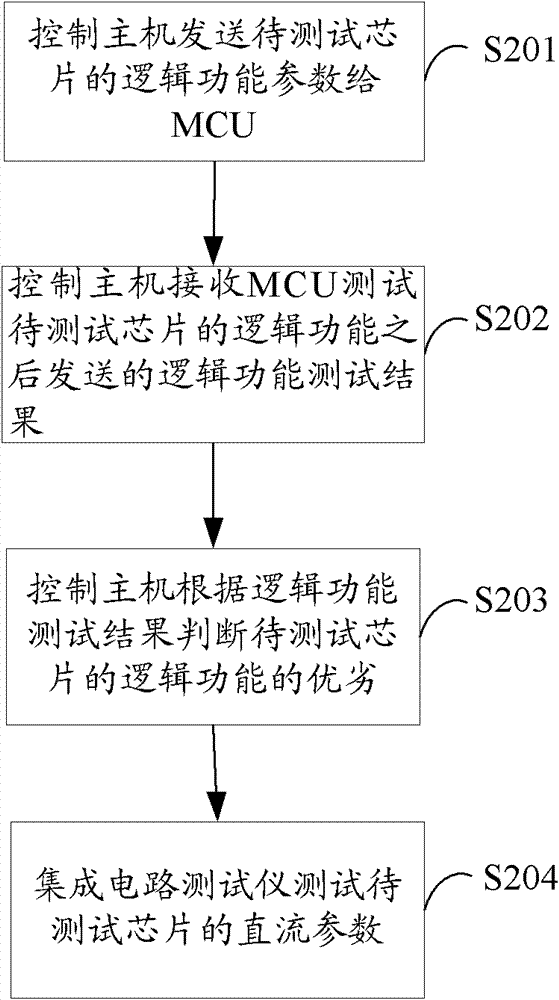

[0032] The control host 11 is connected with the integrated circuit tester 12, MCU13, and Prober Card14, and is used to send the logic function parameters of the chip to be tested to the MCU13, and the MCU13 performs relevant logic on the chip to be tested connected to it according to the received logic function parameters. Functional test, after the test is completed, the logic function test result of the chip is se...

Embodiment 2

[0038] In the embodiment of the present invention, in order to save the logic function test result of the chip to be tested received by the control host 11, or to save the judgment result after the control host 11 judges the test result, a storage device can be set in the control host 11. The unit is used to store logic function test results or judgment results.

[0039] Since the storage unit stores the logic function test result sent by the MCU or the judgment result after making a judgment on the test result, the test result or judgment result can be extracted from the control host 11 very conveniently when the above test result or judgment result is used next time.

Embodiment 3

[0041] In the embodiment of the present invention, first, the control host 11 sends the logic function parameters of the chip to be tested to the MCU 13 connected to it through the RS-232 serial port. Then, MCU13 passes through I according to the logic function parameter that receives 2 C or the SMBuS protocol function to realize the relevant logic function test of the chip to be tested, and finally, the test result information is sent to the control host 11 by way of the RS-232 serial port.

[0042] In addition, the control host 11 is connected to the Prober Card 14 through the RS-232 interface, and controls the Prober Card 14 to complete the testing process of the entire chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com