Semiconductor device

A semiconductor, conductive type technology, applied in the direction of semiconductor devices, electrical components, diodes, etc., can solve problems such as damage tolerance, reduction, and increase in hole discharge resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

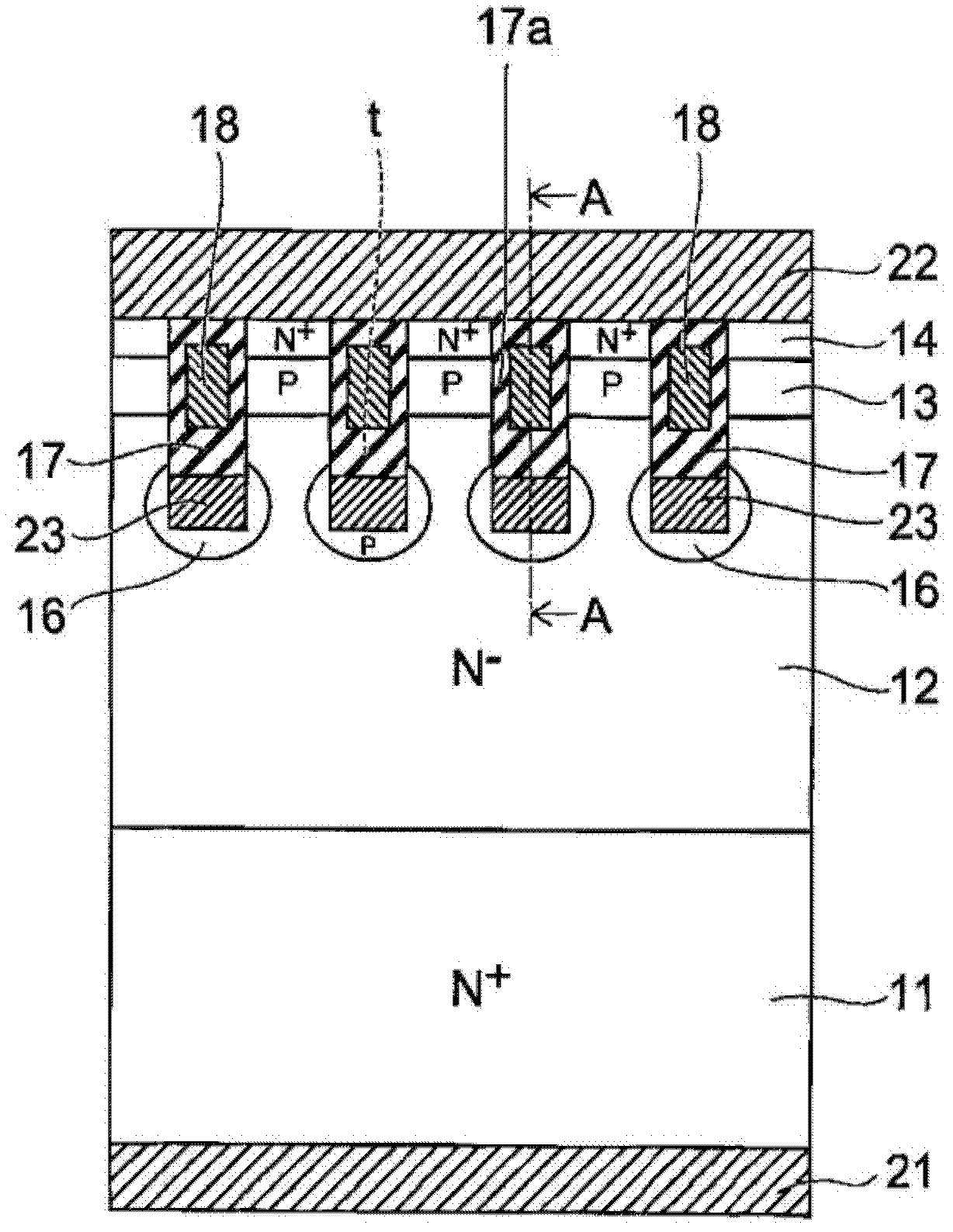

[0022] figure 1 It is a schematic cross-sectional view of the semiconductor device of the first embodiment.

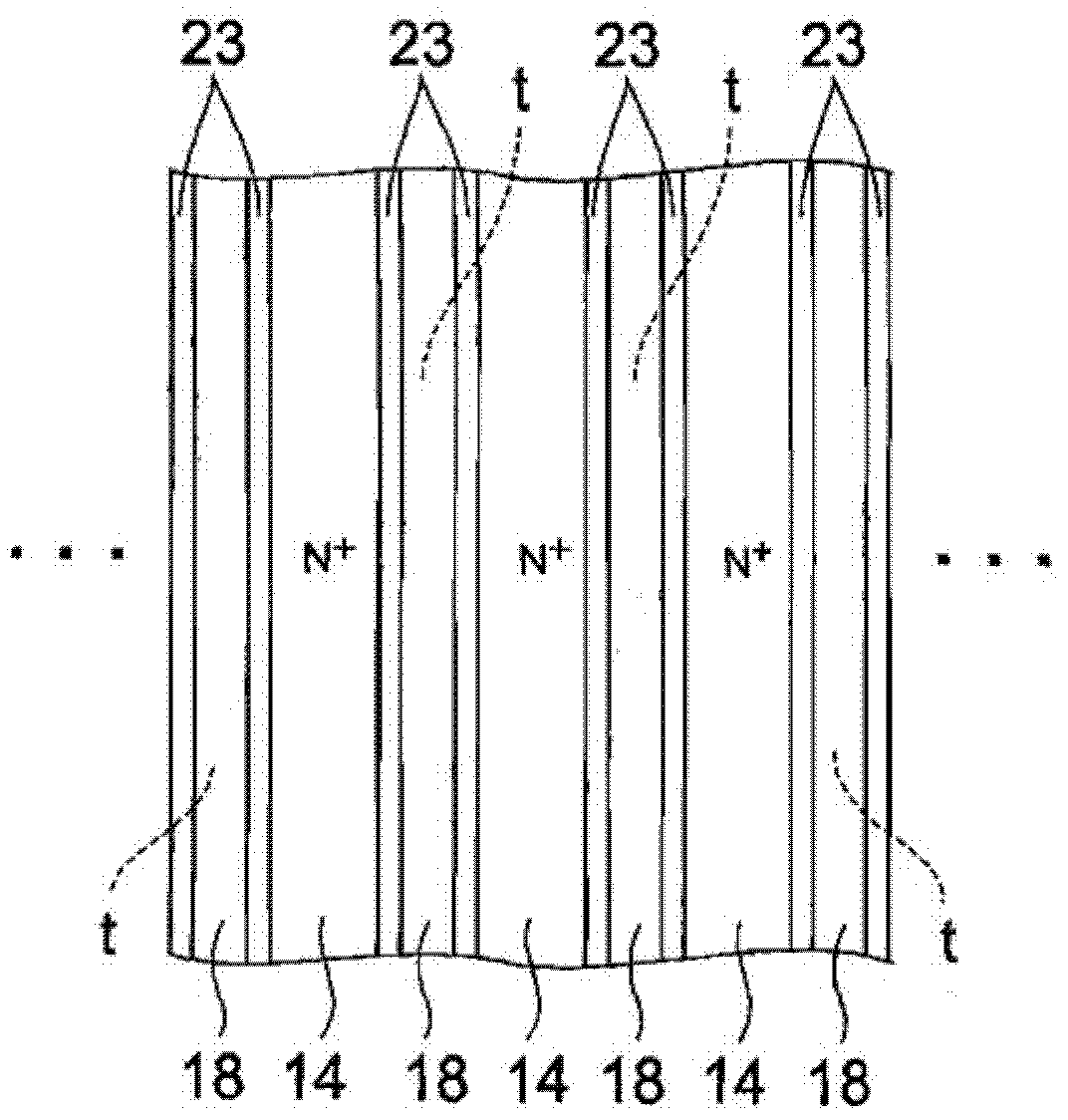

[0023] figure 2 is a schematic diagram illustrating a planar layout of main elements of the semiconductor device.

[0024] image 3 yes figure 1 A-A cutaway view.

[0025] The semiconductor layer includes N + Type drain layer 11, N - Type substrate layer 12, P type substrate layer 13, N + Type source layer 14 and P type buried layer 16. N + type drain layer 11 and N + type source layer 14 with N - The N-type substrate layer 12 has a higher concentration of impurities than the N-type.

[0026] N - type substrate layer 12 set in N + type drain layer 11. The P-type substrate layer 13 is set on the N - Type substrate layer 12. N + The P-type source layer 14 is disposed on the P-type substrate layer 13 . P-type buried layer 16 in N - In the type substrate layer 12, a plurality of them are selectively provided.

[0027] A plurality of trenches t are form...

no. 2 approach

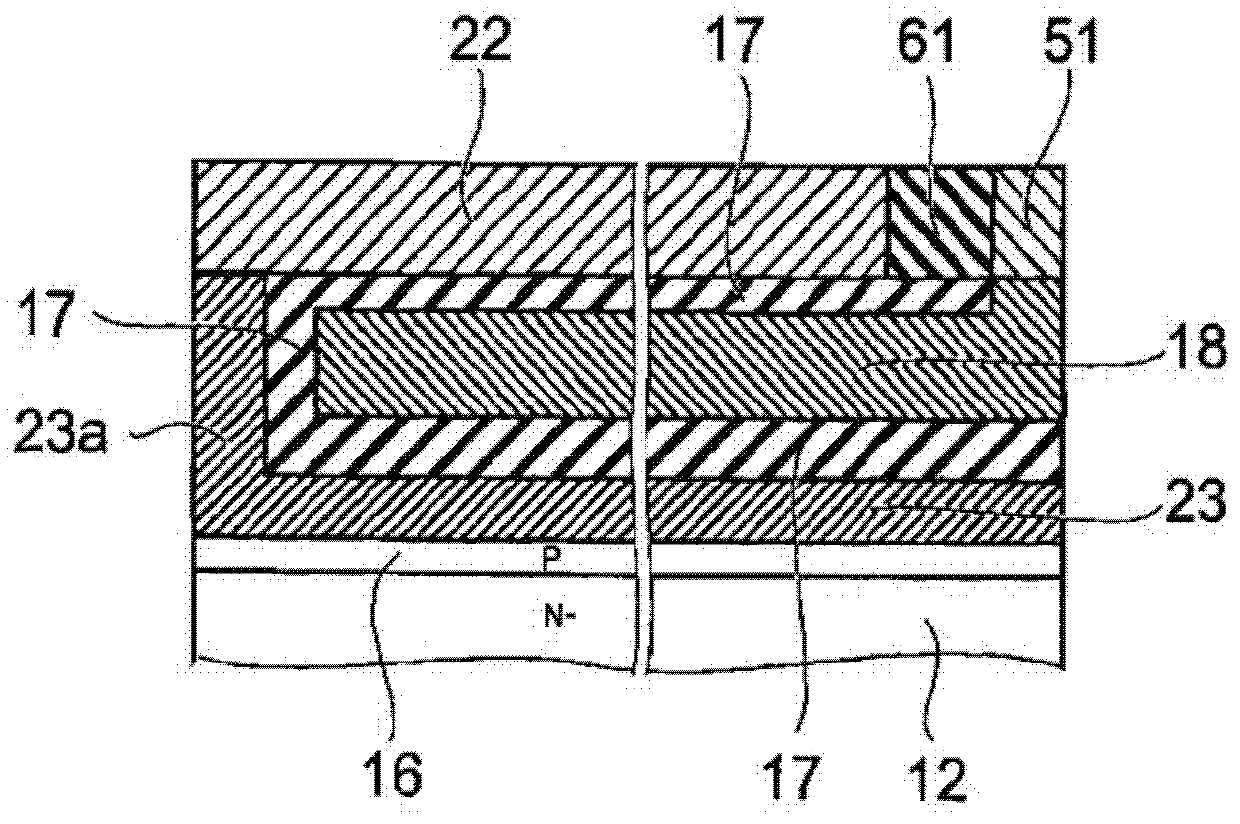

[0053] Such as Figure 4 As shown, the buried electrode 23 may not be provided in all the trenches. exist Figure 4 In , a plurality of trenches are divided into a first trench t1 and a second trench t2 to show.

[0054] The first trench t1 from N + The surface of the P-type source layer 14 penetrates the P-type substrate layer 13 and reaches the N-type - Type substrate layer 12. An insulating film 17 is formed on the bottom surface and sidewalls of the first trench t. A gate electrode 18 is buried inside the insulating film 17 . The gate electrode 18 faces the P-type underlayer 13 via the gate insulating film 17 a formed on the sidewall of the first trench t1 .

[0055] The second trench t2 is also, from N + The surface of the source layer 14 passes through the P-type substrate layer 13 to reach the N-type substrate layer 12 . The second trench t2 is deeper than the first trench t1.

[0056] in N - A P-type buried layer 16 is selectively provided in the P-type subst...

no. 3 approach

[0069] then, Figure 5 It is a schematic cross-sectional view of the semiconductor device of the third embodiment.

[0070] In this embodiment, the P-type buried layer 16 and the buried electrode 33 are not provided in all the trenches. exist Figure 5 In , a plurality of trenches are divided into a first trench t1 and a second trench t3 to represent.

[0071] The first trench t1 from N + The surface of the P-type source layer 14 penetrates the P-type substrate layer 13 and reaches the N-type - Type substrate layer 12. An insulating film 17 is formed on the bottom surface and sidewalls of the first trench t. A gate electrode 18 is buried inside the insulating film 17 . The gate electrode 18 faces the P-type underlayer 13 via the gate insulating film 17 a formed on the sidewall of the first trench t1 .

[0072] The second trench t3 also starts from N + The surface of the P-type source layer 14 penetrates the P-type substrate layer 13 and reaches the N-type - Type subst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More