Low obstruction communication router capable of realizing network on optical chip and communication method thereof

An on-chip network, blocking communication technology, applied in the field of communication, can solve the problems of affecting other node communication, low link utilization, etc., to overcome the number of optical waveguide crossings and micro-rings, reduce insertion loss and energy consumption, Overcome the effects of lower communication efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The present invention will be further described below in conjunction with the accompanying drawings.

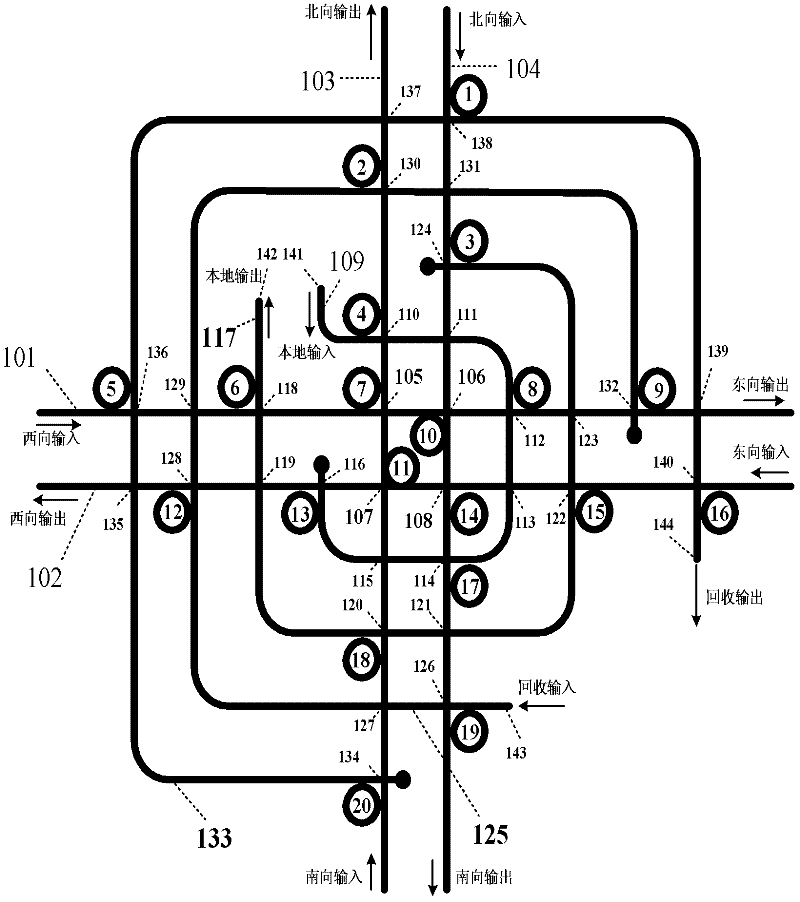

[0058] refer to figure 1 , the present invention realizes the router of network-on-chip low-blocking communication, including N optical waveguides and M microring resonators, N and M are both integers, and N≠M, in this example, N=8, M=20, But not limited to this data. The 8 optical waveguides include two horizontal optical waveguides, two vertical optical waveguides and four ring optical waveguides. The 20 microring resonators are respectively marked with integers 1-20, and all microring resonators have the same structure.

[0059] The two optical waveguides 101 and 102 in the horizontal direction and the two optical waveguides 103 and 104 in the vertical direction are arranged in a cross to form a first group of 4 intersection points, the intersection points are respectively 105, 106, 107 and 108, where One side of intersection 105 is provided with microring resonat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More