Method for improving HCI (Hot Carrier Injection) effect of high-K gate dielectric NMOS (N-Mental-Oxide-Semiconductor) by adopting gate-last process

A technology of gate-last process and gate dielectric, which is applied in the field of semiconductor manufacturing to achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

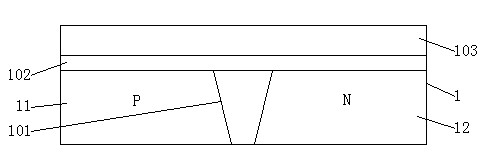

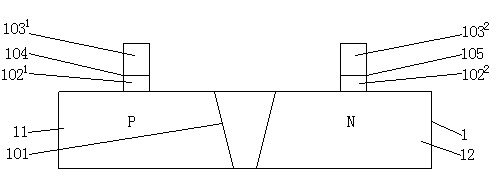

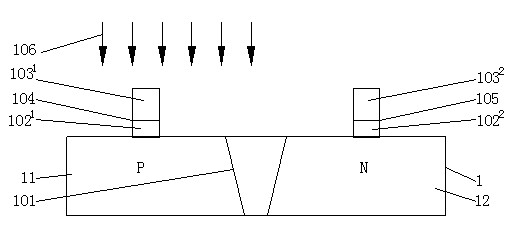

[0025] see Figure 1a As shown in -g, the present invention improves the gate-last process high-K gate dielectric NMOS HCI method, which includes the following steps:

[0026] A first dielectric layer 102 and a polysilicon layer 103 are sequentially deposited on the substrate 1, wherein the substrate 1 is provided with an isolation groove 101, and its two sides are respectively a P-type substrate 11 and an N-type substrate 12; using photolithography and Etching process, etching polysilicon layer 102 and first dielectric layer 103 to form NMOS semiconductor device sample gate 104 and PMOS semiconductor device sample gate 105, wherein, NMOS semiconductor device sample gate 104 is formed by first dielectric layer 102 1 and polysilicon layer 103 1 Composition, PMOS semiconductor device sample gate 105 is made of the first dielectric layer 102 2 and polysilicon layer 103 2 Composition: using ion implantation process 106 to implant fluorine ions into the drain source region on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More