Method for extracting parasitic parameters of interconnection lines and device

A parasitic parameter and interconnection technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of inaccurate extraction results, and achieve the effect of avoiding performance error estimation, accurate parasitic parameters, and consistent performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

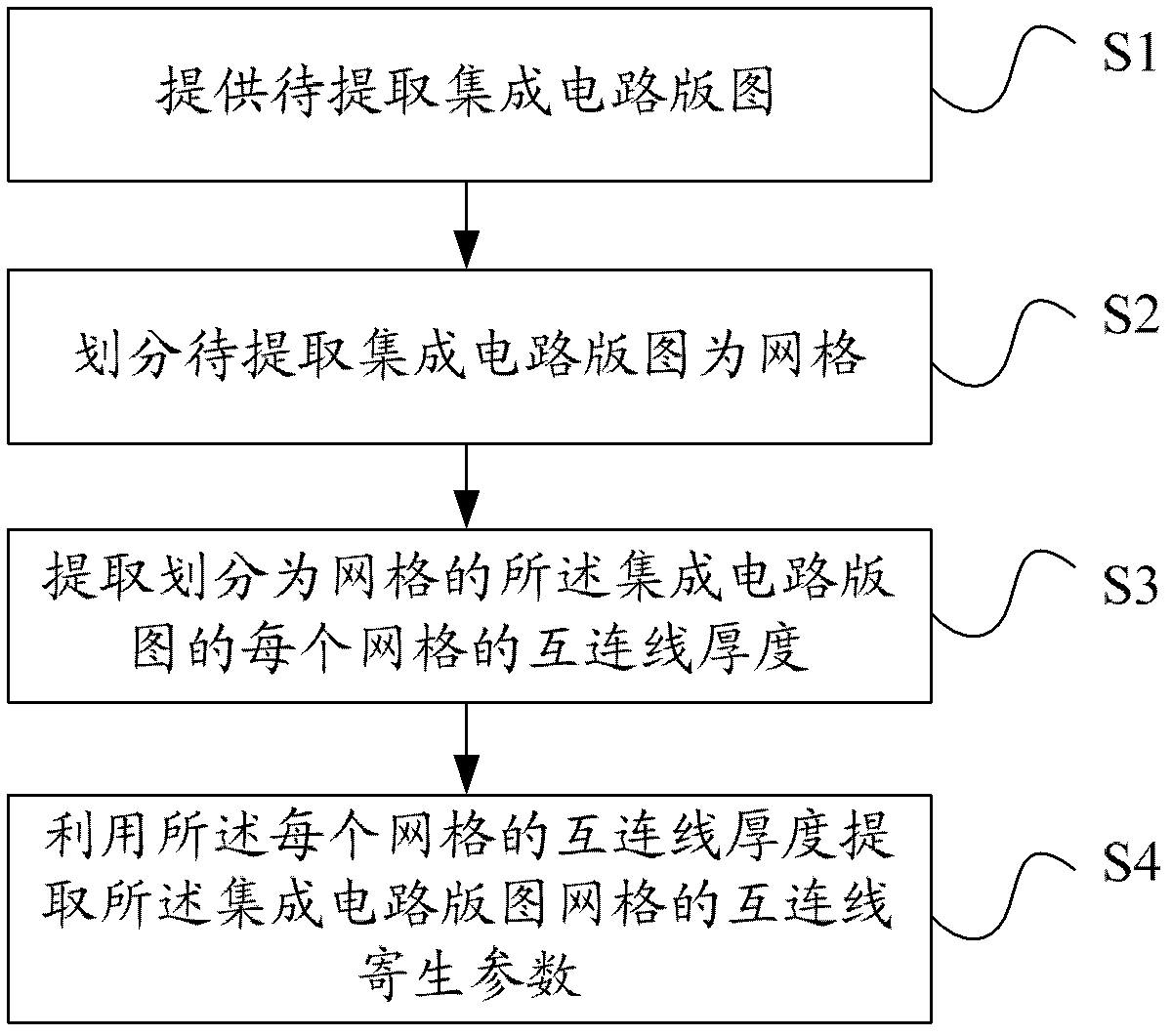

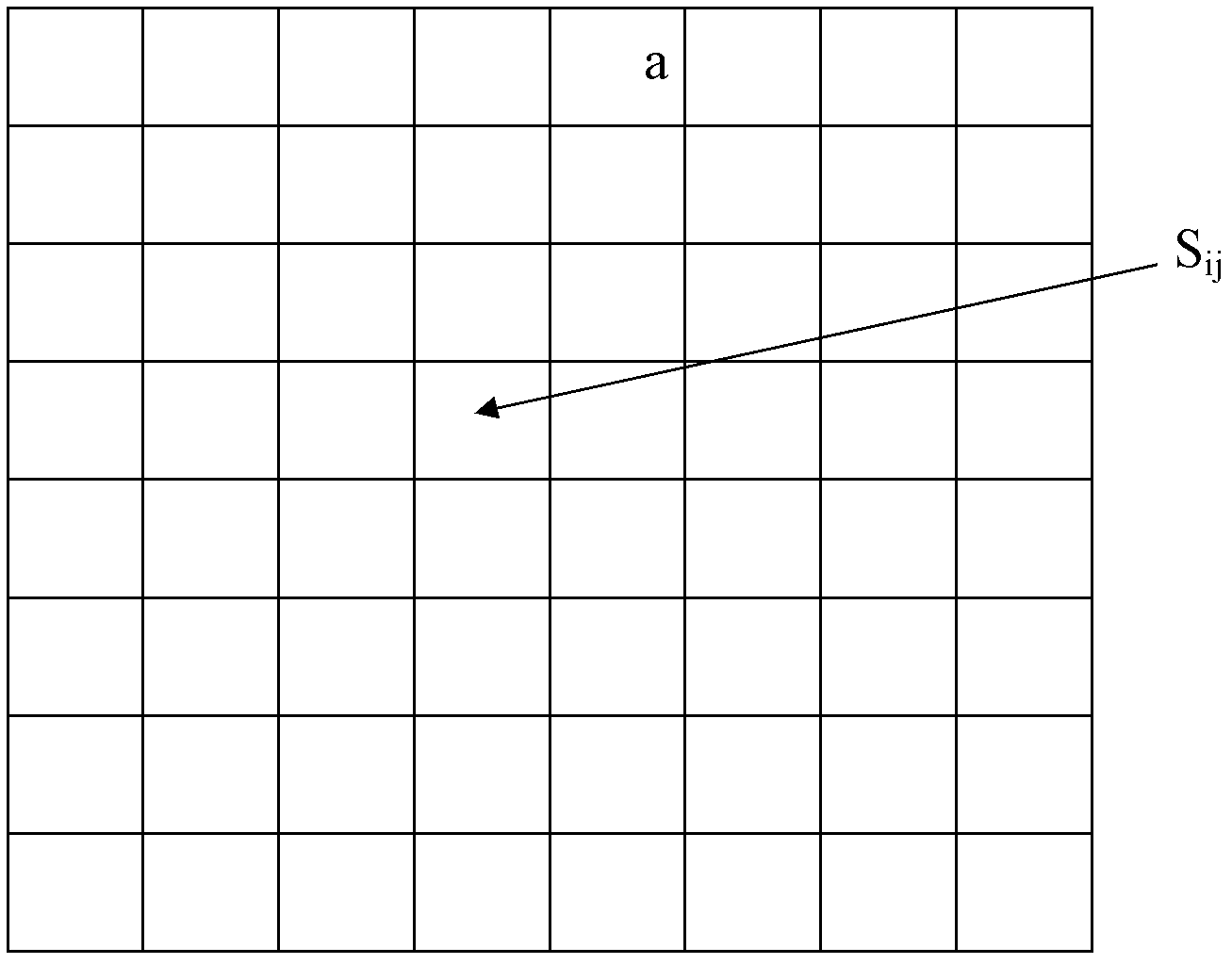

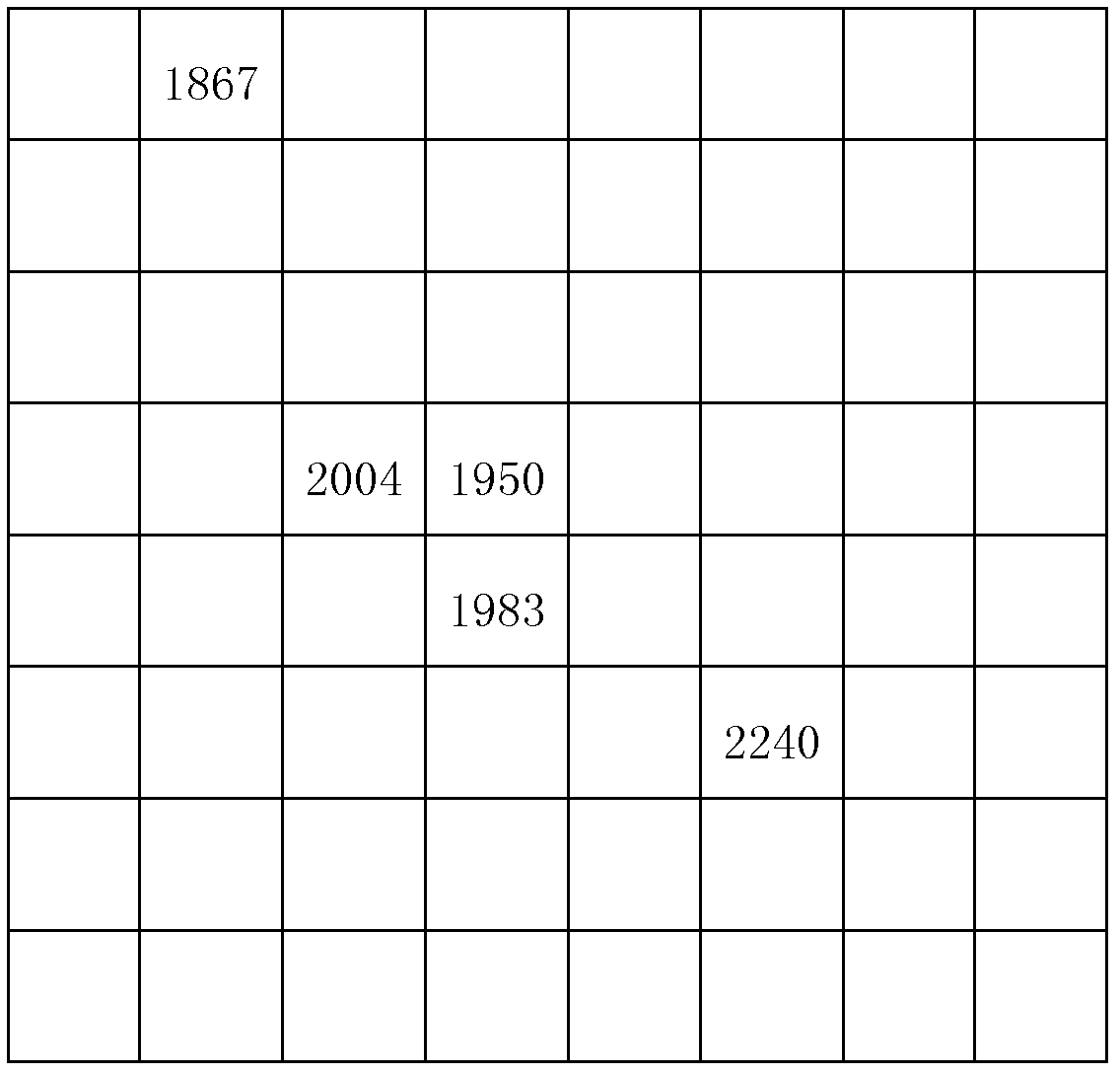

[0021] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention. Apparently, the described embodiments are only some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0022] Secondly, the present invention is described in detail with reference to the schematic diagrams. When describing the embodiments of the present invention in detail, for the convenience of explanation, the schematic diagrams are only examples, which should not limit the protection scope of the present invention.

[0023] As mentioned in the background technology, usually when the integrated circuit layout and the deposition process parameters of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More