Testing device and method for digital semiconductor device

A testing device and semiconductor technology, applied in measurement devices, instruments, measurement electronics, etc., can solve the problems of high cost, small vector storage depth, and low complexity of vector changes, and achieve the effect of reducing testing costs and saving testing time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

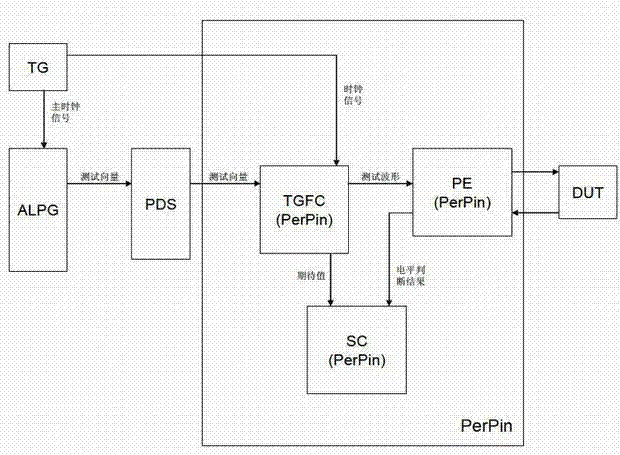

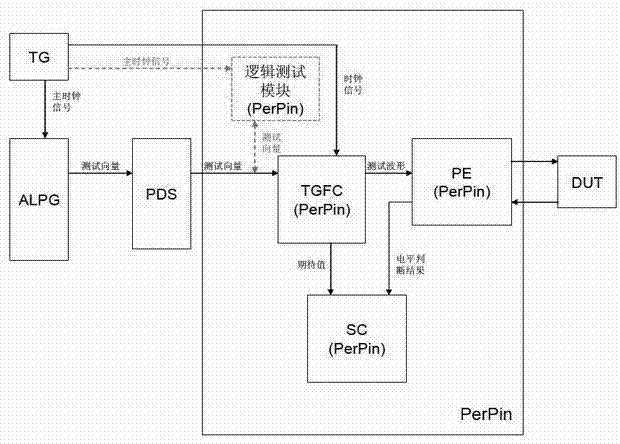

[0023] The invention discloses a test device for digital semiconductor devices, such as figure 2 shown, including:

[0024] A timing generator module that generates a master clock signal;

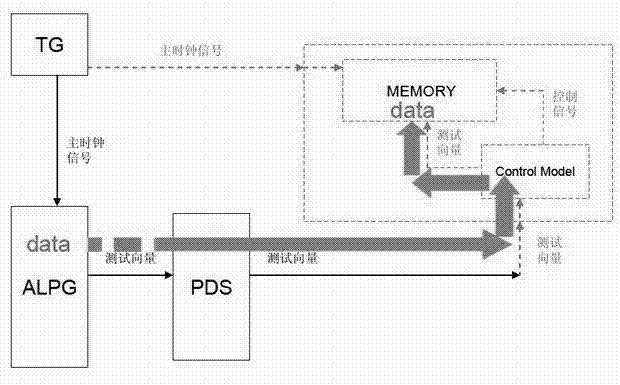

[0025] The algorithm vector generator module is used to store the test vector information. When the waveform needs to be output to the device under test, the algorithm vector generator module will output the first test vector to the programmable data selector according to the main clock signal sent by the timing generator module In the module, the first test vector is transmitted to each test module resource by switching the PDS internal switch;

[0026] The programmable data selector module receives the first test vector output by the algorithm vector generator module, and transmits the first test vector to the test module resource by switching the internal switch;

[0027] The test module includes a logic test module, a waveform format controller module, a pin circuit module and a digi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More