Forming method of graph of aligned layer on silicon chip

A technology for aligning layers and silicon wafers, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of long manufacturing time and increased process costs, and achieve the effect of contrast enhancement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

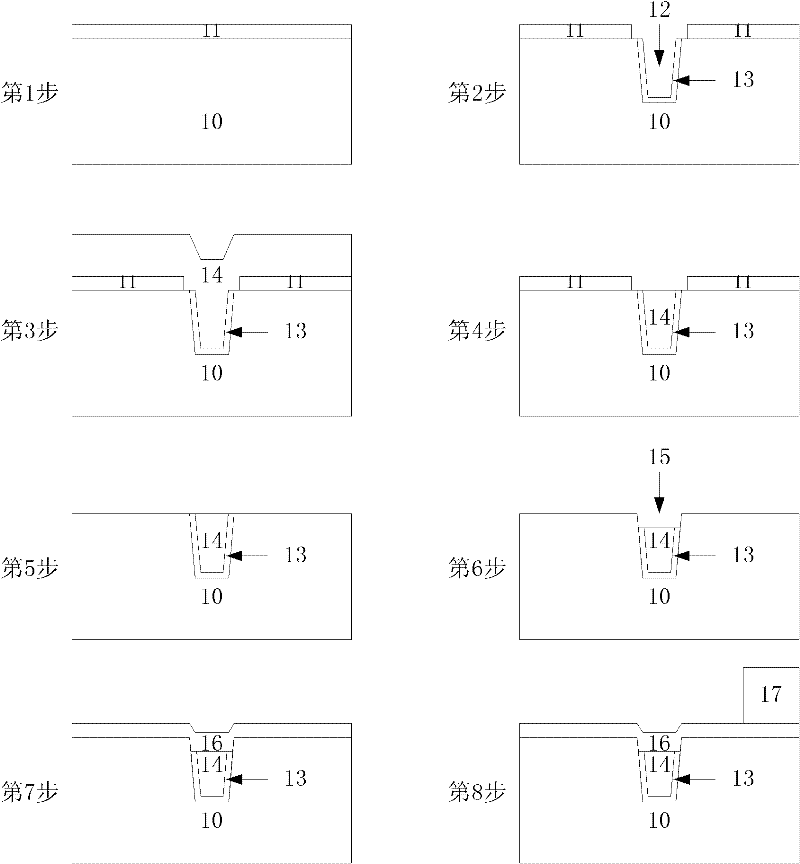

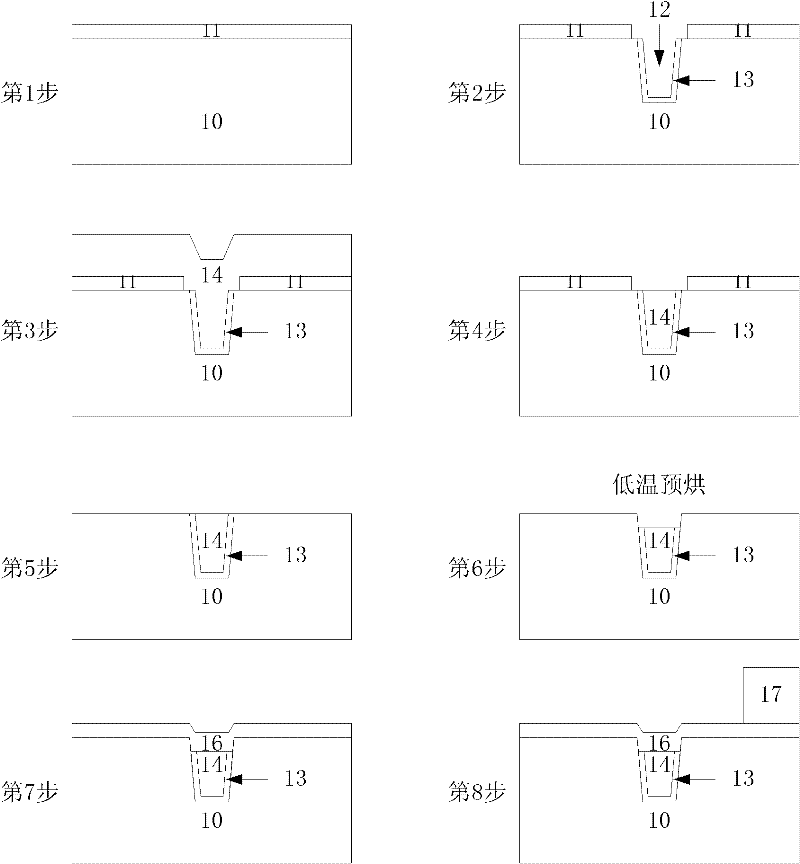

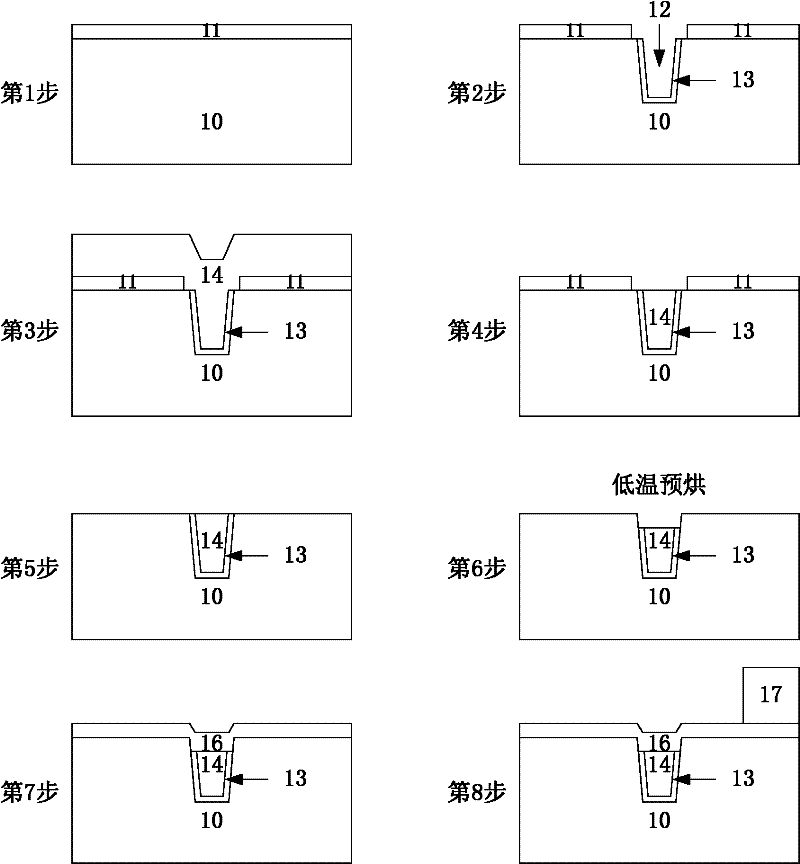

[0030] see figure 2 The method for forming the pattern of the aligned layer on the silicon wafer of the present invention comprises the following steps:

[0031] In the first step, a first dielectric layer 11, such as silicon nitride, is deposited on the substrate 10.

[0032] In the second step, a trench 12 is etched on the substrate 10 by photolithography and etching processes, and after the etching is completed, the photoresist is removed, and a pad oxide layer is grown on the bottom and side walls of the trench 12 ( Liner Oxide) 13. A shallow trench isolation (STI) process may be used to etch the trench 12 .

[0033] The groove 12 is used as an overlay mark of this layer of graphics on the silicon wafer, and the overlay mark may be a line or shape (such as a square ring, a cross, etc.) from a top view of the silicon wafer, but from a cross-sectional view of the silicon wafer It's the groove. The aligned layer pattern is a silicon wafer pattern formed on the basis of o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More