Processor system, as well as multi-channel memory copying DMA accelerator and method thereof

A technology of processor system and memory copy, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of slow copy speed, low system efficiency, lack of universal compatibility, etc., and achieve good portability, avoid dependence, and high The effect of parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

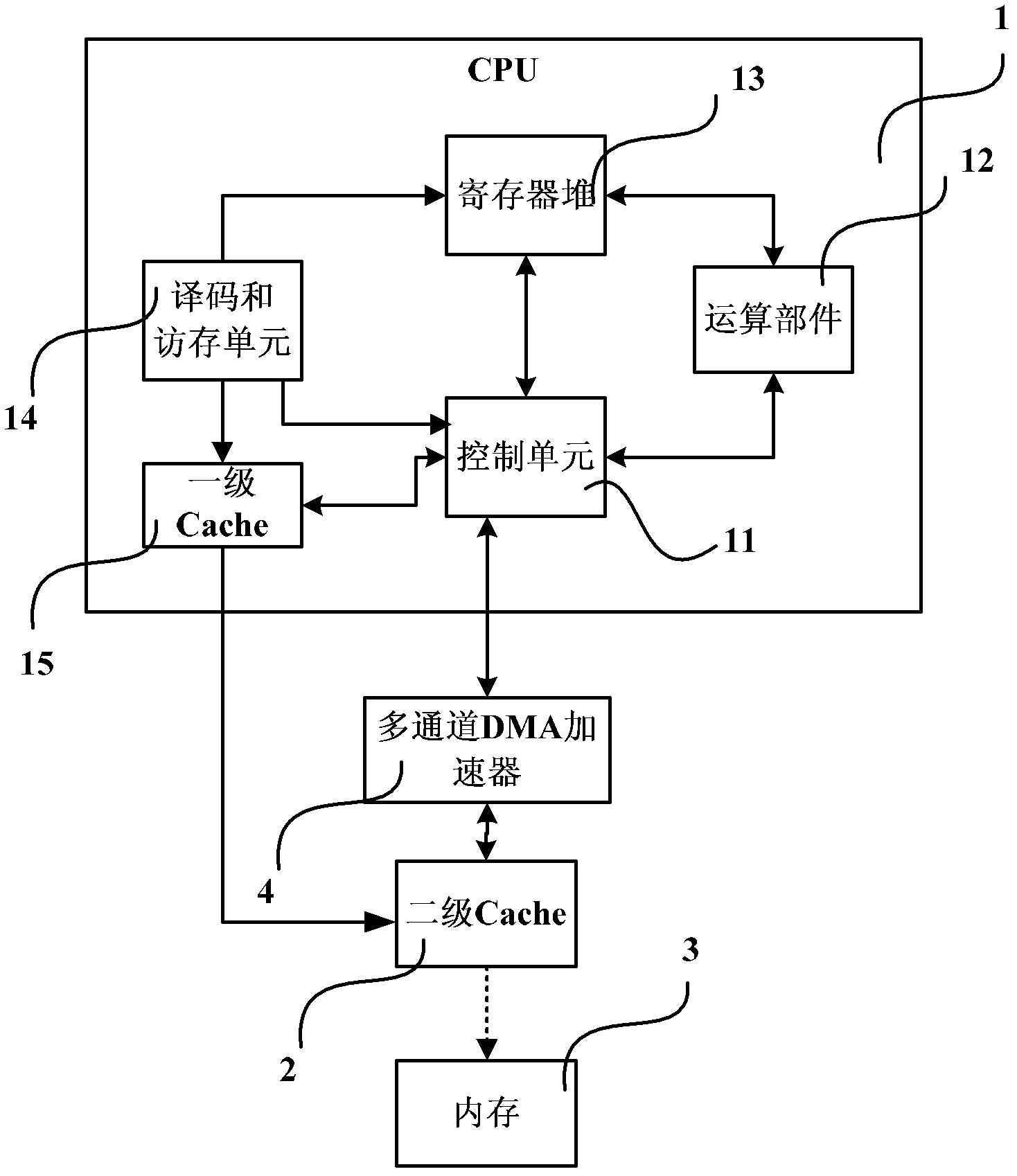

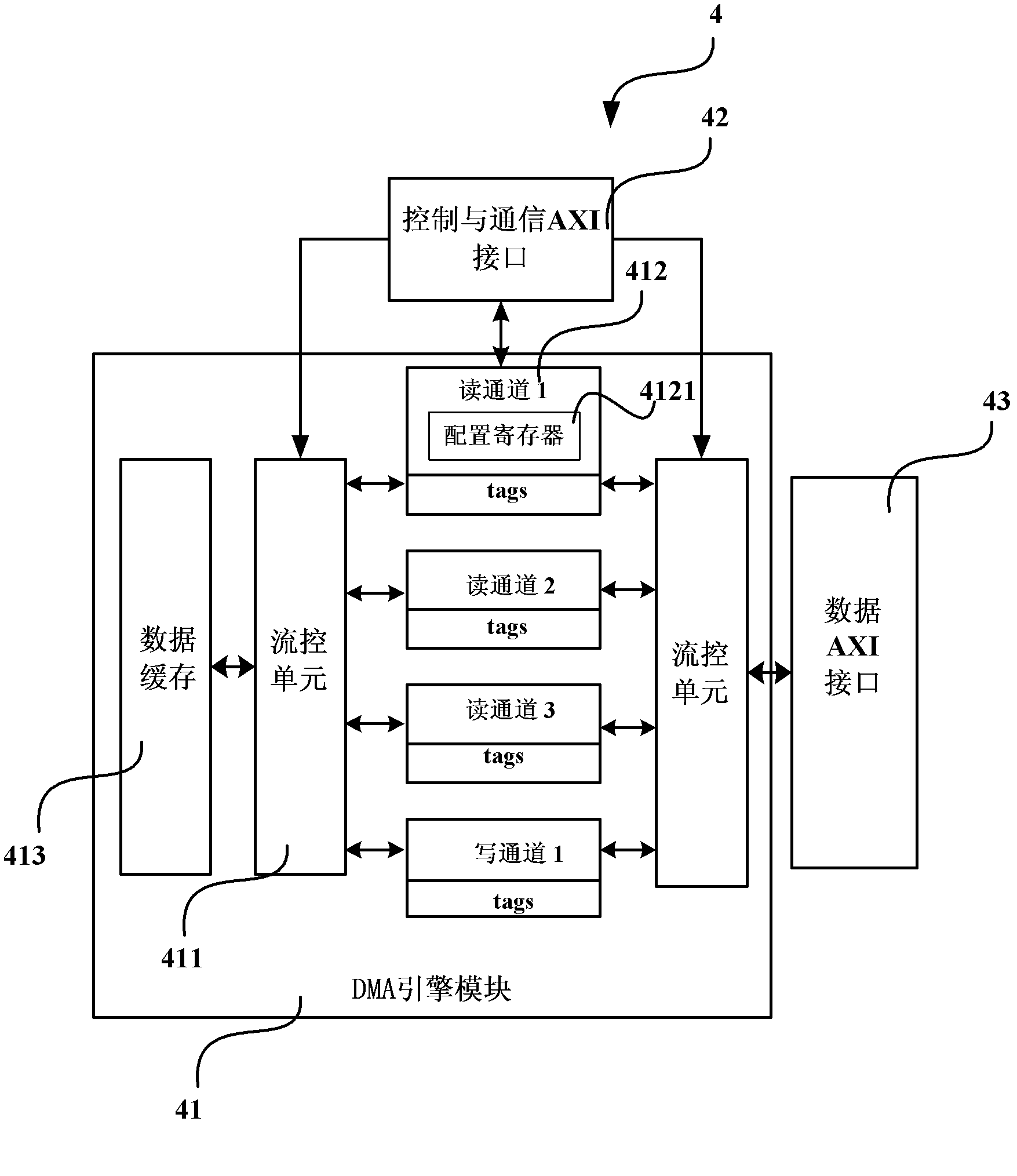

[0064] Such as figure 2 As shown, the processor system of the embodiment of the present invention includes a processor core 1, a memory 3, and a multi-channel DMA (Direct Memory Access) connected between the processor core 1 and the memory 3 through a data bus Accelerator 4;

[0065] The multi-channel DMA accelerator 4 is used to judge and decompose the task information of the data read and write request according to the task information of the data read and write request when the processor core 1 sends the data read and write request of the memory copy command, and According to the task information of the decomposed data read-write request, and the read-write frequency and priority of multiple read-write channels, and the value of the flag bit of the read-write channel, control multiple read-write channels to send to the memory 3 in parallel Read and write requests multiple times to complete data reading and writing.

[0066] Preferably, as an implementable mode, the proce...

Embodiment 2

[0128] Correspondingly, an embodiment of the present invention provides a memory copy acceleration method, including the following steps:

[0129] Step S101, the control unit of the processor core sends a memory copy command to the multi-channel DMA accelerator;

[0130]Step S102, when the multi-channel DMA accelerator receives the data read and write request of the memory copy command sent by the processor core to the memory, it judges and decomposes the task information of the data read and write request according to the task information of the data read and write request, And according to the task information of the decomposed data read-write request, and the read-write frequency and priority of the multiple read-write channels, and the value of the flag bit of the read-write channel, control multiple read-write channels to issue to the memory in parallel Multiple read and write requests, parallel data read and write, until all read and write operations are completed;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More