Method and device for repairing memory chip, and memory chip

A memory chip and backup storage technology, applied in static memory, instruments, etc., can solve problems such as unusable, unreachable, and difficult to repair, and achieve the effect of reducing the probability of damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0065] One of the core concepts of the embodiments of the present invention is to add a second interface in the memory chip, and the addressing of the backup cell is performed by the second interface; in this way, after the erasing operation is successful, the backup cell can be checked through the second interface Whether it is in the over-erased state, and correct the backup cells in the over-erased state through soft programming operations, so as to prevent these backup cells from remaining in the over-erased state, thereby reducing the probability of damage to the backup cells.

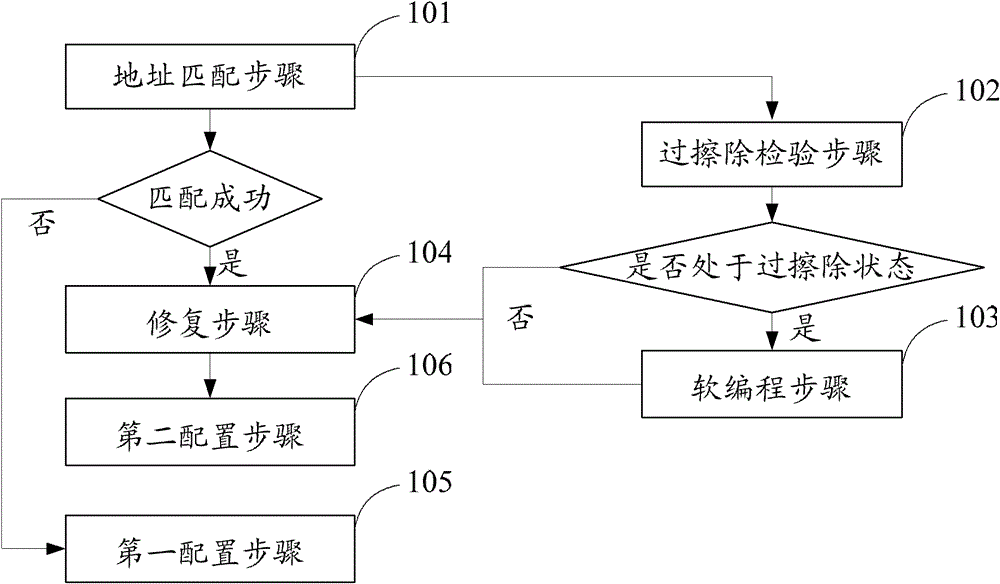

[0066] refer to figure 1 , which shows a flow chart of Embodiment 1 of a method for repairing a memory chip according to the present invention, which...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More