Semiconductor storage device

A storage device and semiconductor technology, applied in the direction of semiconductor devices, information storage, semiconductor/solid-state device manufacturing, etc., can solve the problems of characteristic deviation and large difference, so as to suppress the increase of the area, shorten the length of the bit line, and realize the reduction of the area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

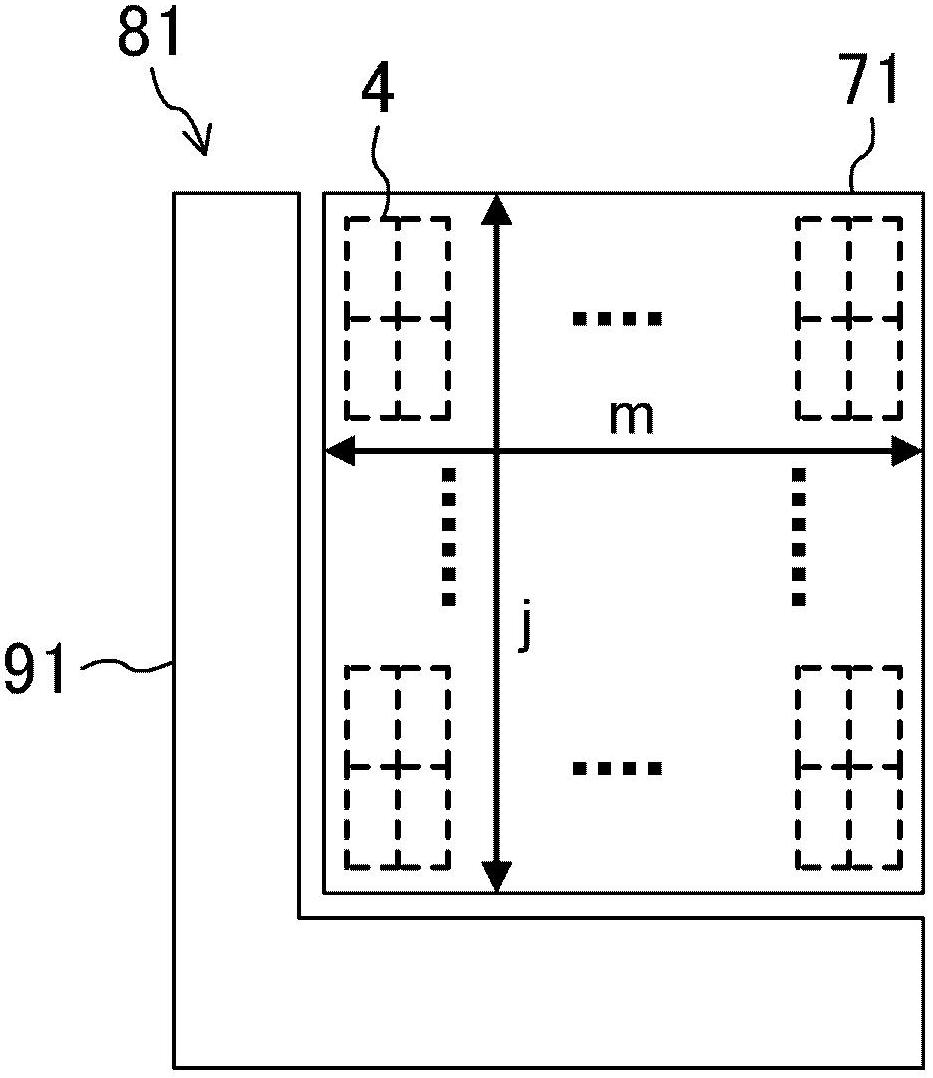

[0034] figure 1 It is a block diagram of ROM81 concerning 1st Embodiment of this invention. exist figure 1 Among them, 71 is a memory array in which the cell patterns 4 are arranged in a matrix (m×j). Wherein, m is the number of cell patterns in the horizontal direction (word line direction), and j is the number of cell patterns in the vertical direction (bit line direction). 91 is a peripheral circuit for outputting data stored in a ROM memory cell, and is connected to the memory array 71 via a word line and a bit line.

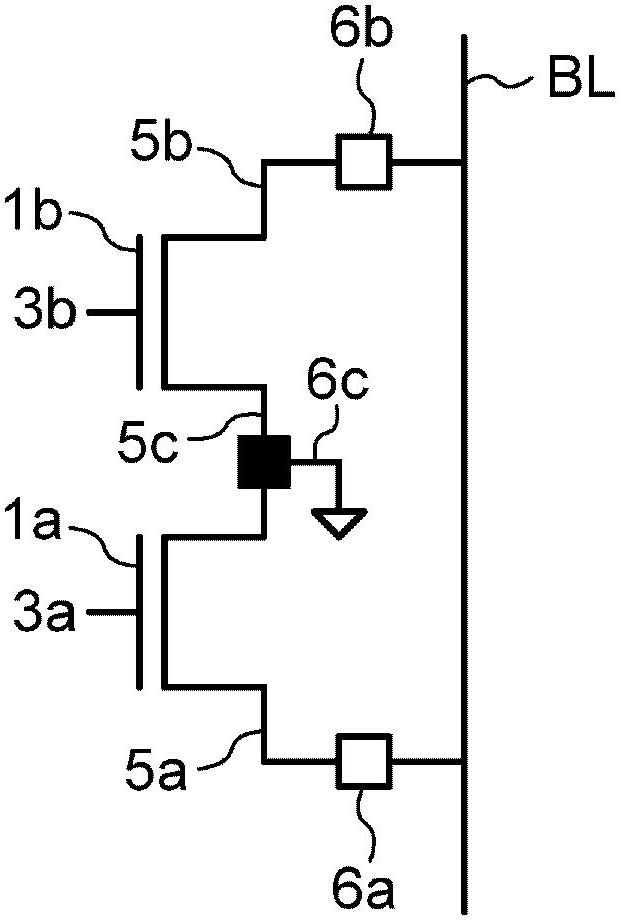

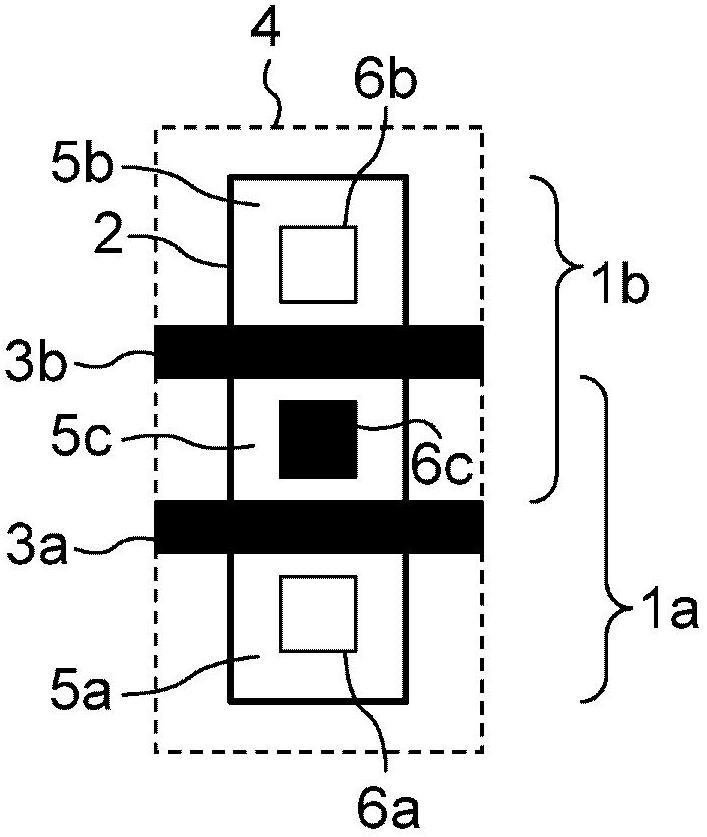

[0035] Figure 2(a) shows figure 1 The circuit diagram of a unit pattern 4 in Fig. 2(b) is its layout pattern diagram. In FIG. 2(a) and FIG. 2(b), 1a and 1b respectively denote N-channel memory cell transistors constituting one ROM memory cell. 2 is a diffusion pattern constituting the memory cell transistors 1a and 1b, and 3a and 3b are gate terminals of the memory cell transistors 1a and 1b, which are connected to word lines. 5a, 5b, and 5c denote dif...

no. 2 approach

[0045] Figure 4 It is a block diagram of a hierarchical bit line structure type ROM 82 having a memory array 72 divided into two arrays according to the second embodiment of the present invention. exist Figure 4 Among them, 72 is a storage array divided into two arrays, ie, a first array 101 and a second array 102 . The first and second arrays 101 and 102 are arrays in which the unit patterns 4 are arranged in a matrix (m×j), respectively. 20 is a logic circuit, which is composed of completely different patterns from the first and second arrays 101, 102, connected to the first and second arrays 101, 102 via bit lines, and the logic circuit 20 is used to control ROM readout, including Amplifier etc.; 92 is the peripheral circuit. The logic circuit 20 outputs stored data to the outside through other wirings.

[0046] Figure 5 yes Figure 4 A detailed layout pattern diagram of the storage array 72 in FIG. Each column of the first array 101 and the second array 102 has b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com