Patents

Literature

40results about How to "Increase in inhibition area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

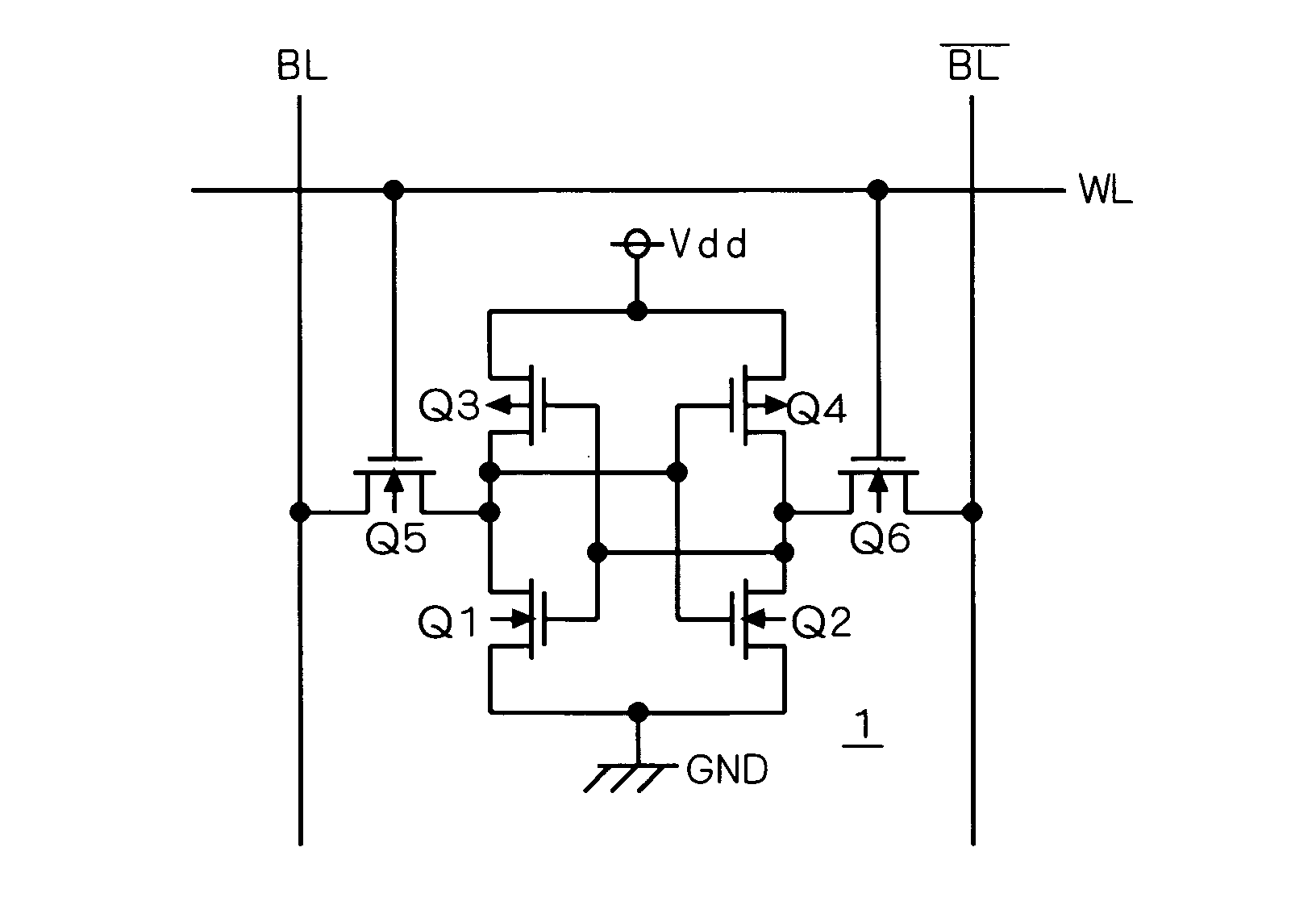

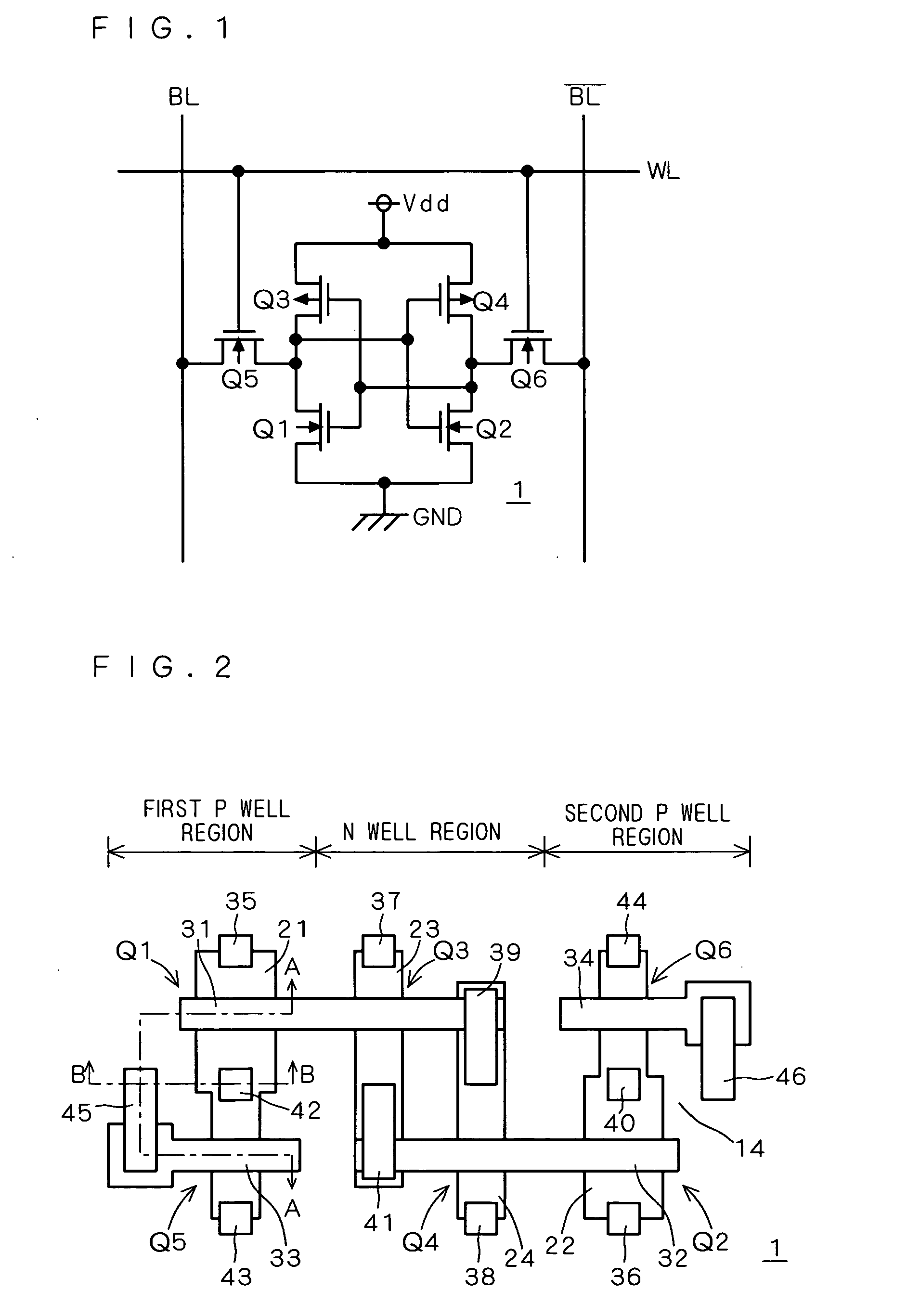

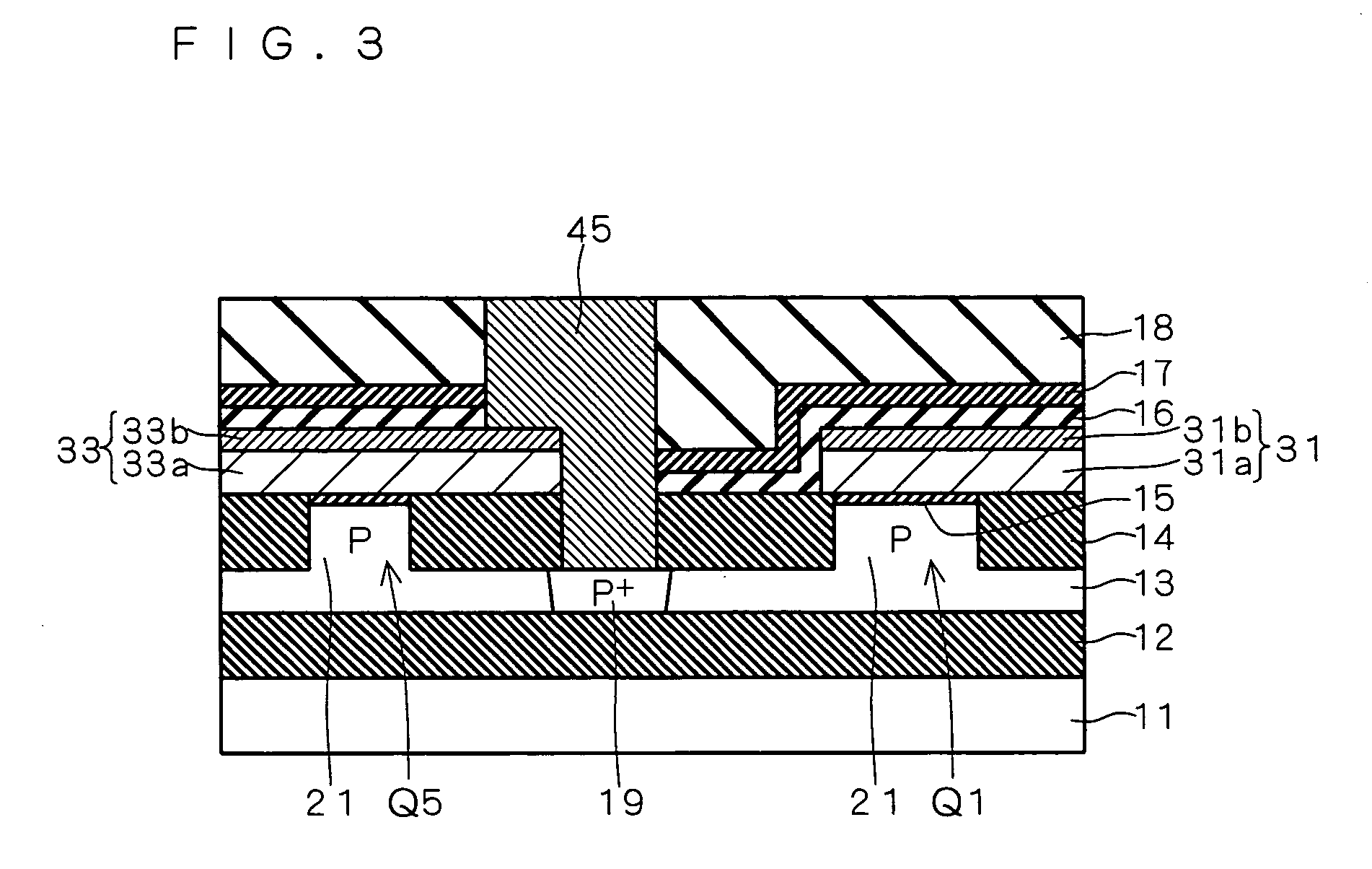

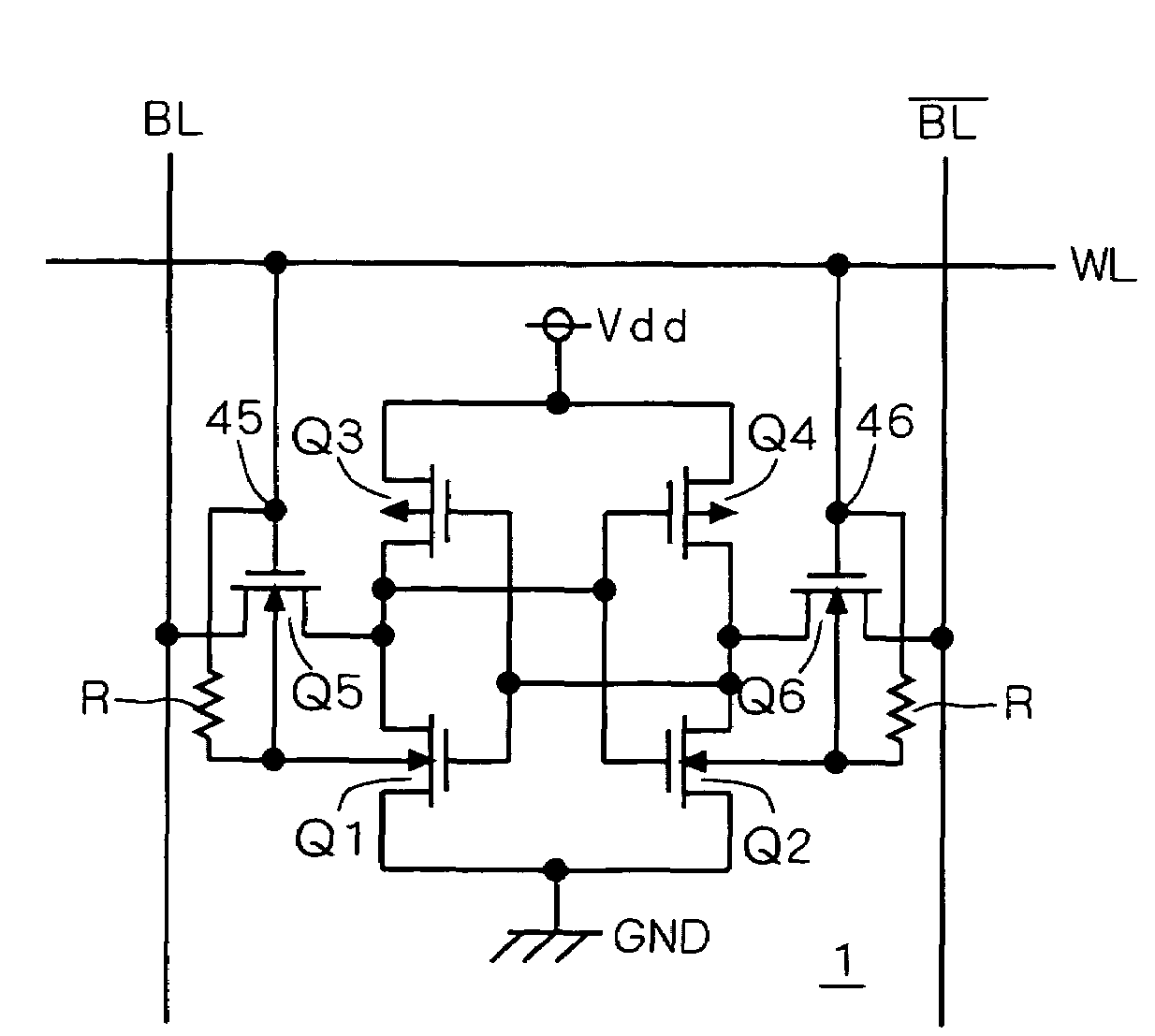

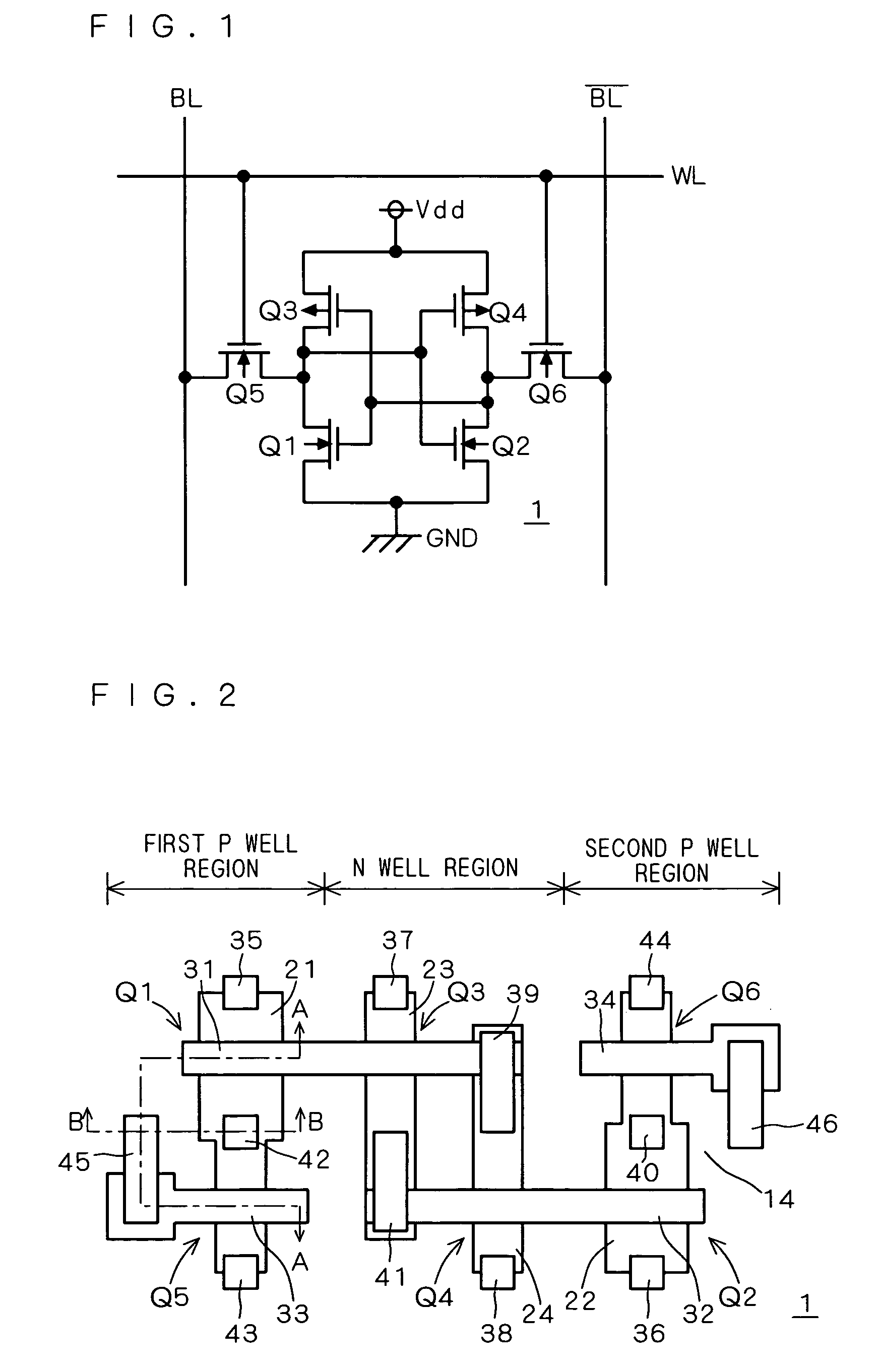

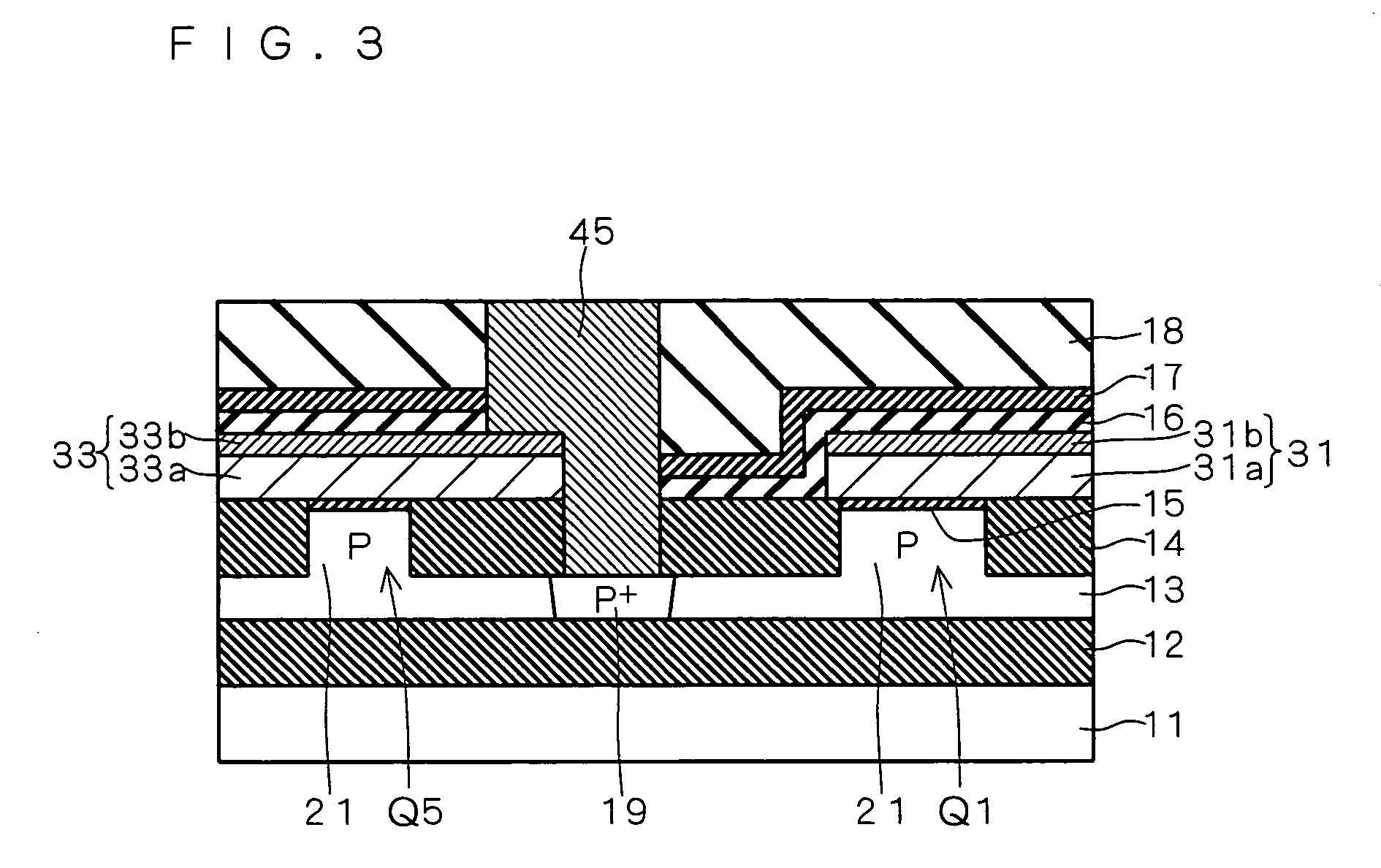

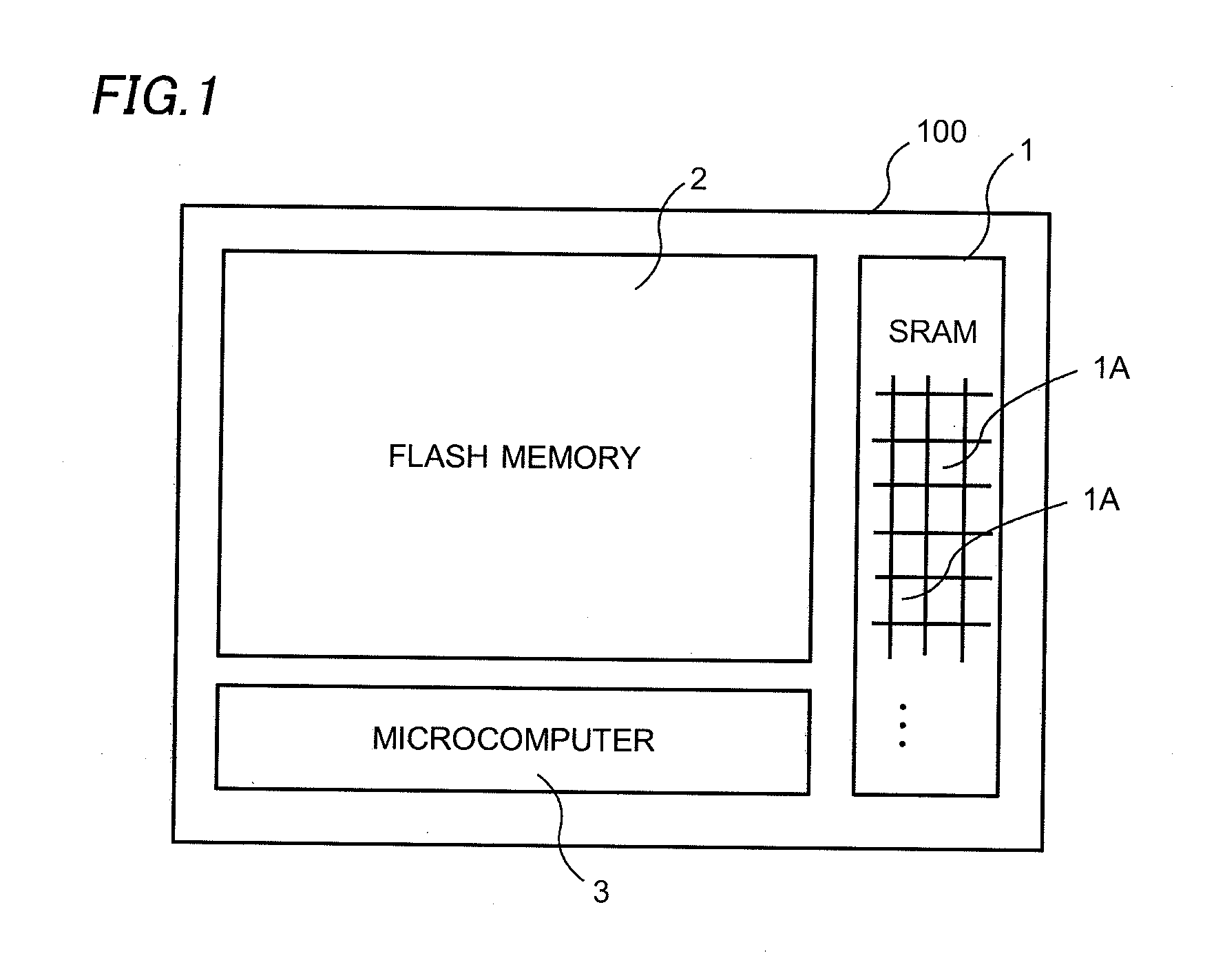

Semiconductor memory device and method of manufacturing the same

InactiveUS20050078546A1Improve reliabilityIncrease the areaTransistorSolid-state devicesEngineeringBody region

A contact connected to a word line is formed on a gate electrode of an access transistor of an SRAM cell. The contact passes through an element isolation insulating film to reach an SOI layer. A body region of a driver transistor and that of the access transistor are electrically connected with each other through the SOI layer located under the element isolation insulating film. Therefore, the access transistor is in a DTMOS structure having the gate electrode connected with the body region through the contact, which in turn is also electrically connected to the body region of the driver transistor. Thus, operations can be stabilized while suppressing increase of an area for forming the SRAM cell.

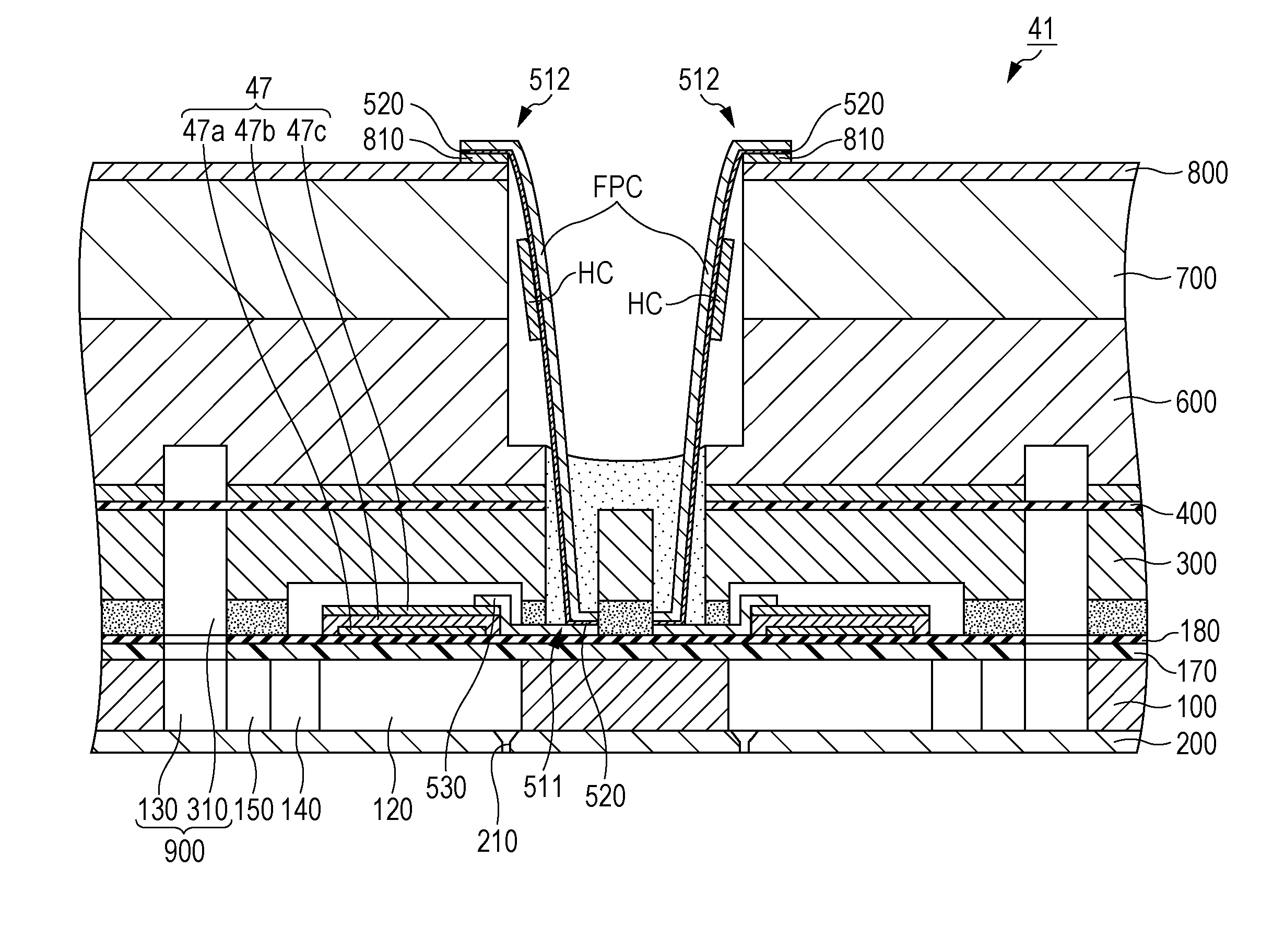

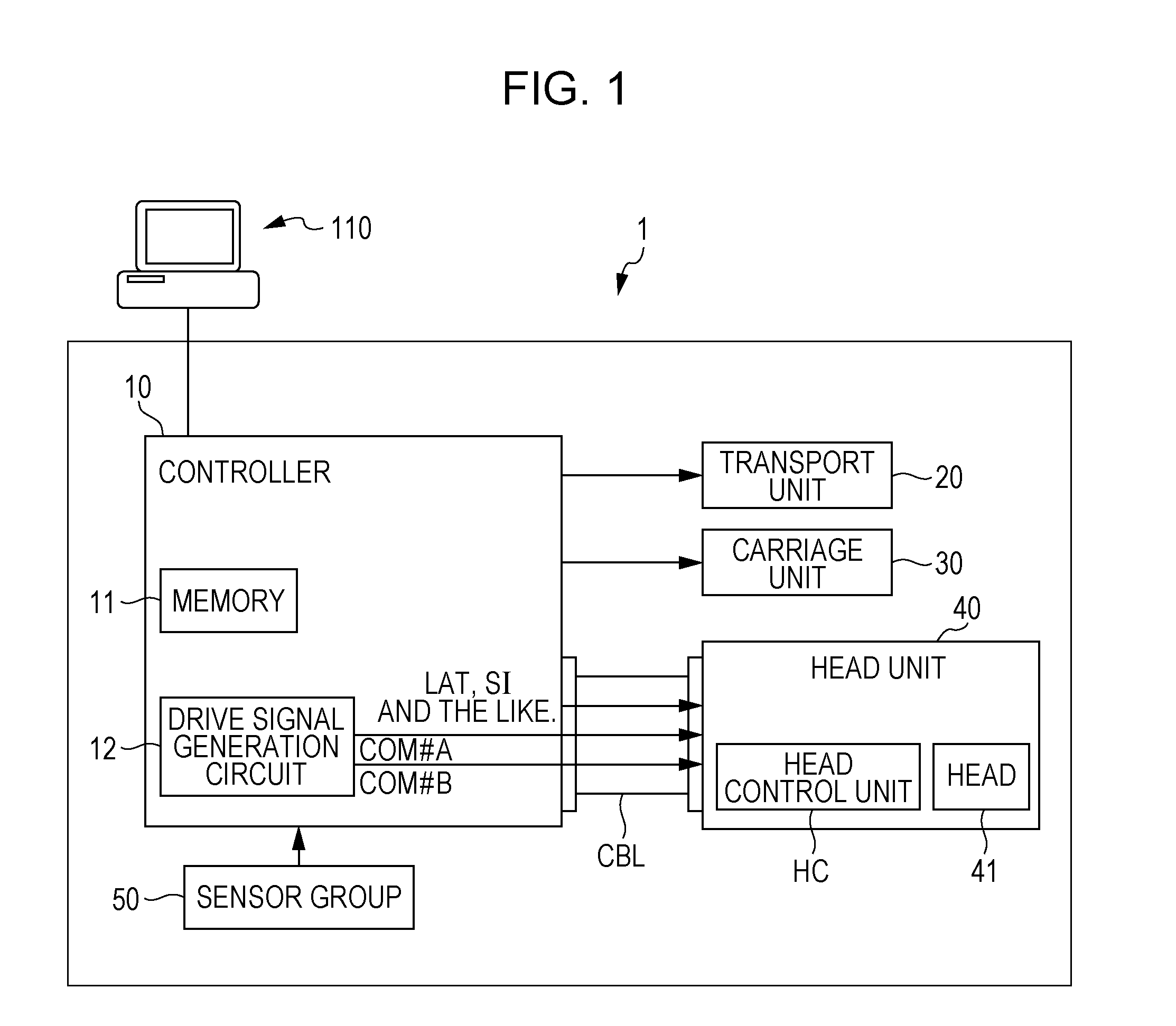

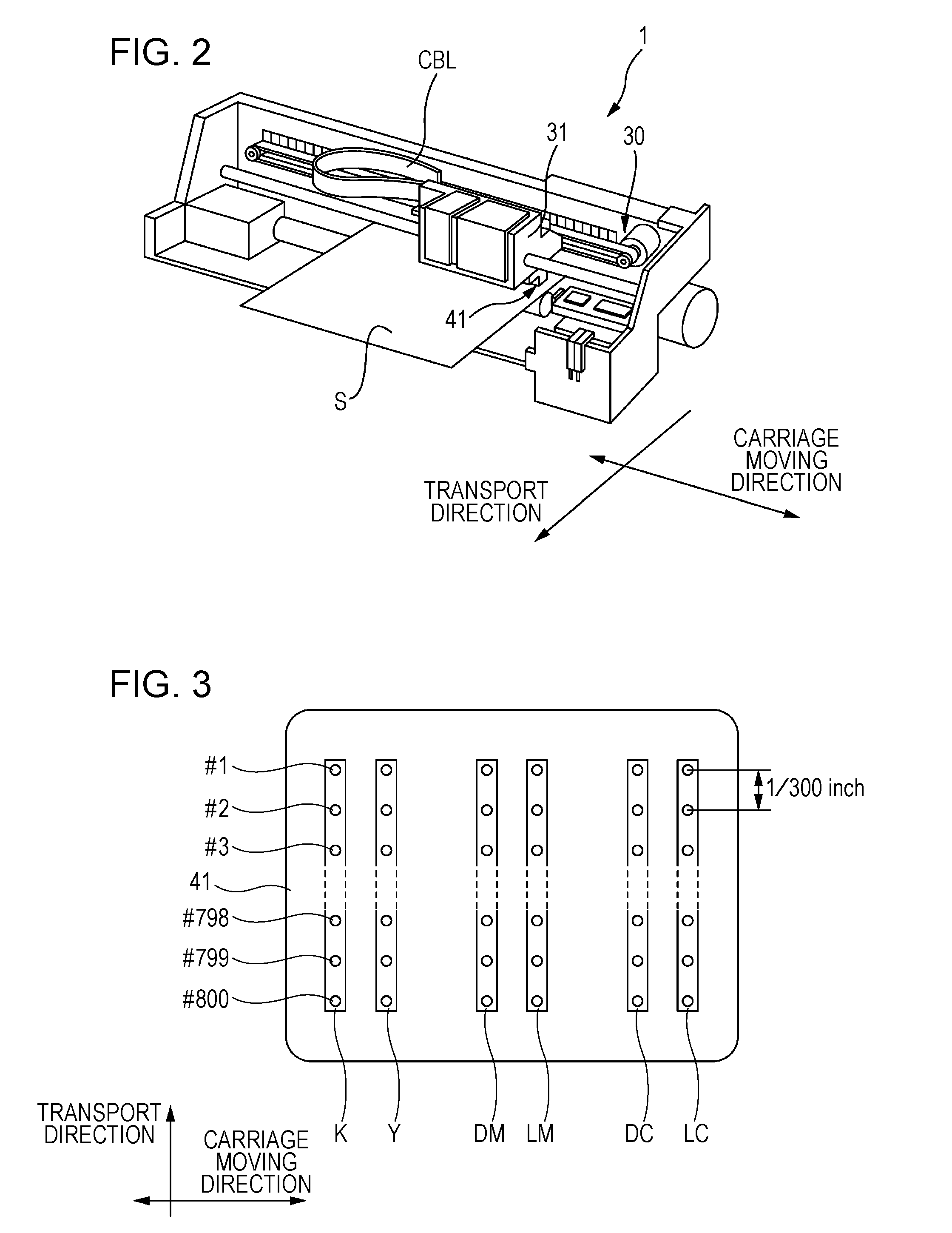

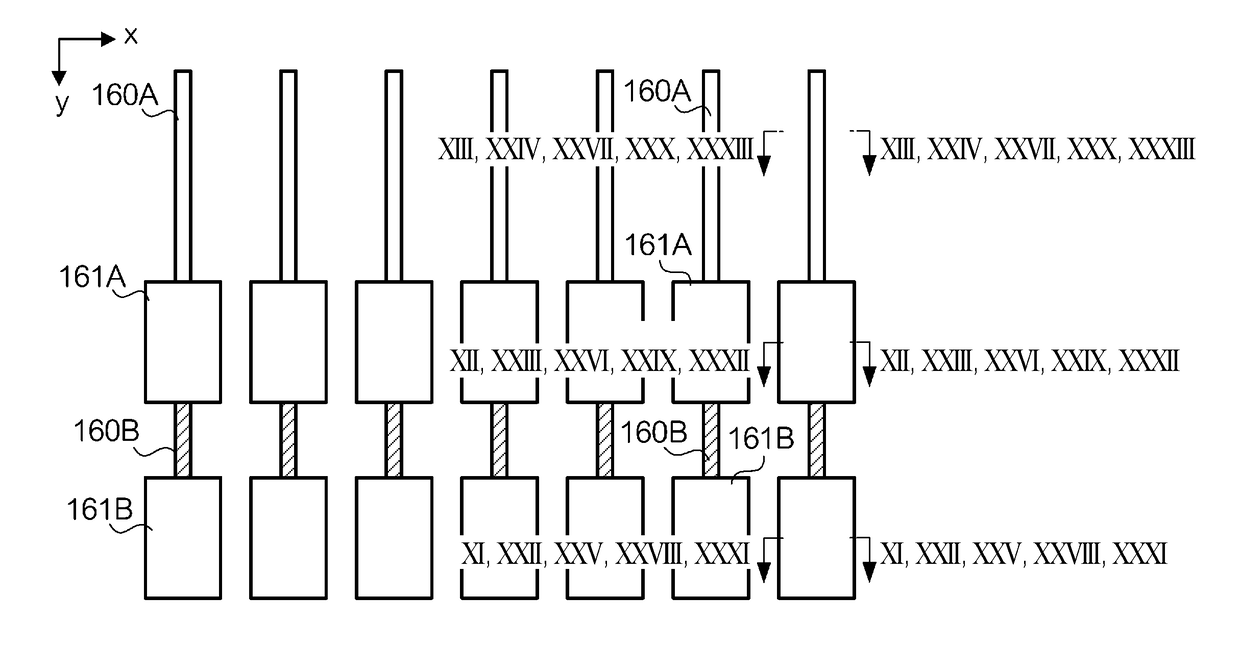

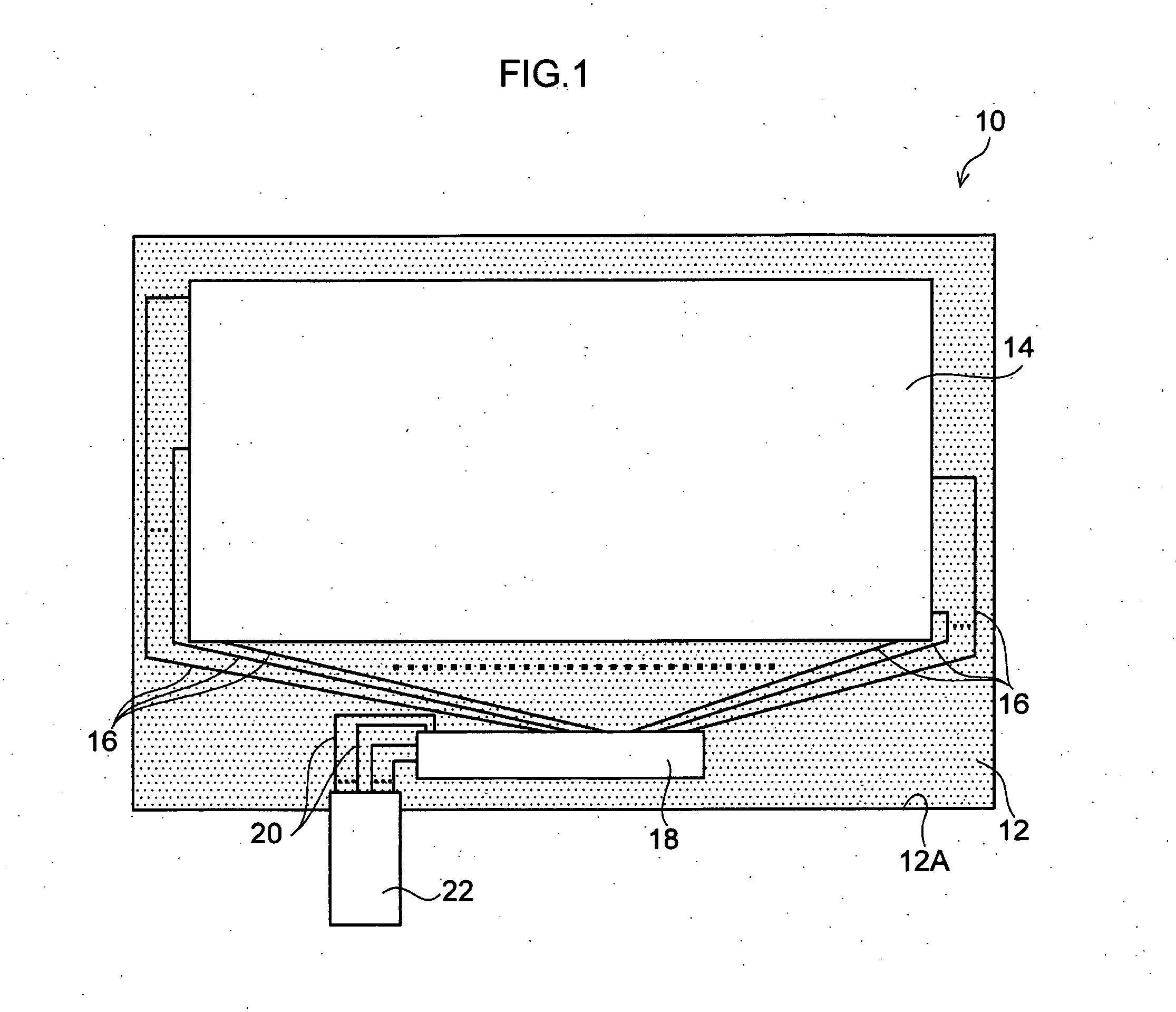

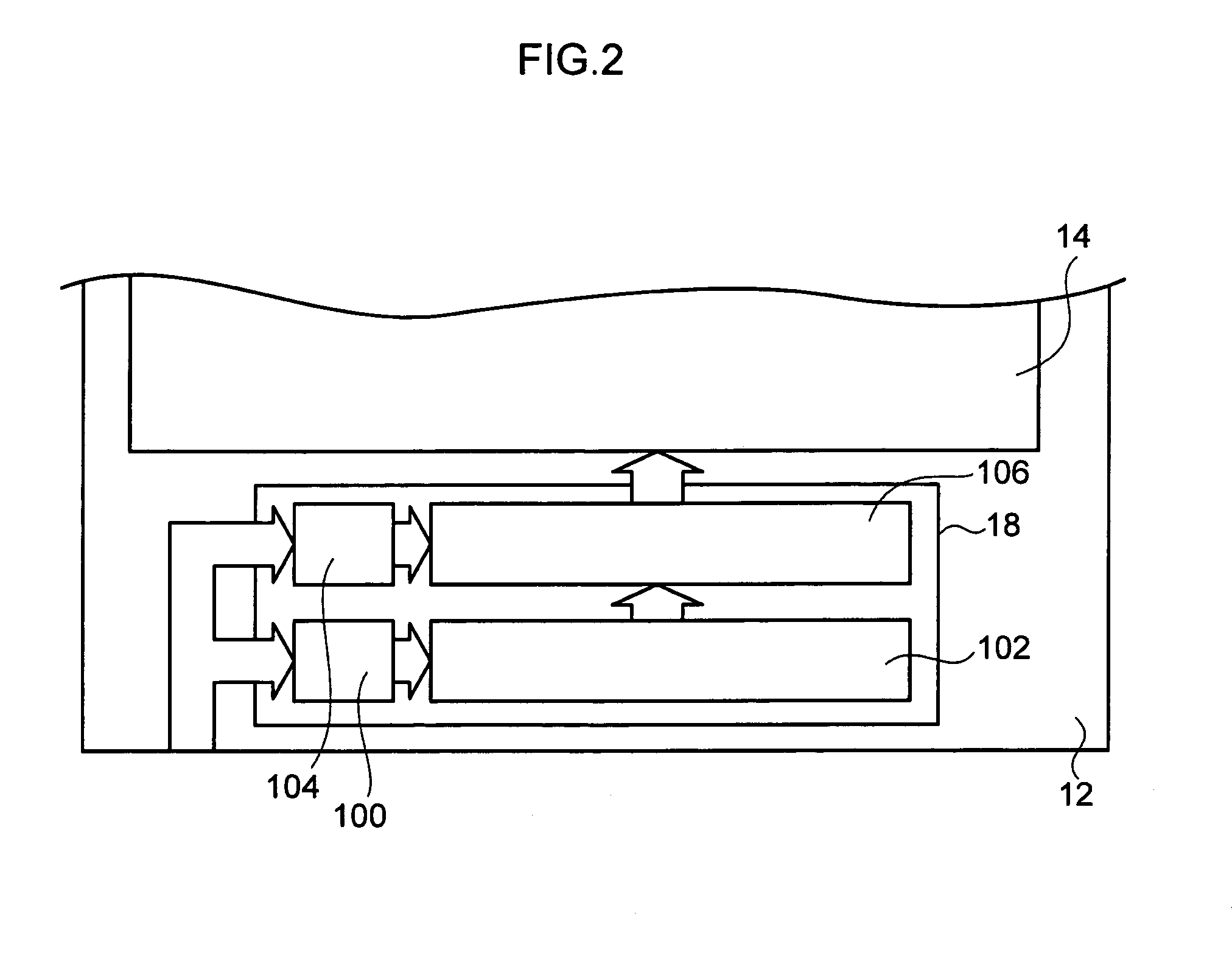

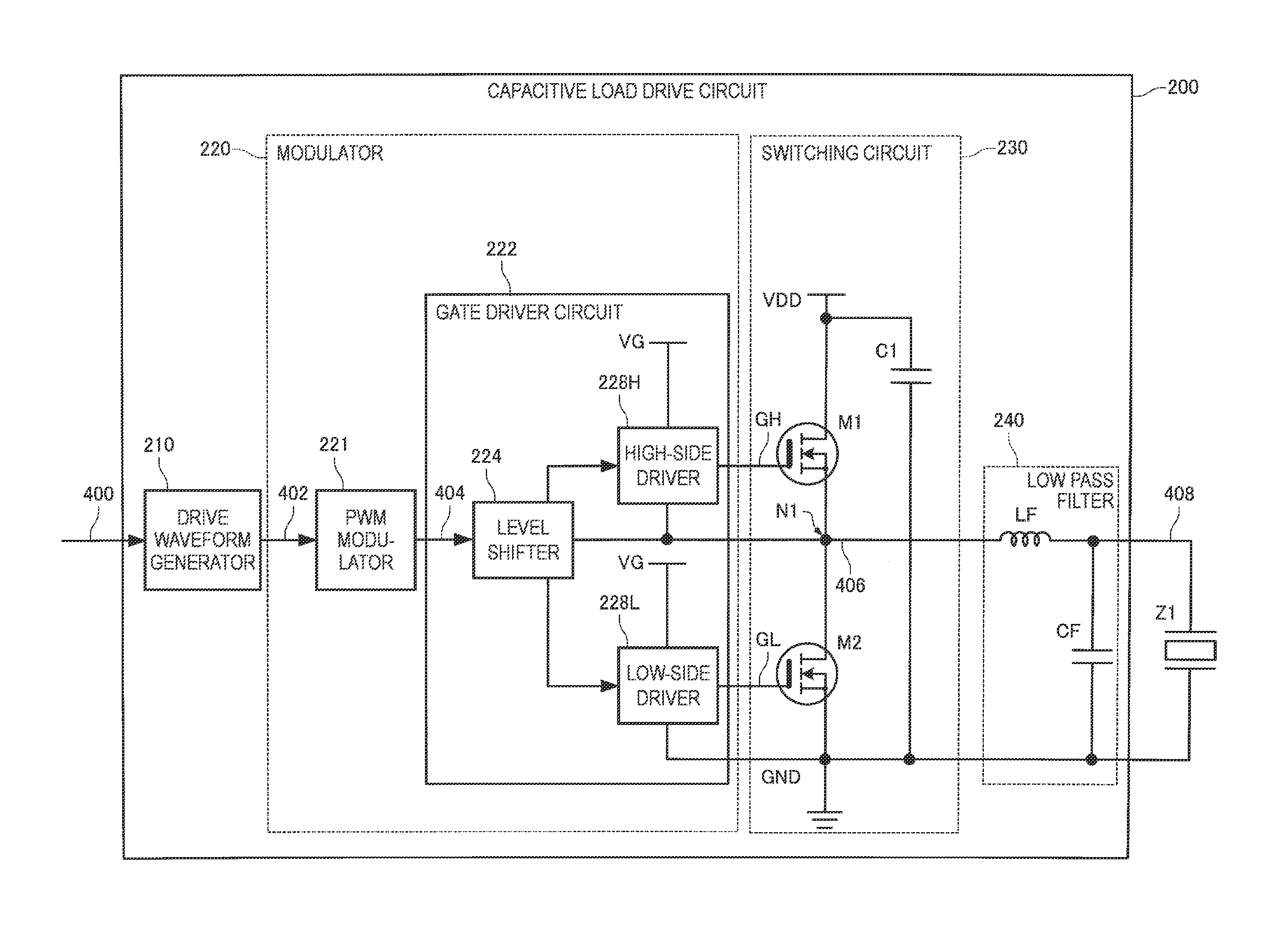

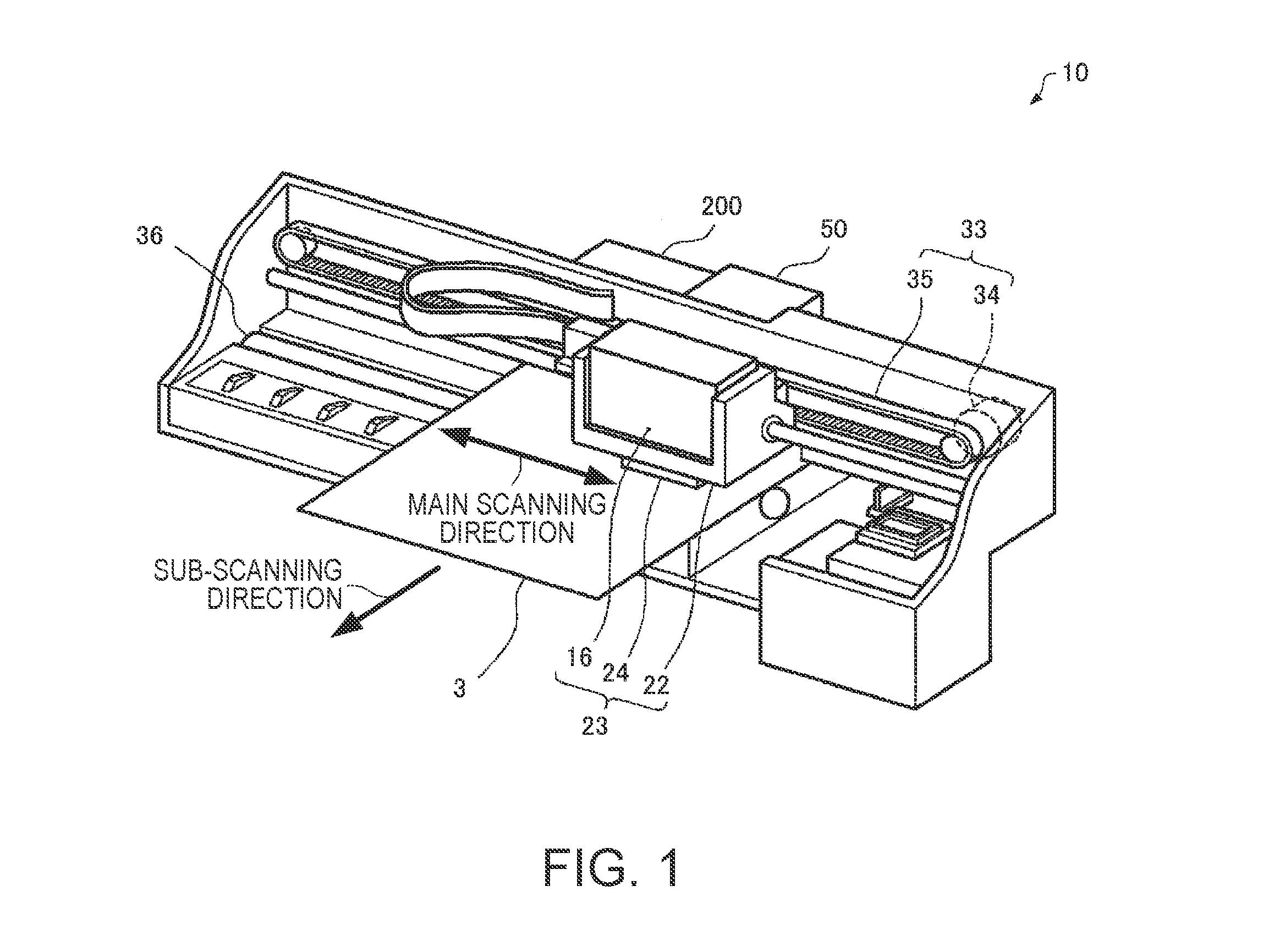

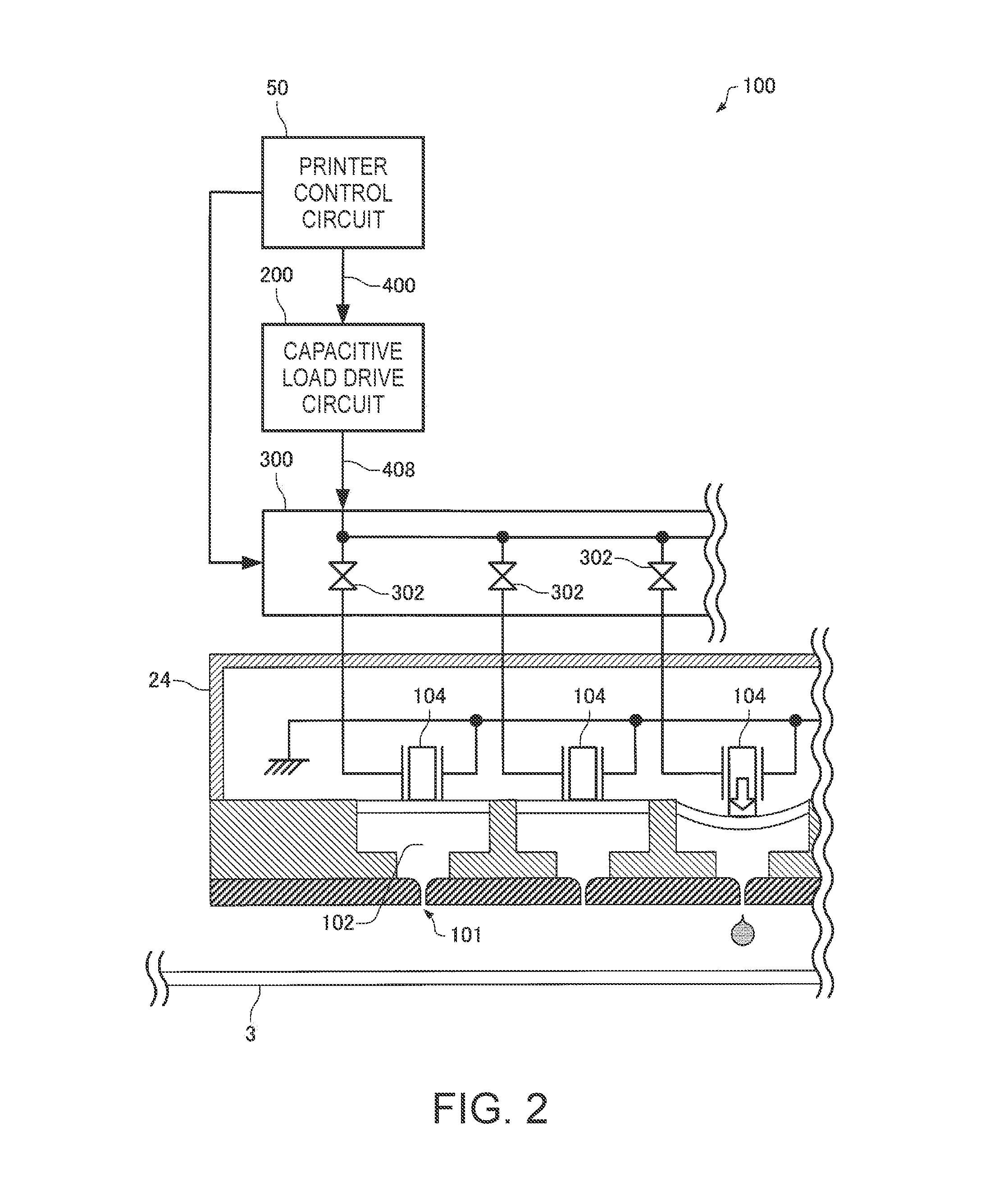

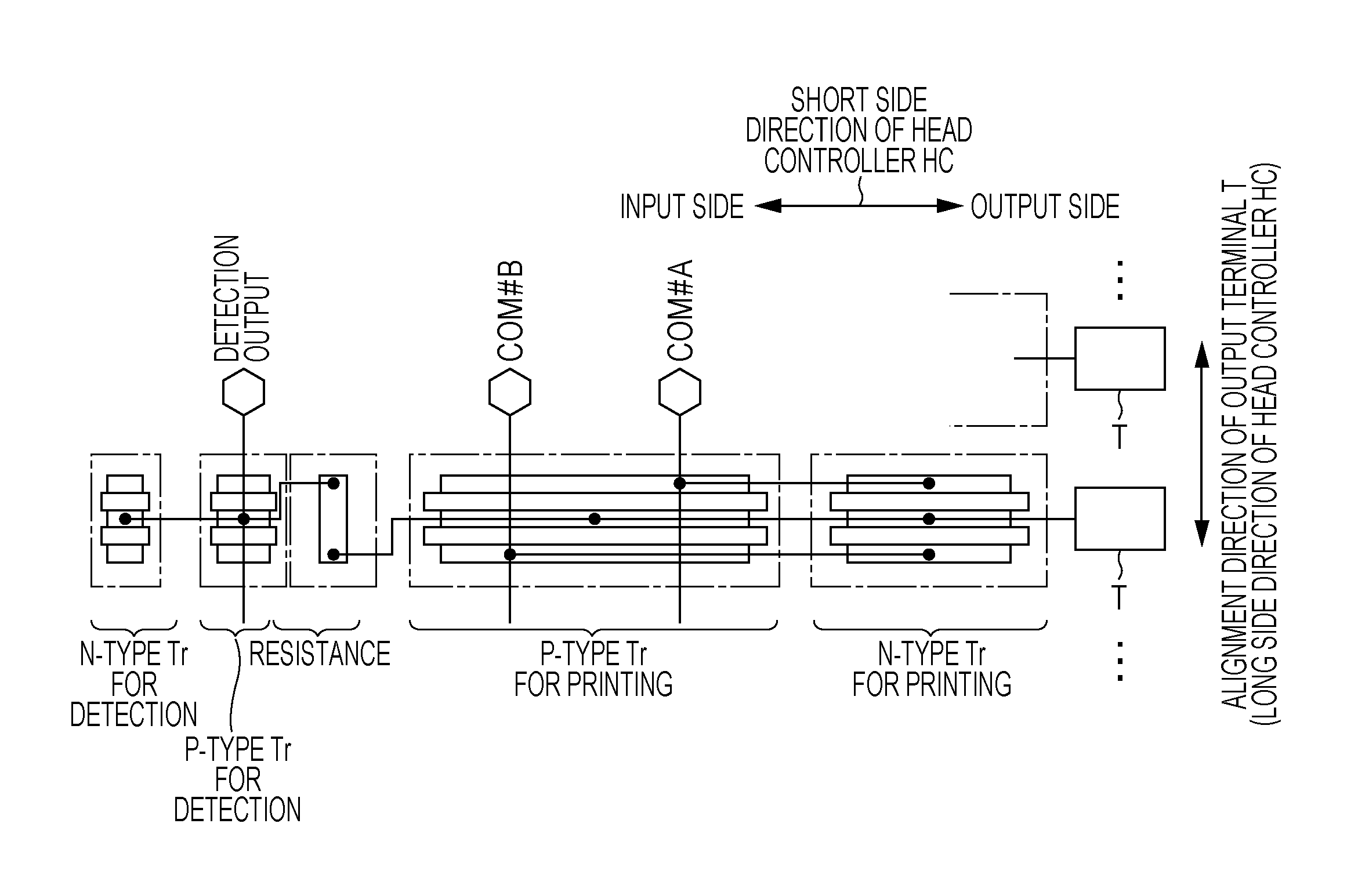

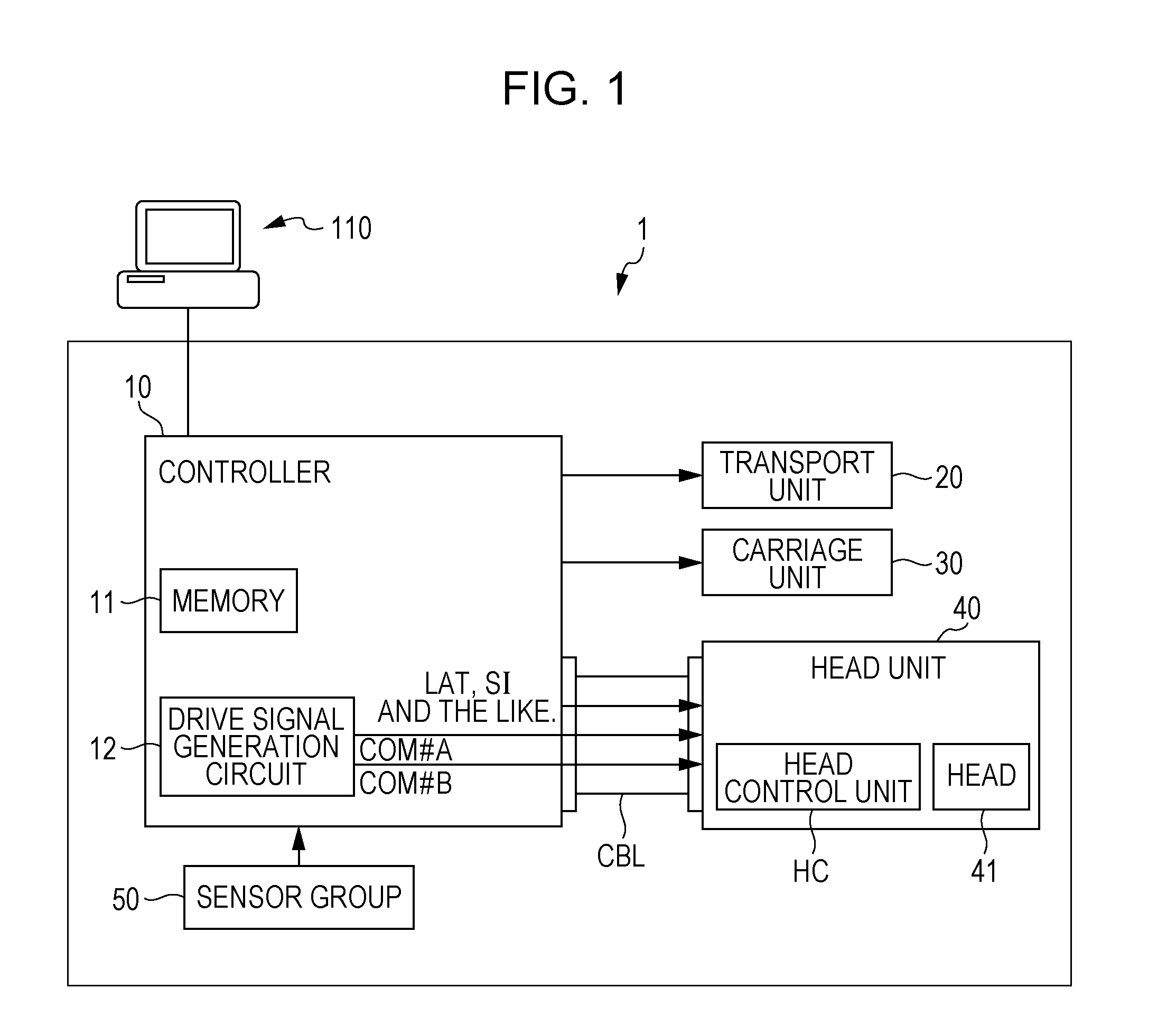

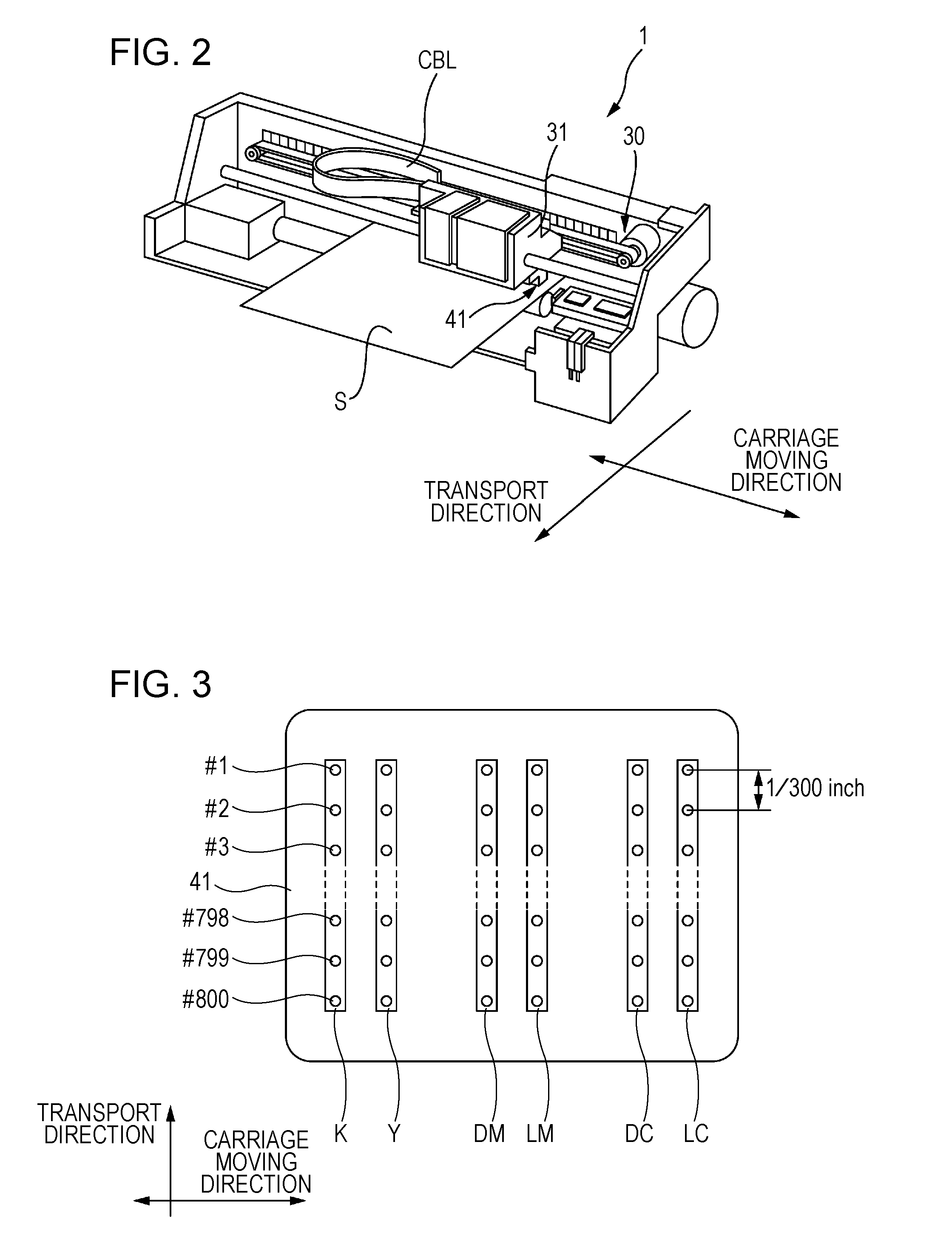

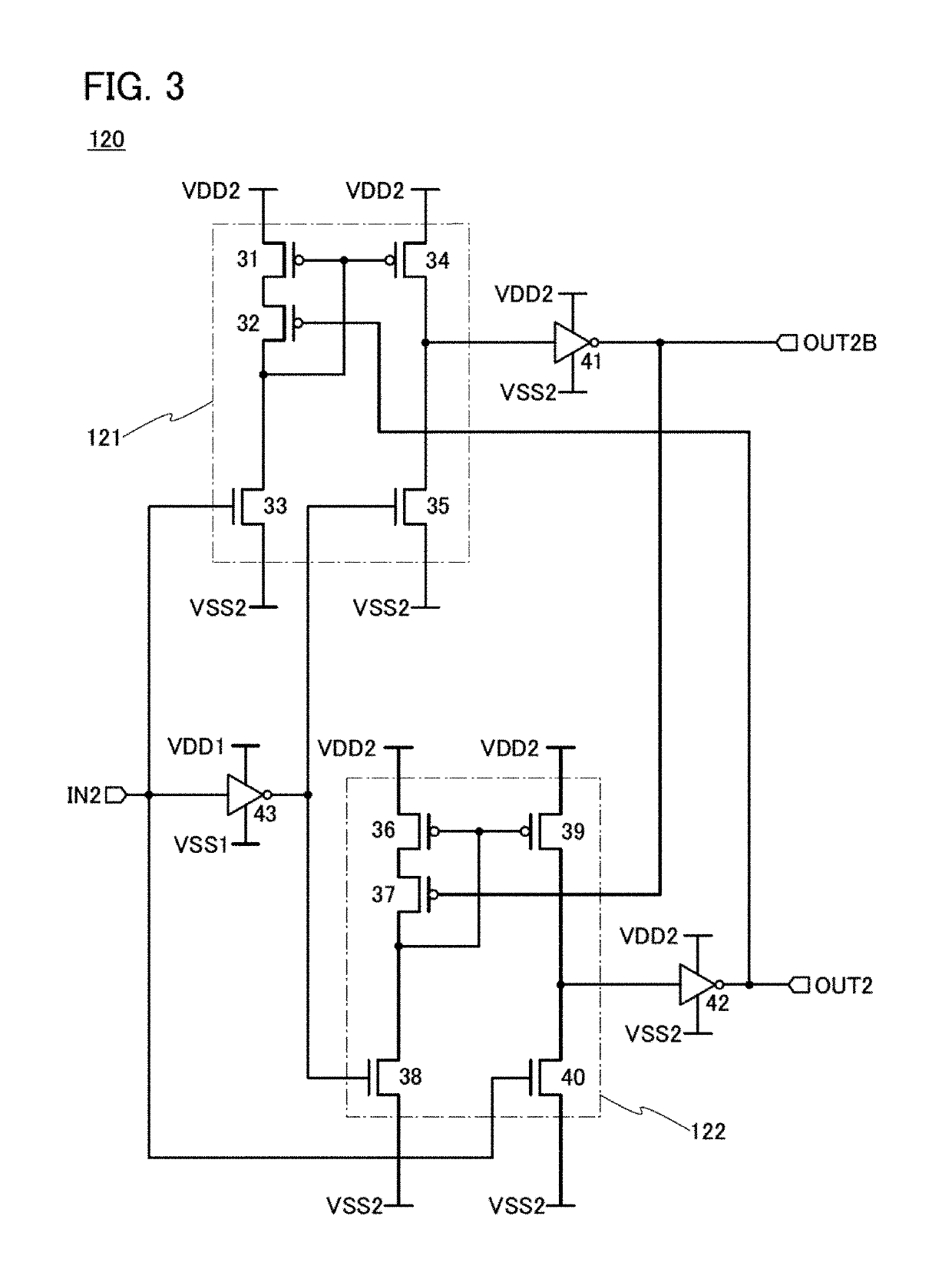

Semiconductor device, liquid discharge head, and liquid discharge apparatus

ActiveUS20150251415A1Efficiently provideIncrease in inhibition areaOther printing apparatusPower semiconductor deviceResidual vibration

A semiconductor device which is provided to correspond to each of a plurality of nozzles discharging a liquid and controls a plurality of drive elements causing a liquid to be discharged from each nozzle by an application of a drive signal includes a detection circuit which detects a residual vibration signal of the drive element, an output terminal which is provided to correspond to each of the plurality of drive elements, a discharge transistor which controls an application of the drive signal to the drive element through the output terminal, and a detection transistor which controls an application of the residual vibration signal to the detection circuit through the output terminal, in which the detection transistor is smaller than the discharge transistor in size, and the discharge transistor is disposed between the detection transistor and the output terminal.

Owner:SEIKO EPSON CORP

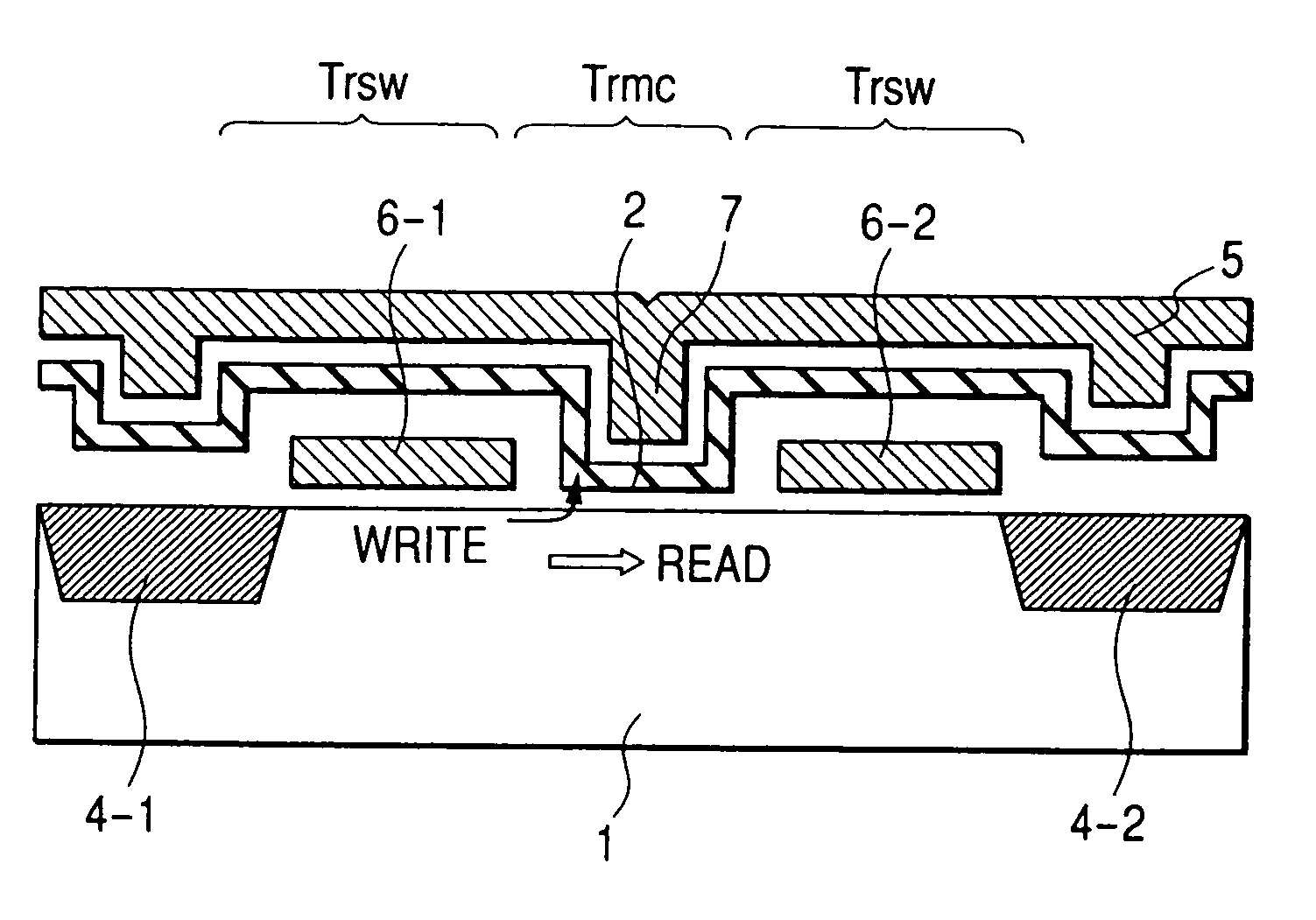

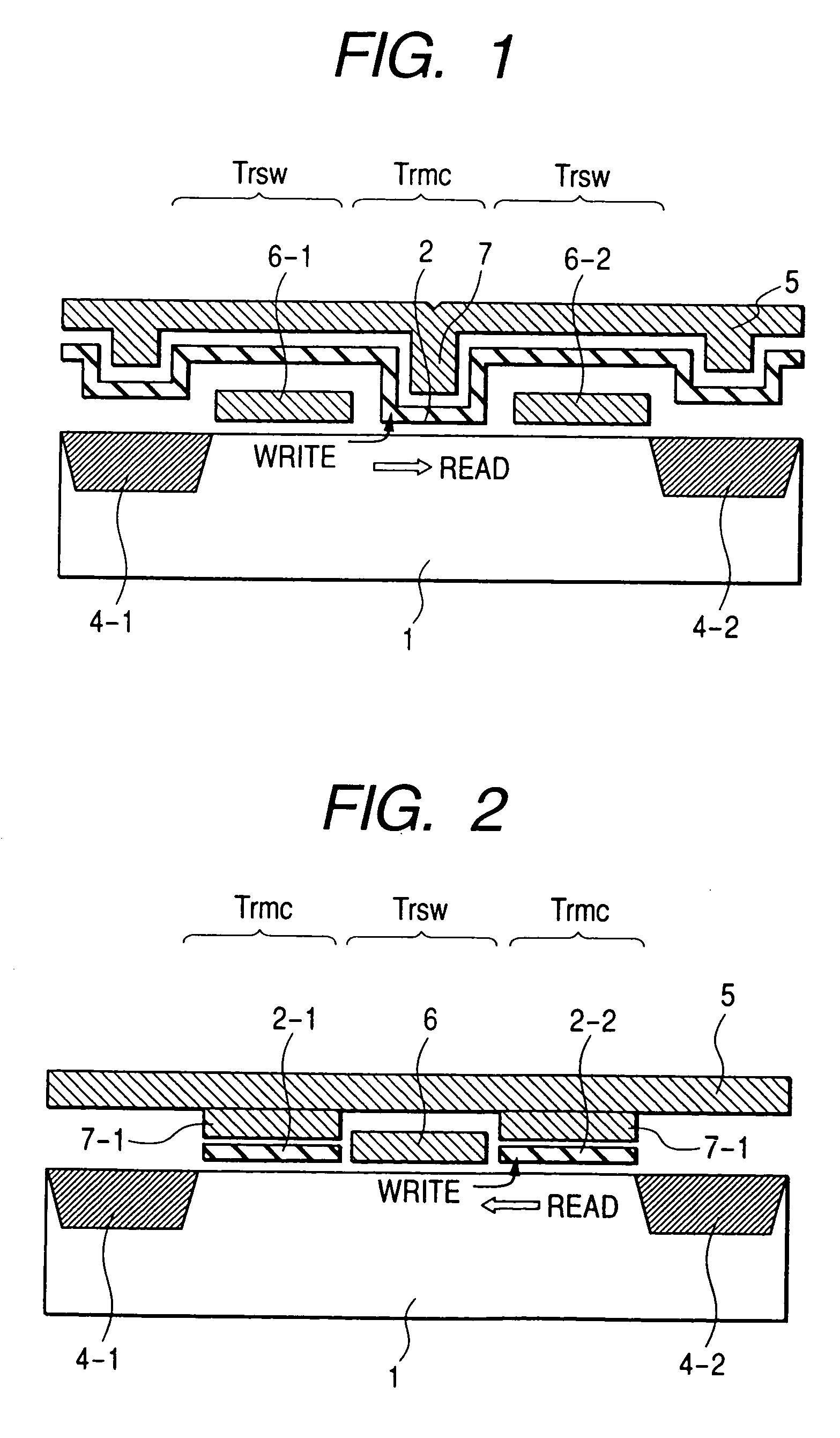

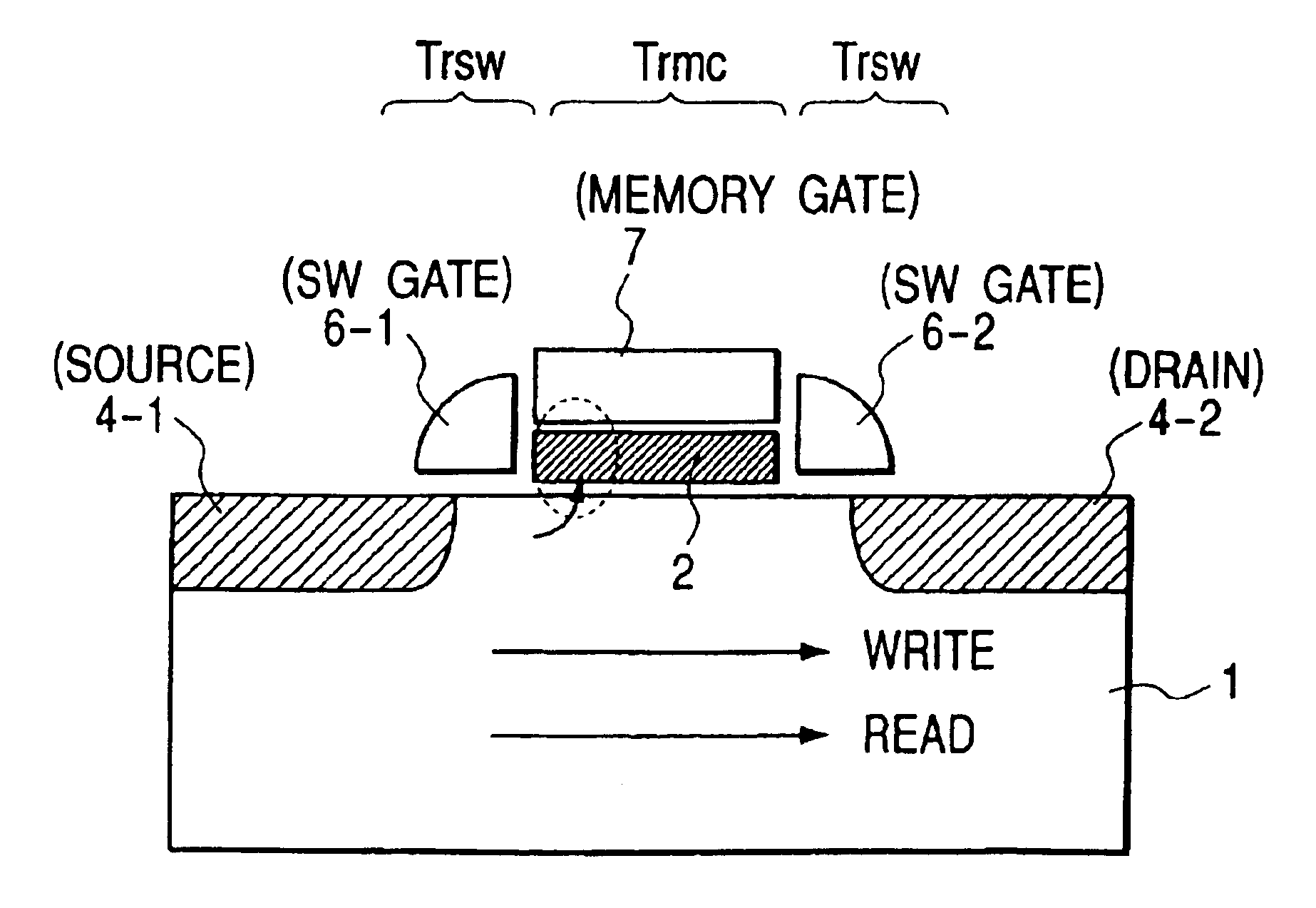

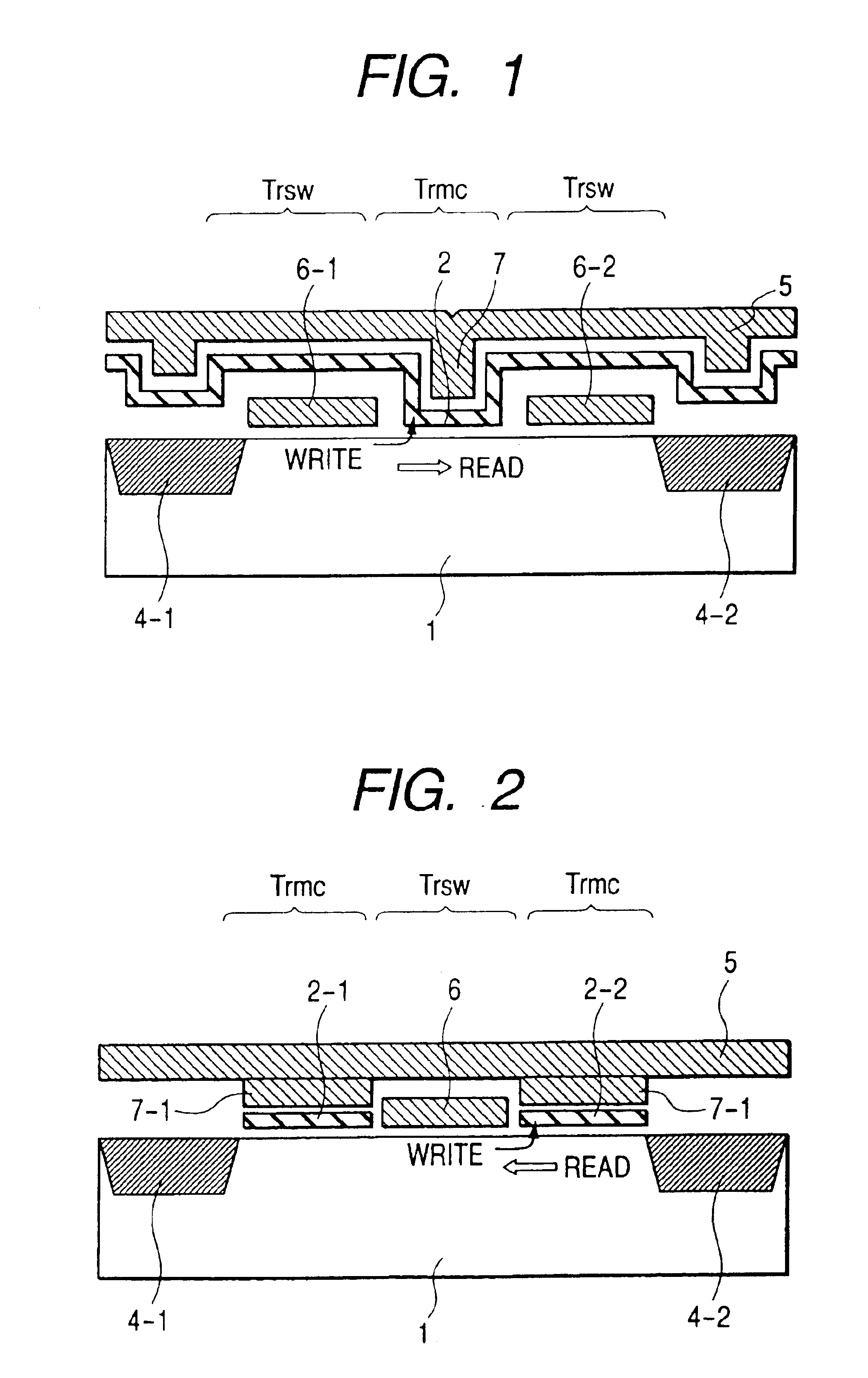

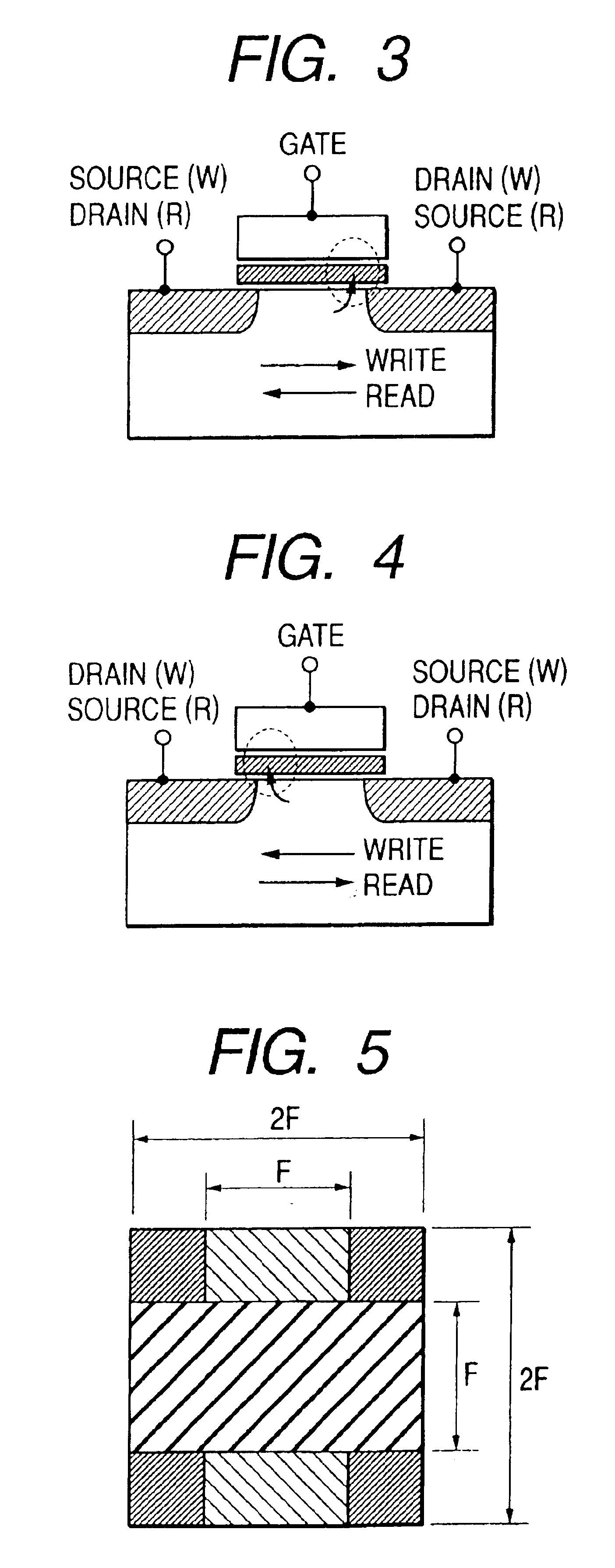

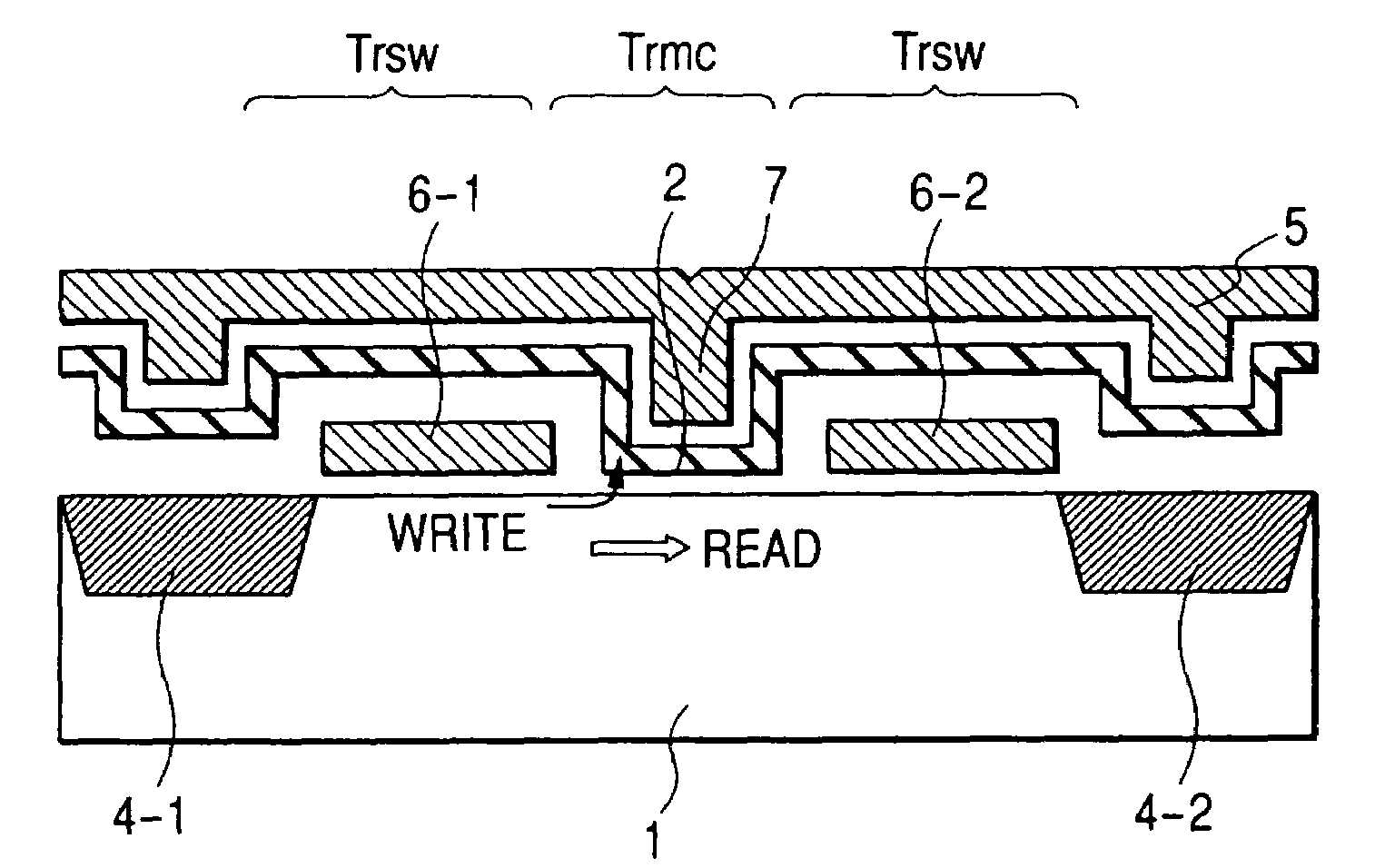

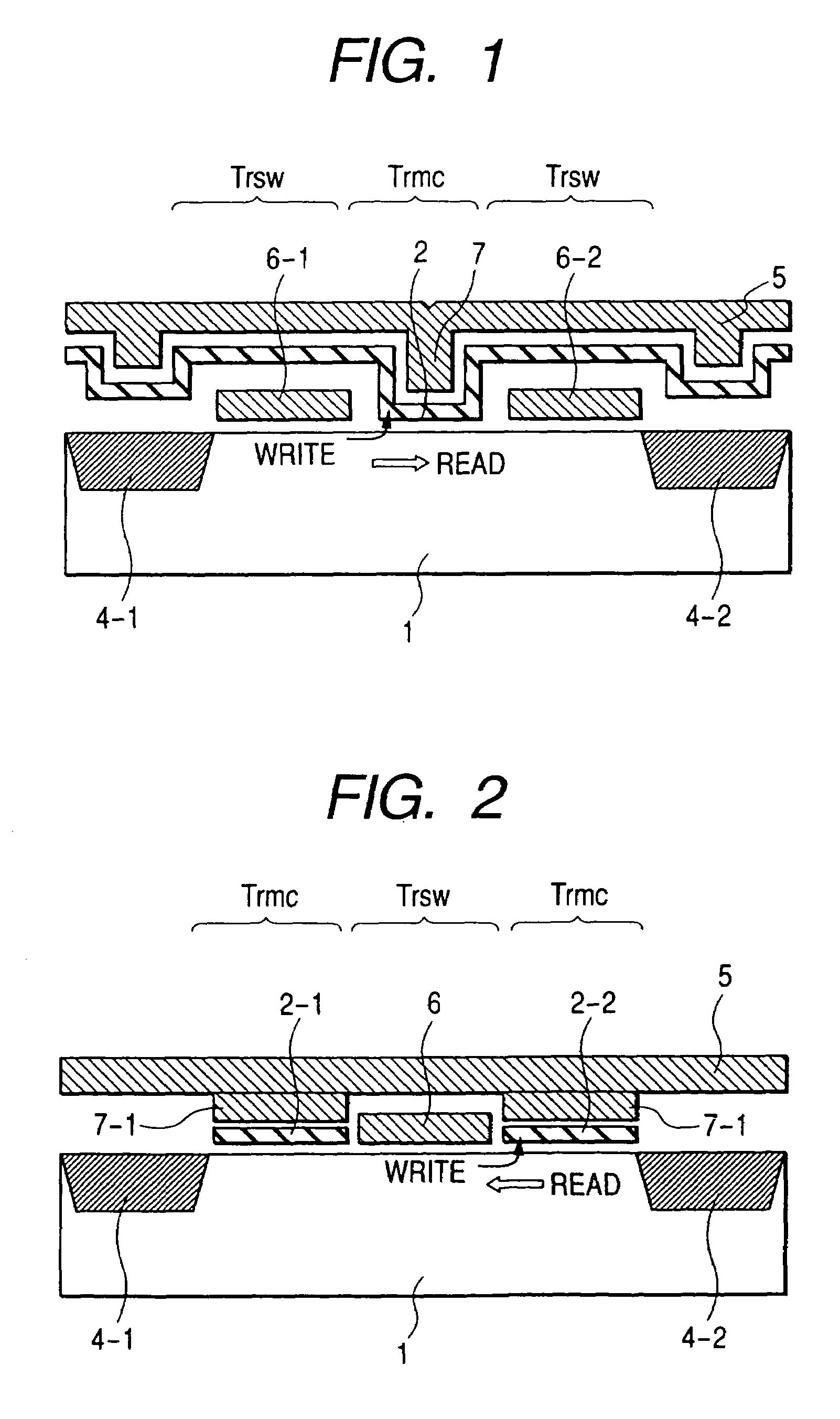

Semiconductor integrated circuit

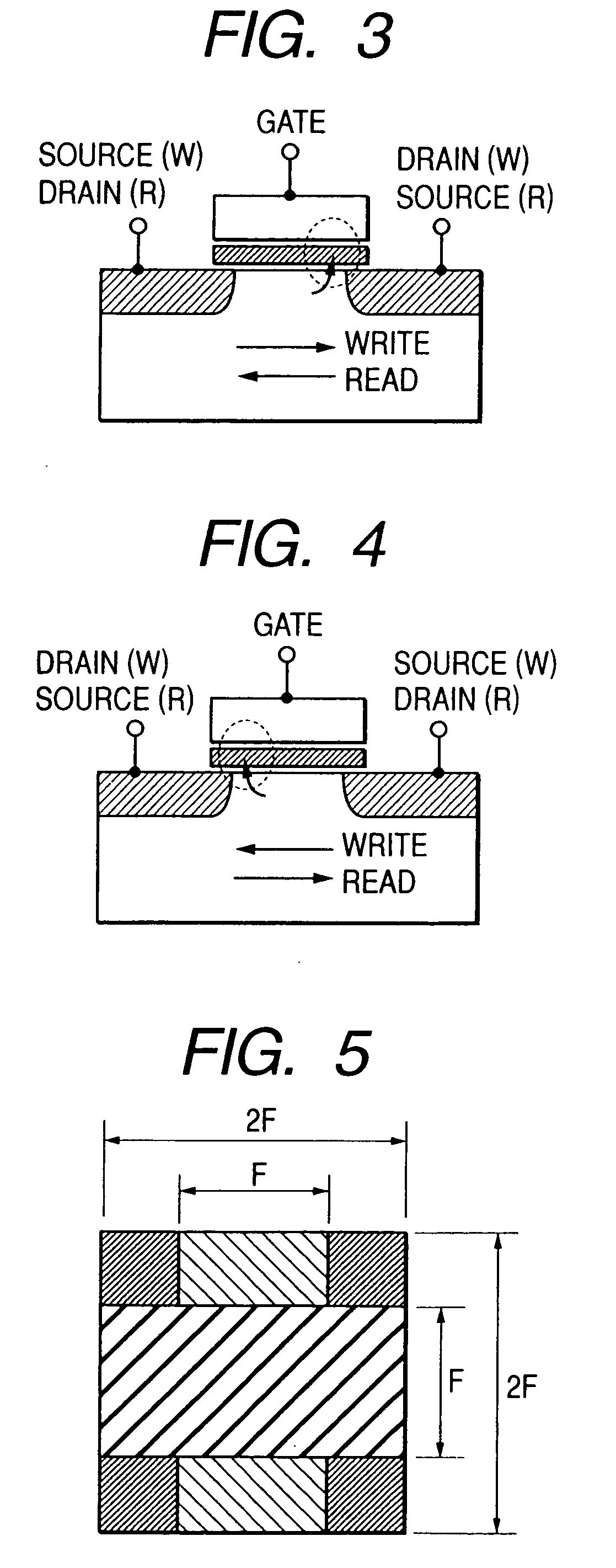

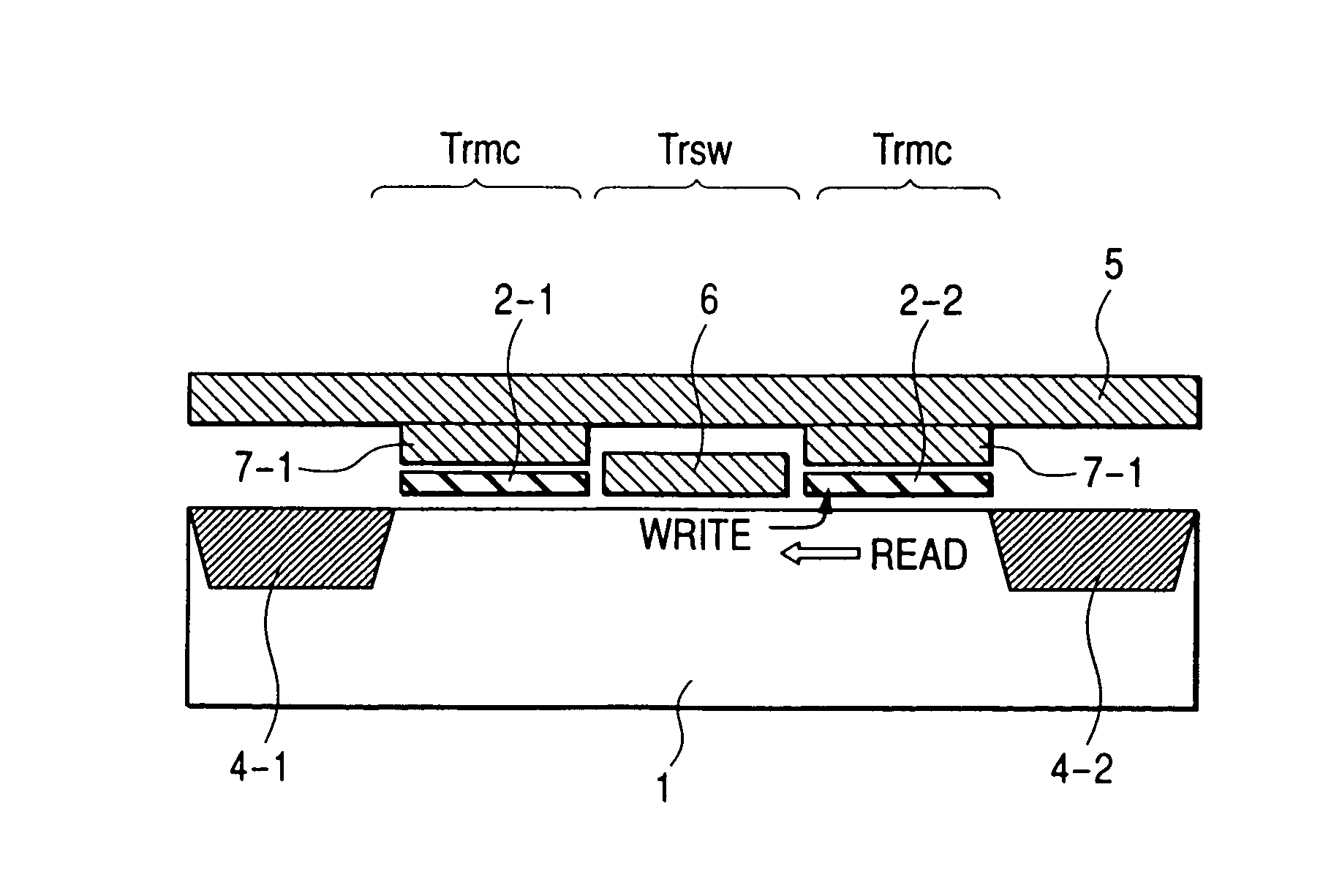

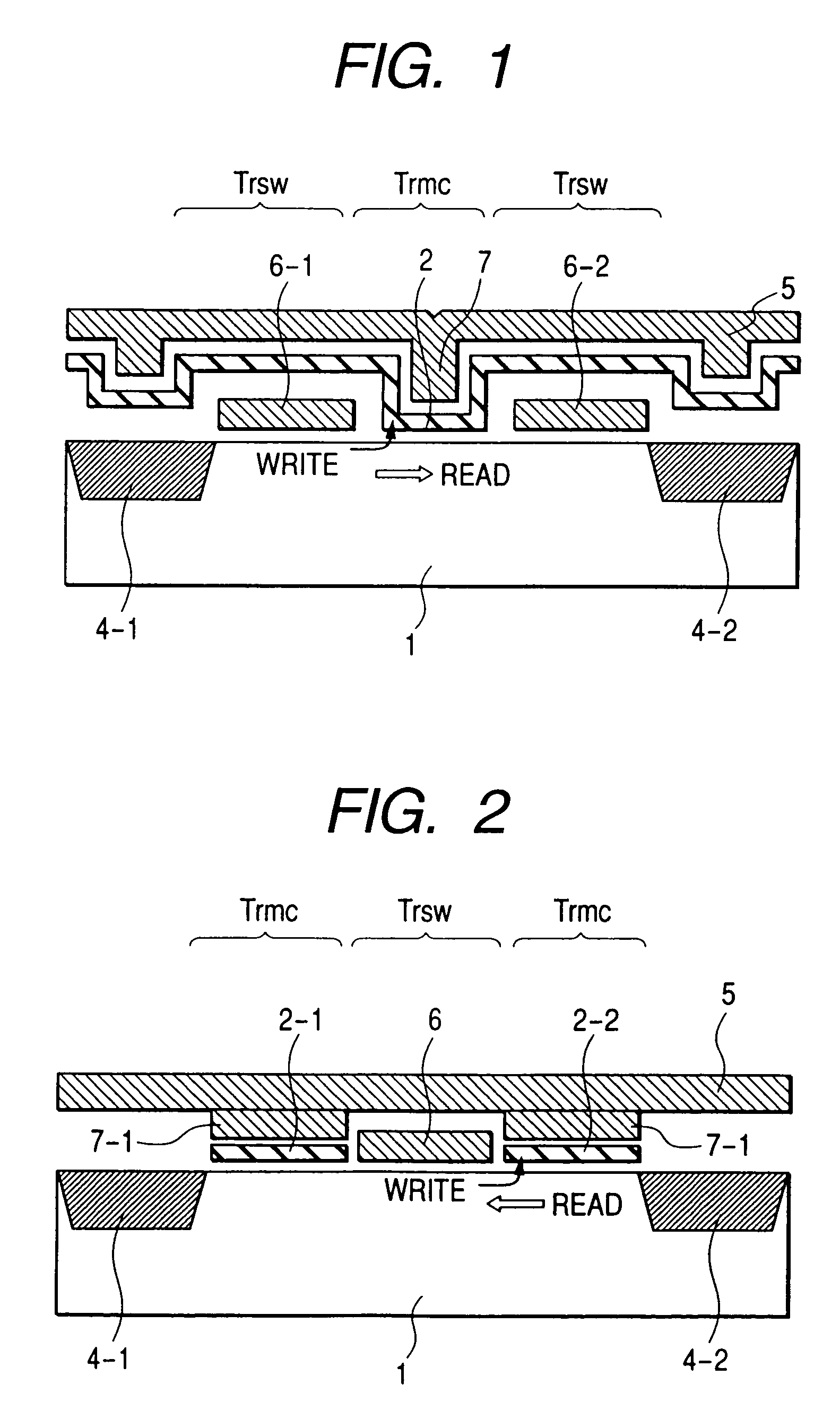

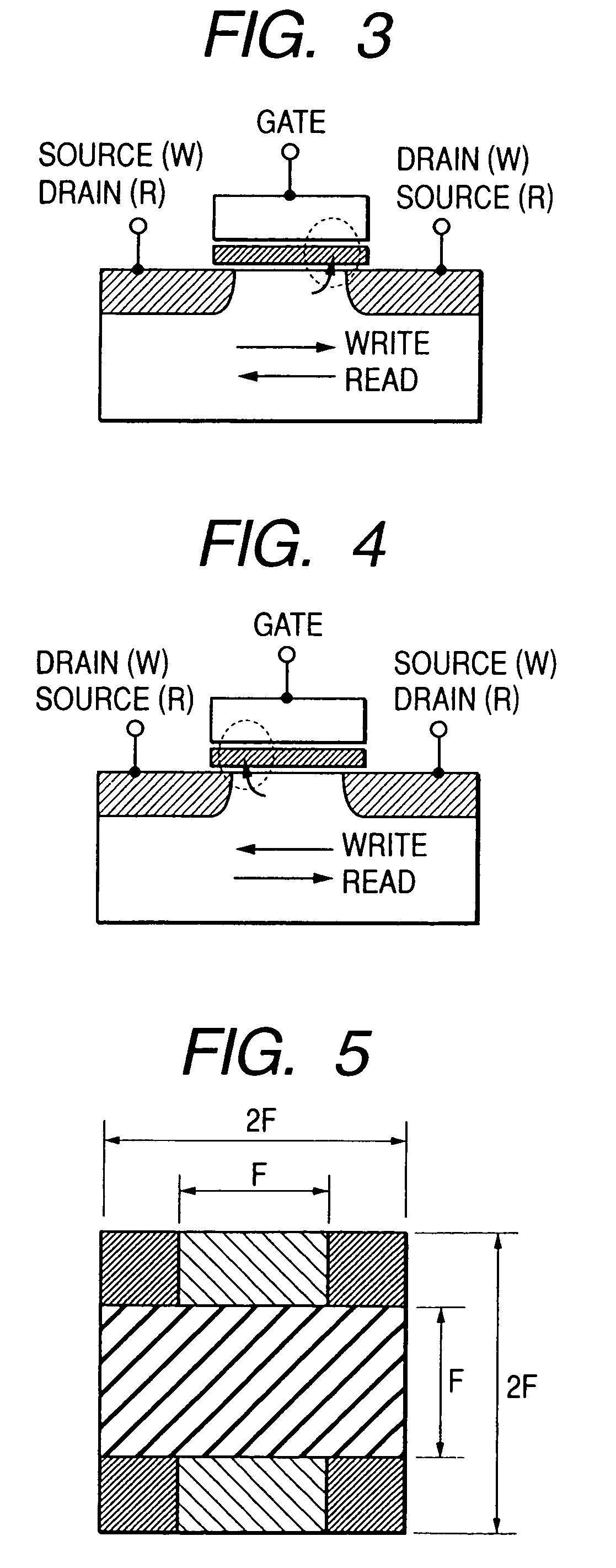

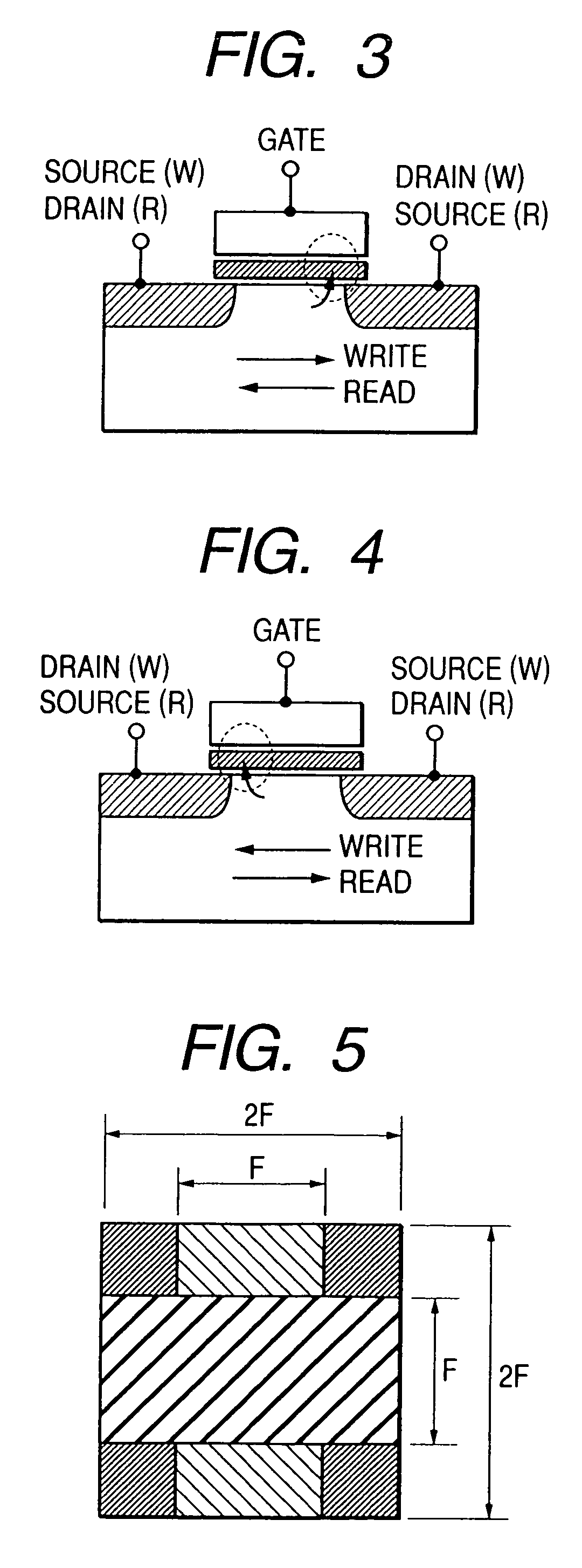

InactiveUS20050219900A1Reduce stored chargeImprove programming efficiencyTransistorRead-only memoriesHigh densityEngineering

A multi-storage nonvolatile memory of high density, high speed and high reliability has a memory transistor and switch transistors disposed on both the sides of the memory transistor. The memory transistor includes a gate insulating film having discrete traps and a memory gate electrode, whereas the switch transistors include switch gate electrodes. The gate insulating film has the discrete traps for storing information charge, can locally inject carriers, and one memory cell constitutes a multi-storage cell for storing at least information of 2 bits. The switch transistors having the switch gate electrodes realize source side injection. The memory transistor is fommed together with the switch transistors in self-aligned diffusion. The memory gate electrode of the memory transistor is connected to a word line so as to perform word-line erase.

Owner:RENESAS ELECTRONICS CORP

Semiconductor integrated circuit

Owner:RENESAS ELECTRONICS CORP

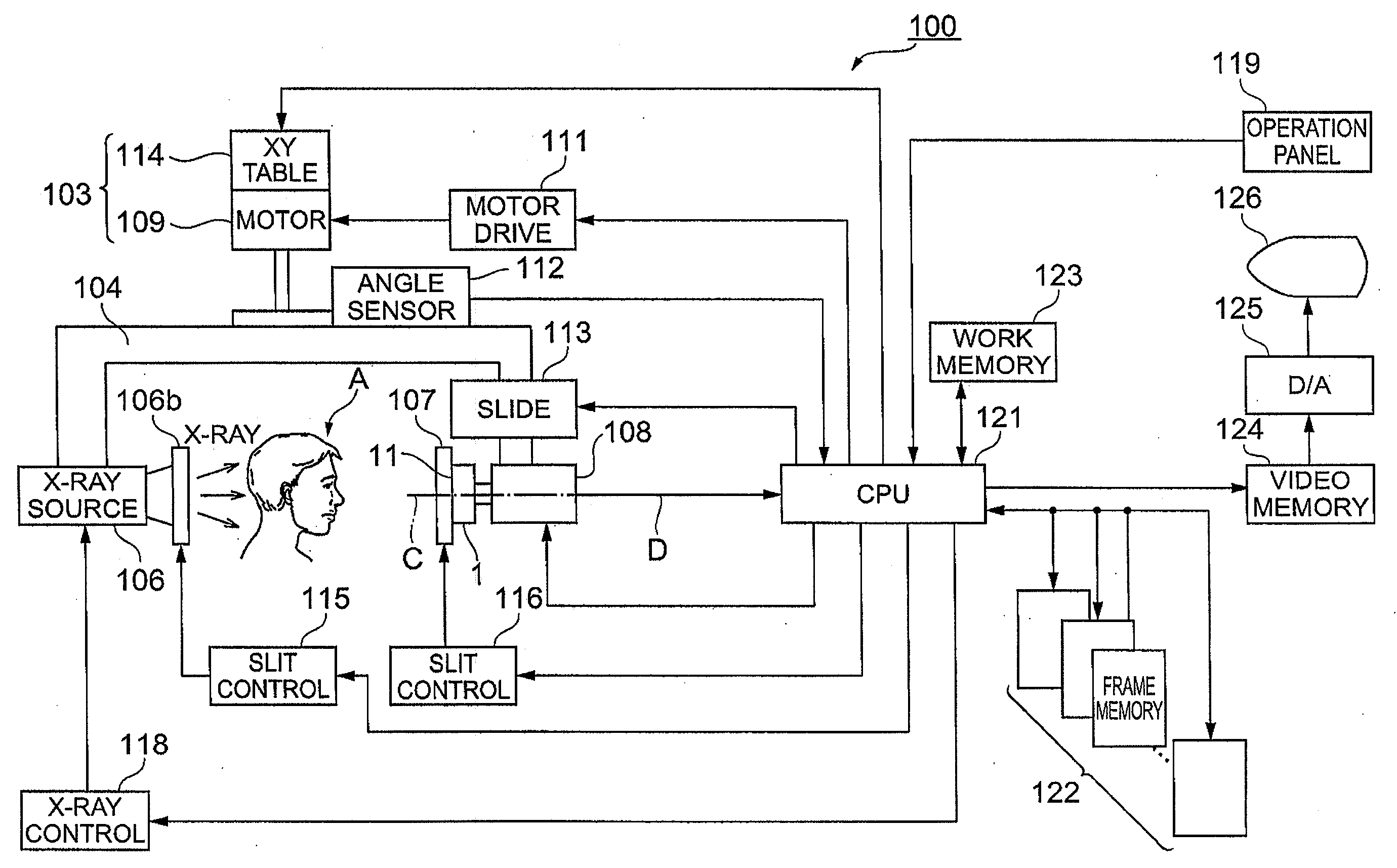

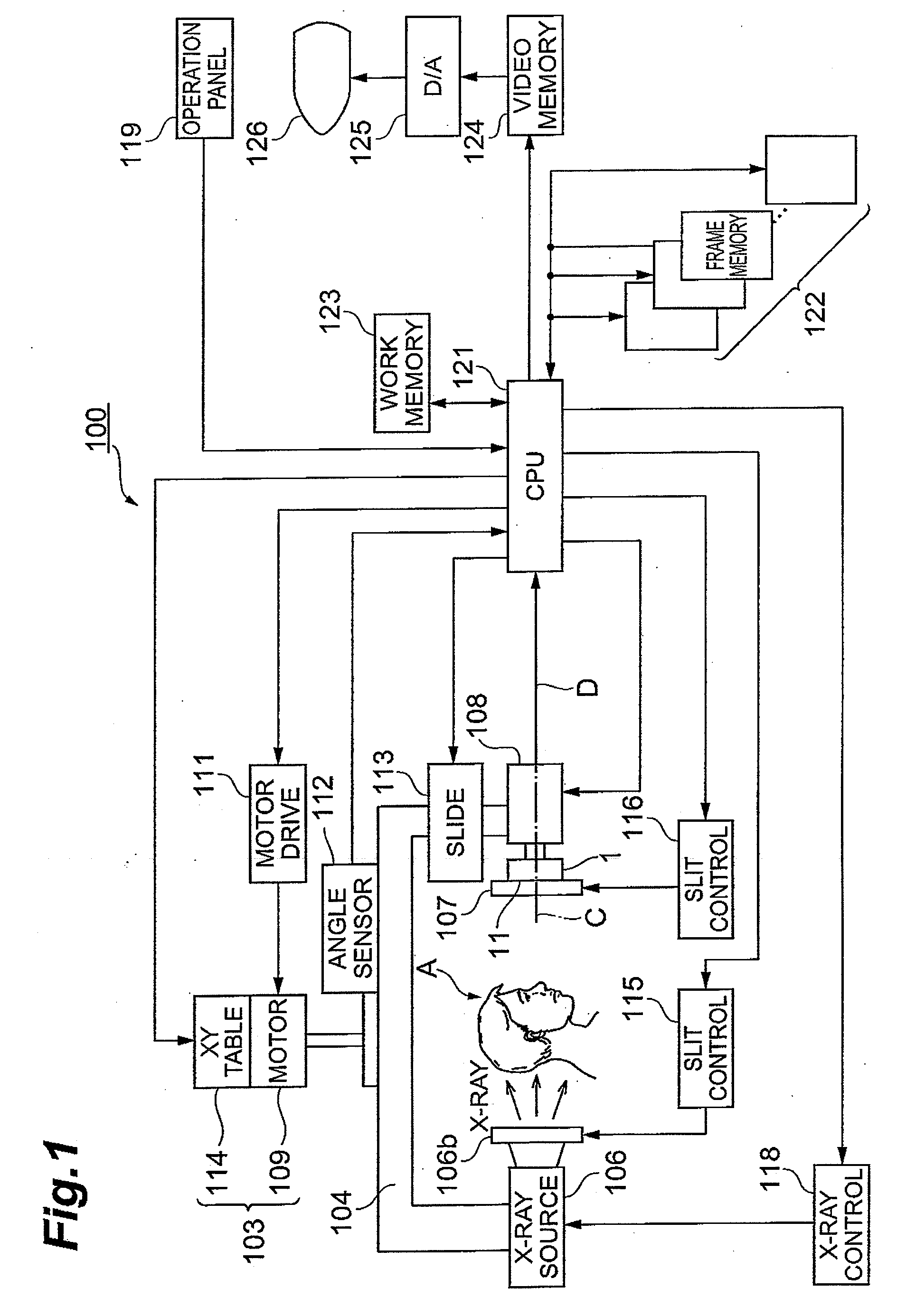

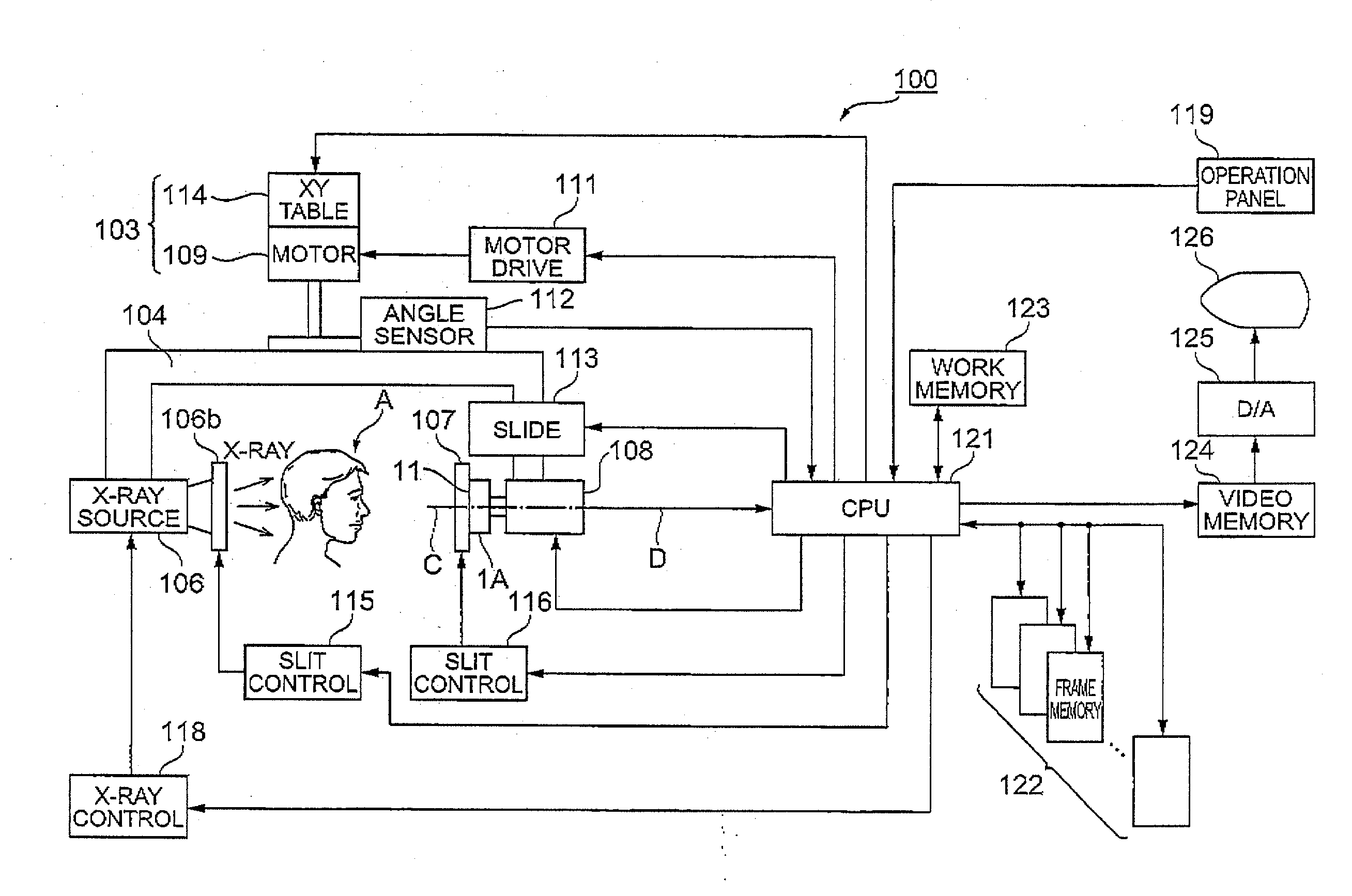

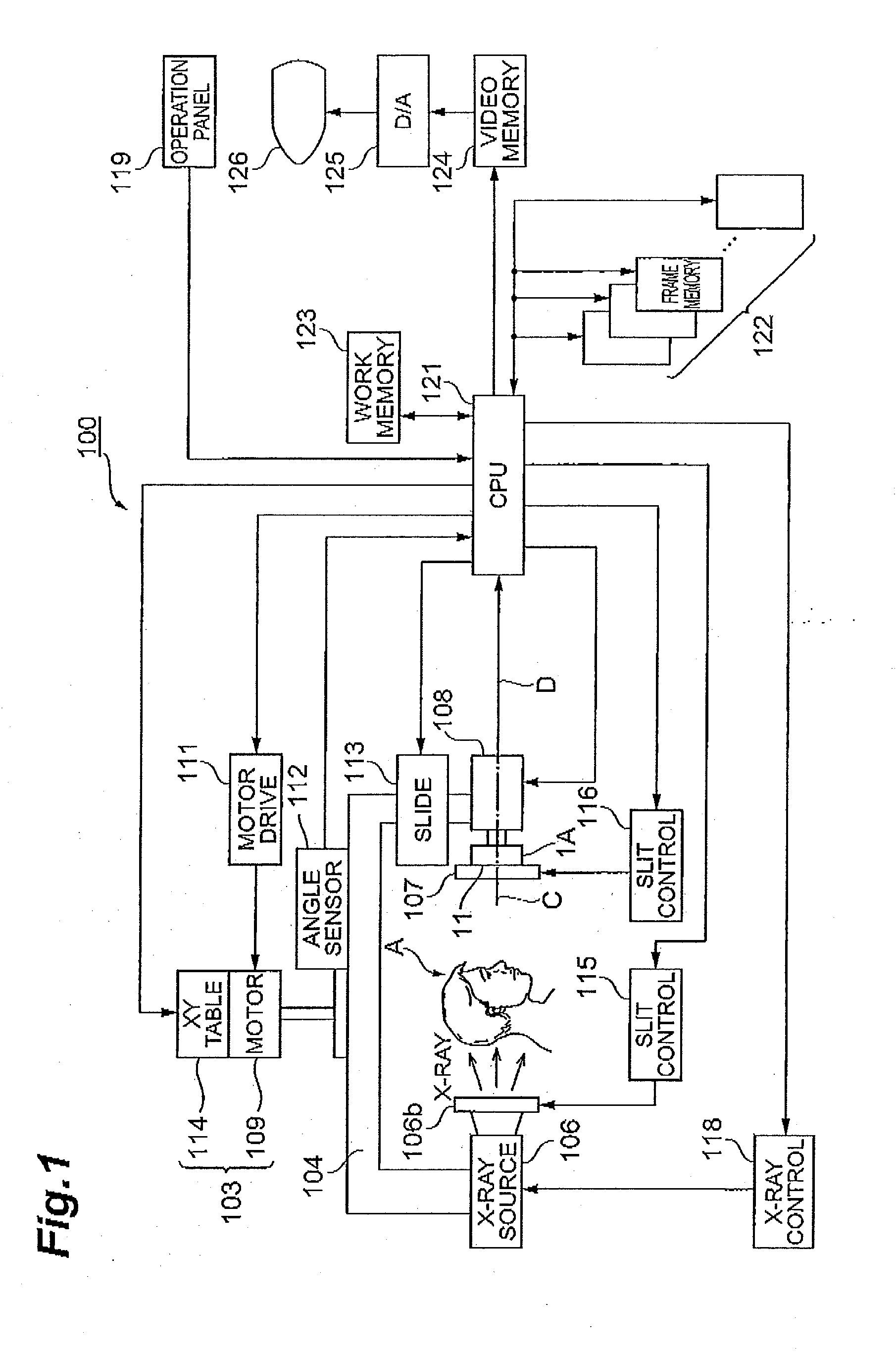

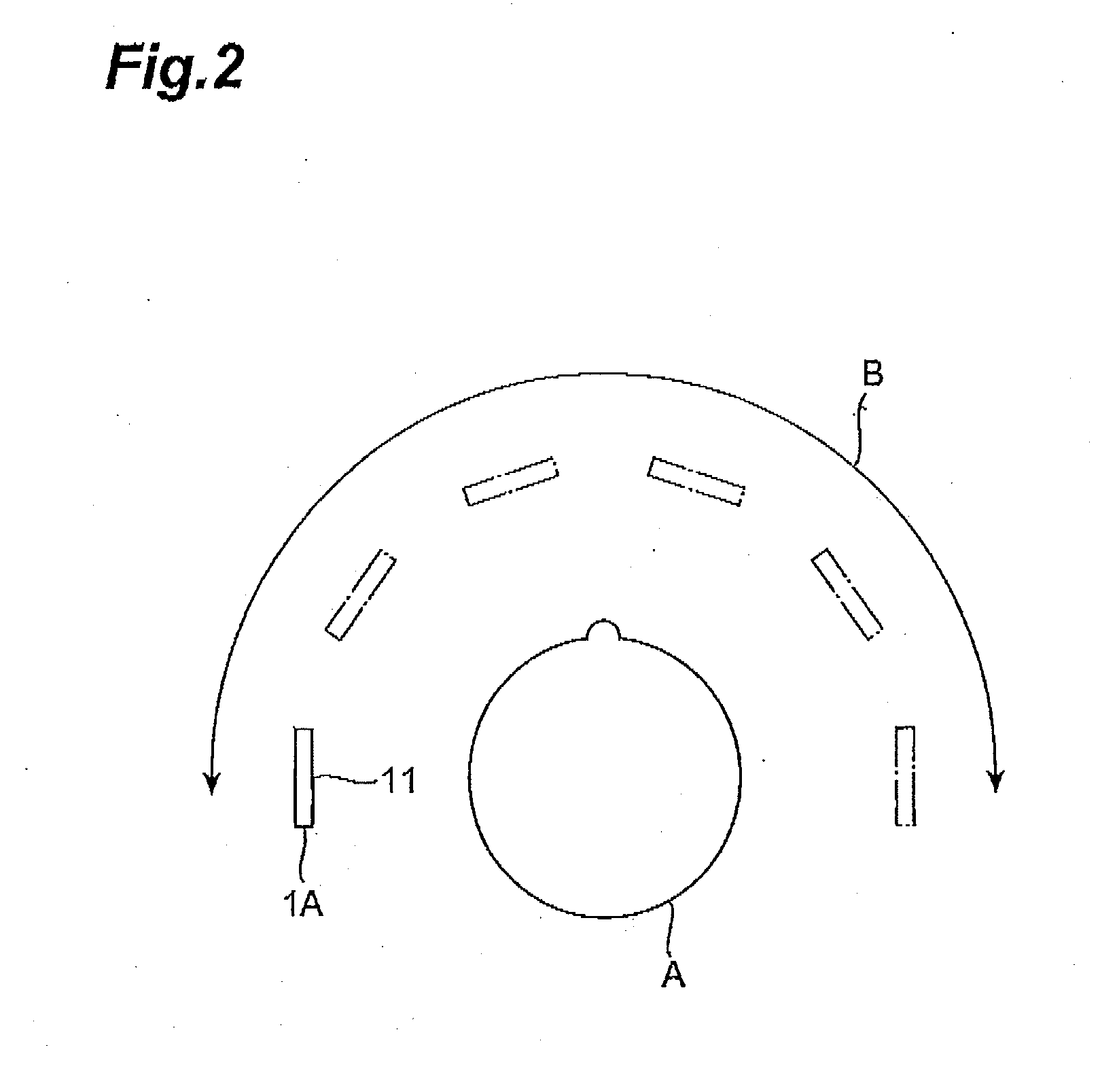

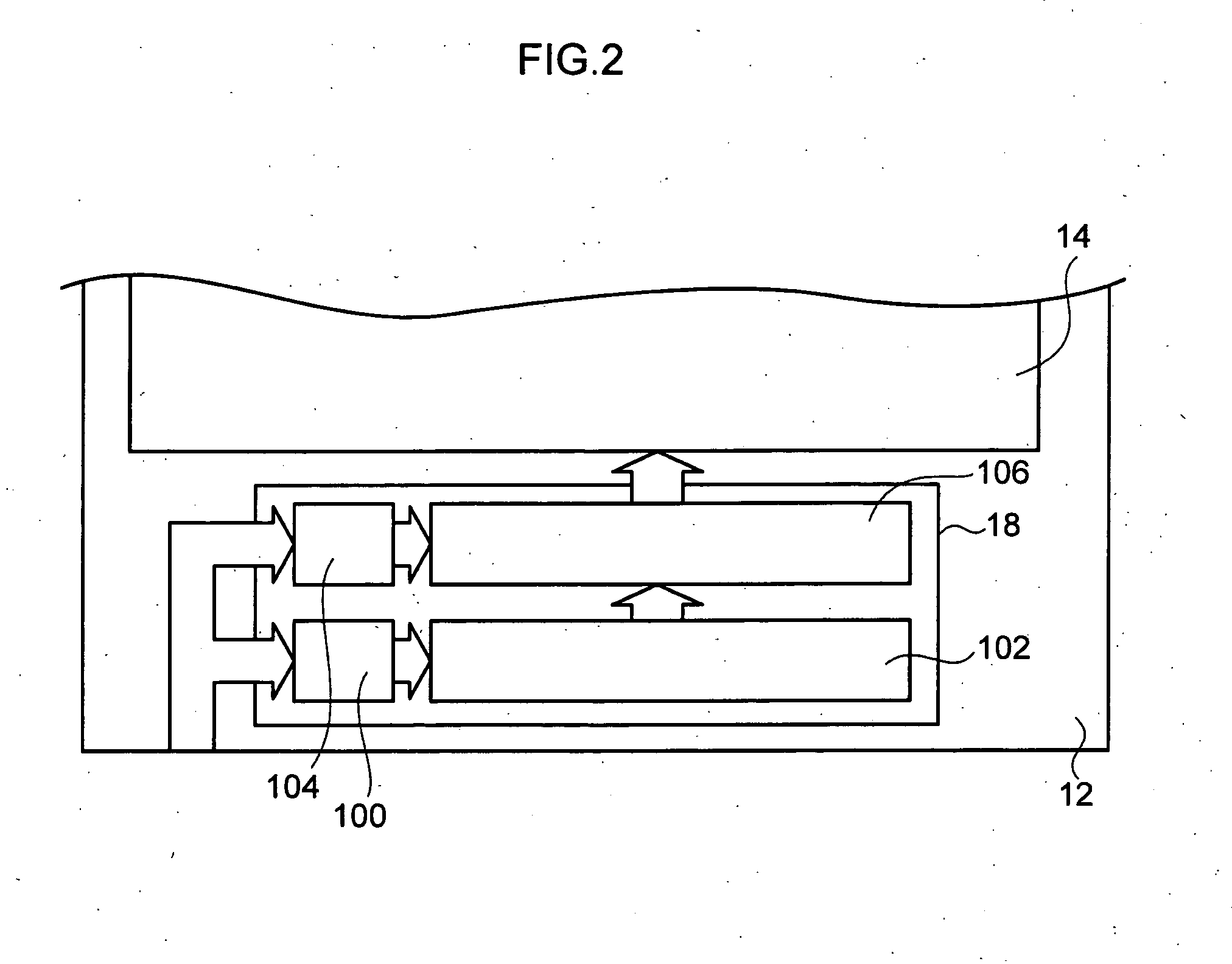

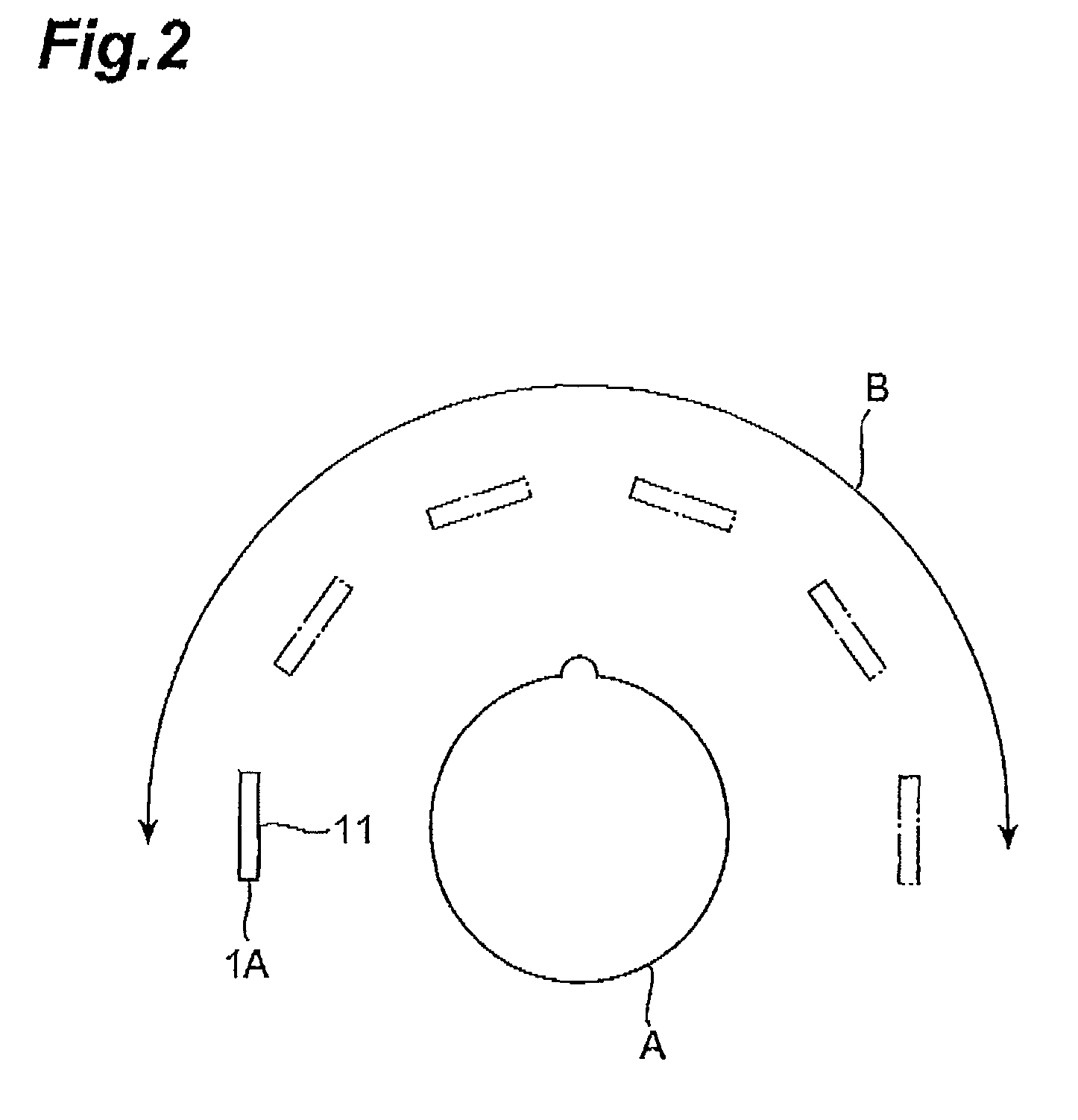

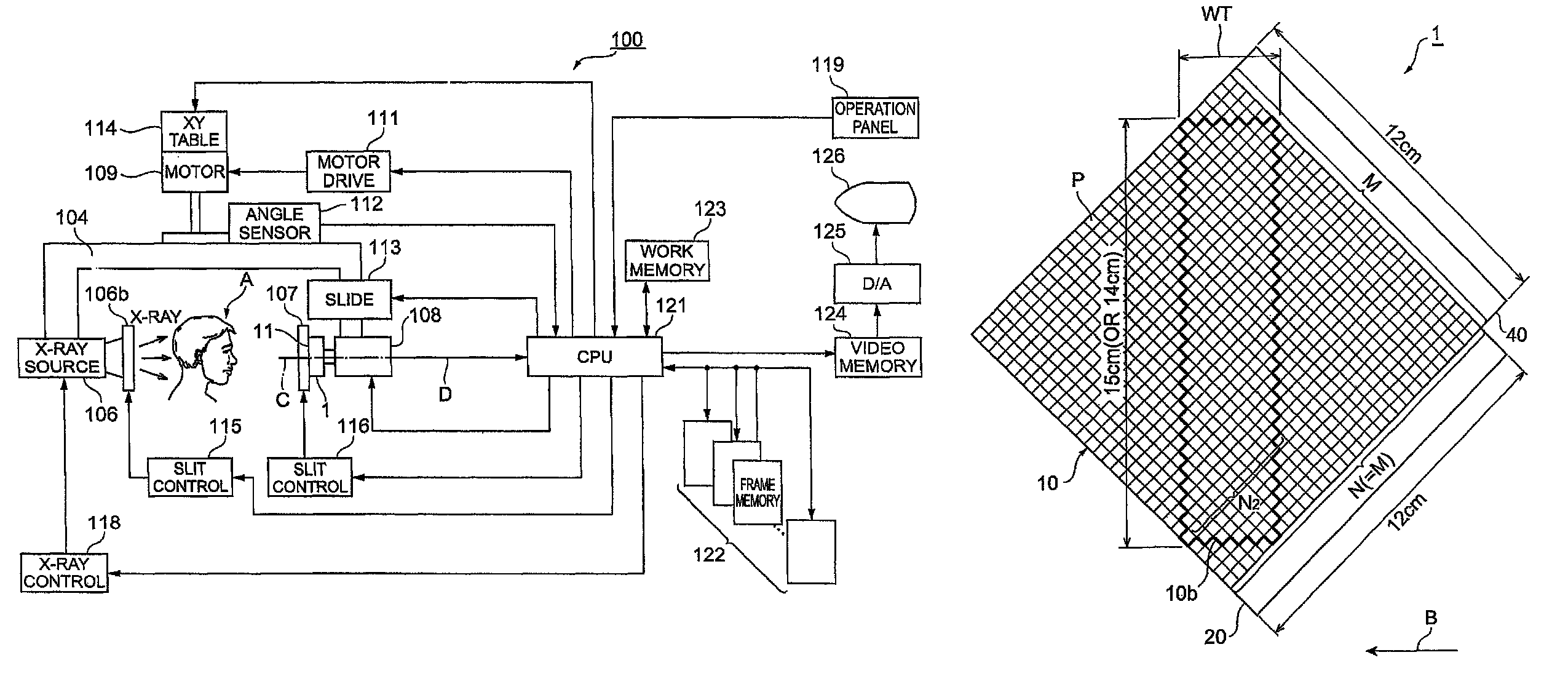

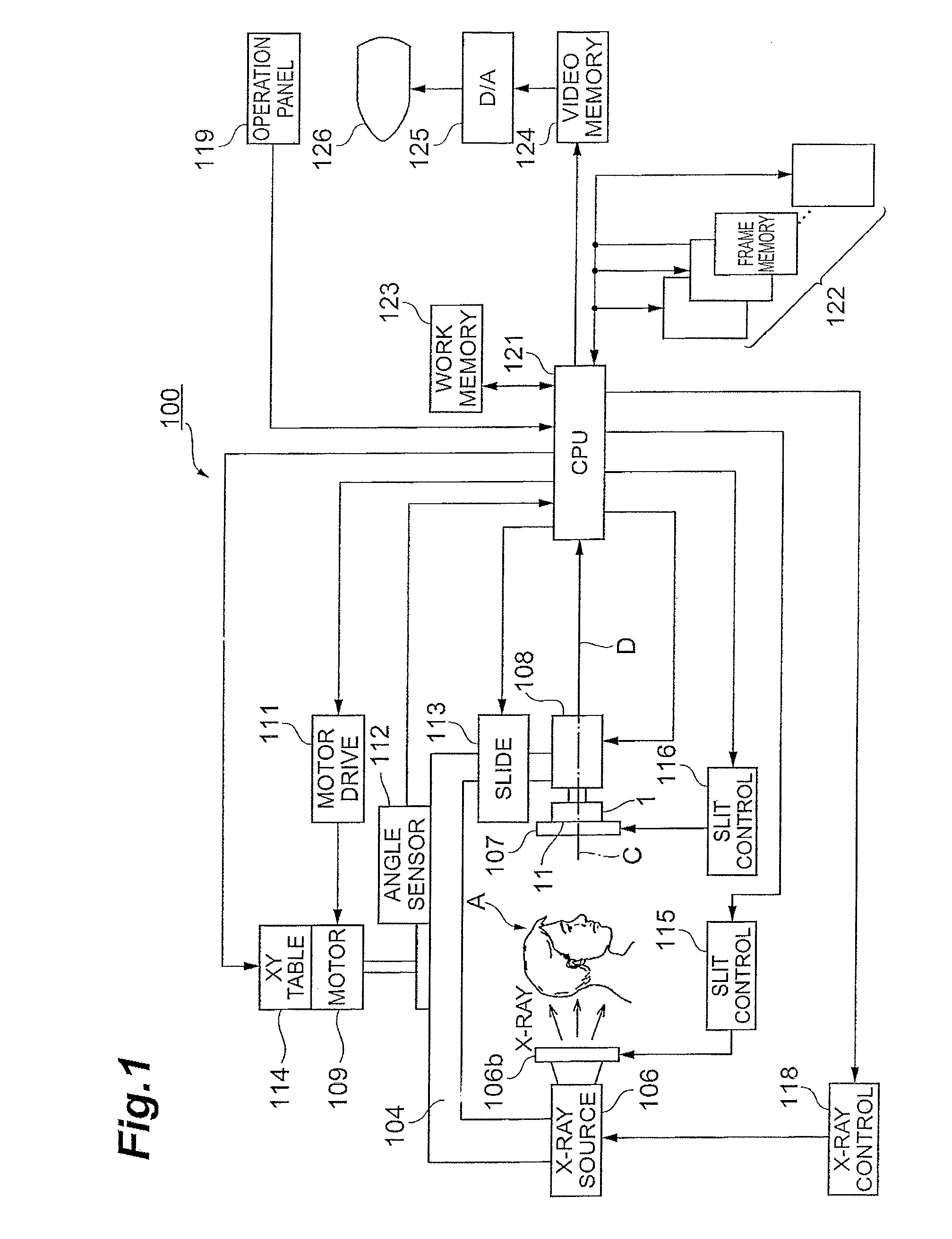

Medical x-ray imaging system

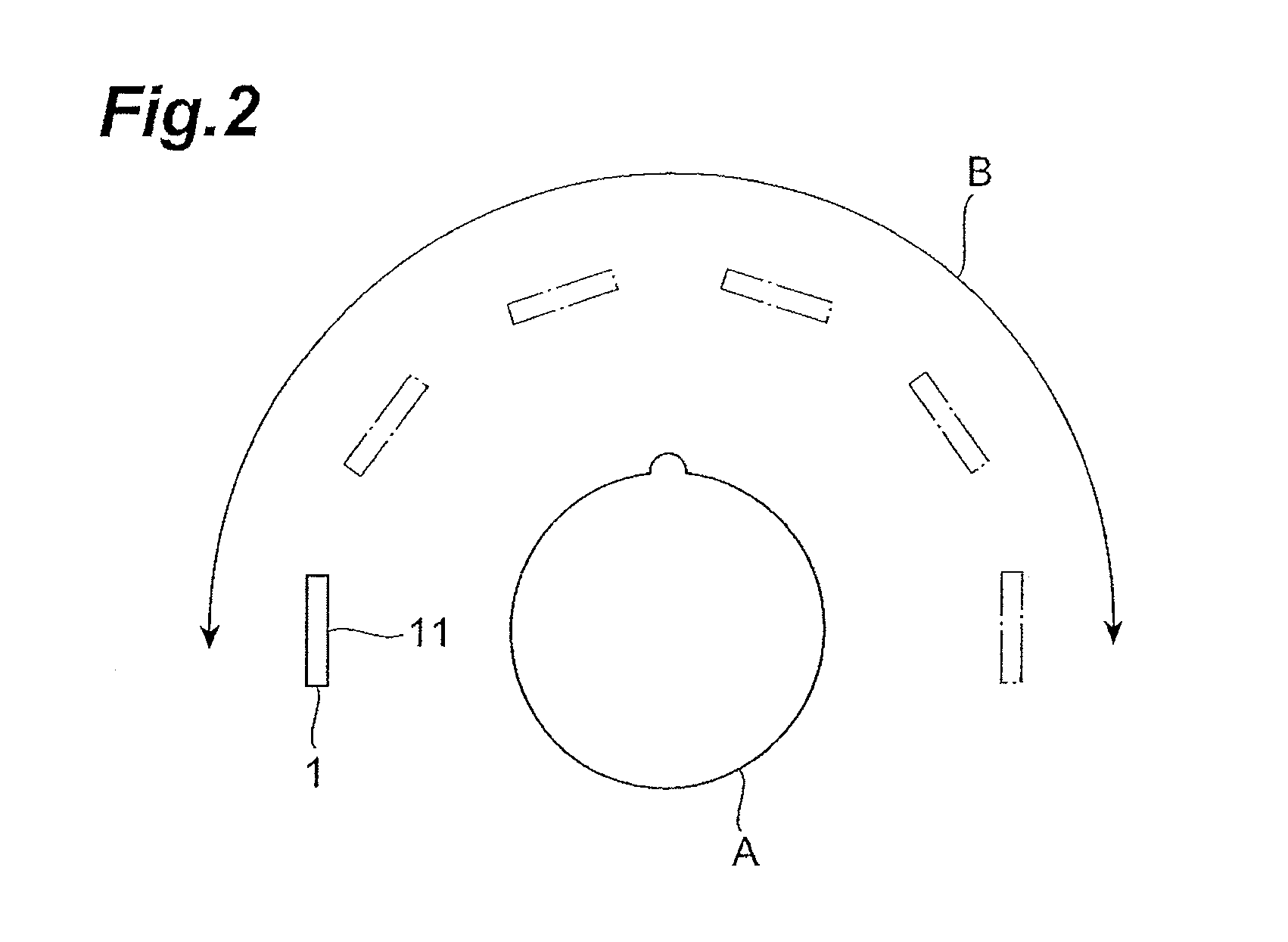

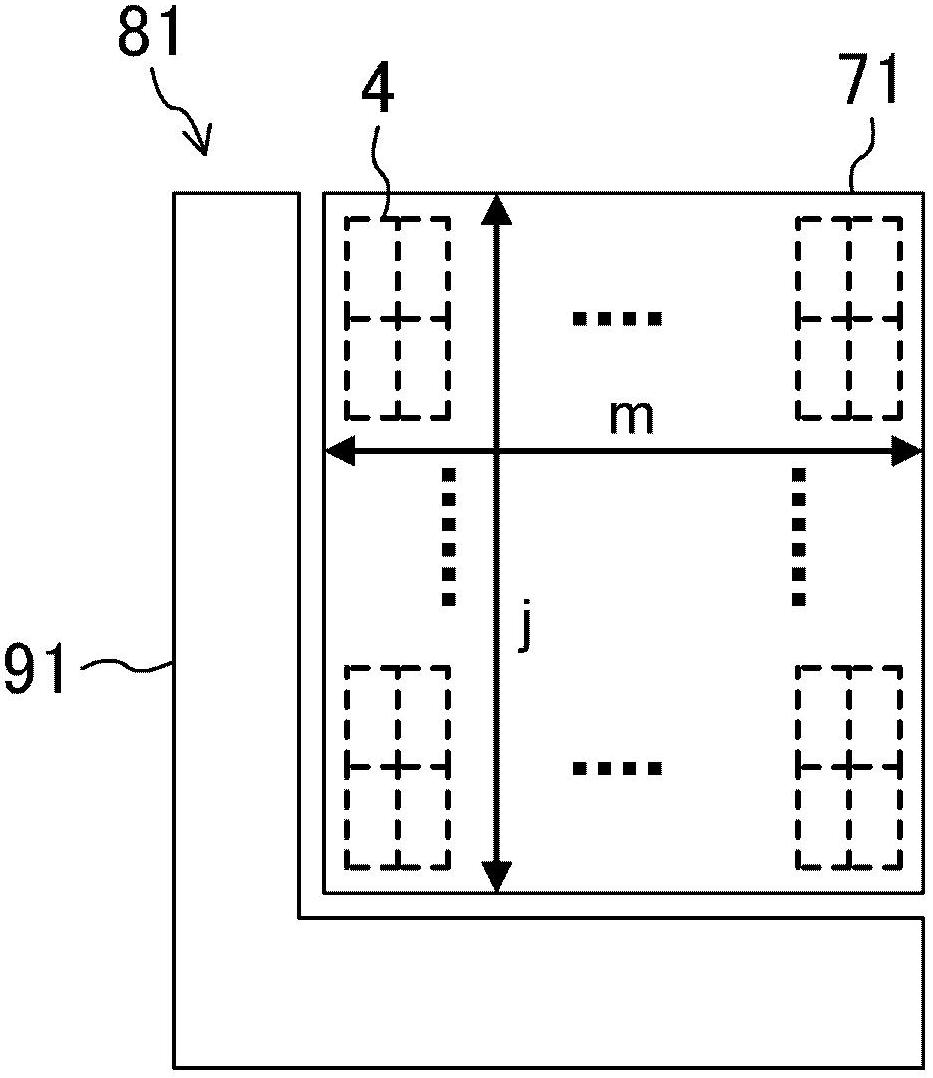

ActiveUS20090268867A1Reduce in quantityIncrease frame rateTelevision system detailsX/gamma/cosmic radiation measurmentX-rayEngineering

The solid-state image pick-up device (1) includes a photodetecting section (10) which is formed by two-dimensionally aligning M×N (M and N are integers not less than 2) pixels in M rows and N columns and has a rectangular photodetecting surface. This solid-state image pick-up device (1) is supported rotatably by a rotation controlling section, and the rotation controlling section controls the rotation angle of the solid-state image pick-up device (1) so that the row direction or column direction of the photodetecting section (10) becomes parallel to the movement direction (B) of the solid-state image pick-up device (1) in one of the two imaging modes, and both of the row direction and the column direction of the photodetecting section (10) tilt with respect to the movement direction (B) of the solid-state image pick-up device (1) in the other imaging mode of the two imaging modes.

Owner:HAMAMATSU PHOTONICS KK

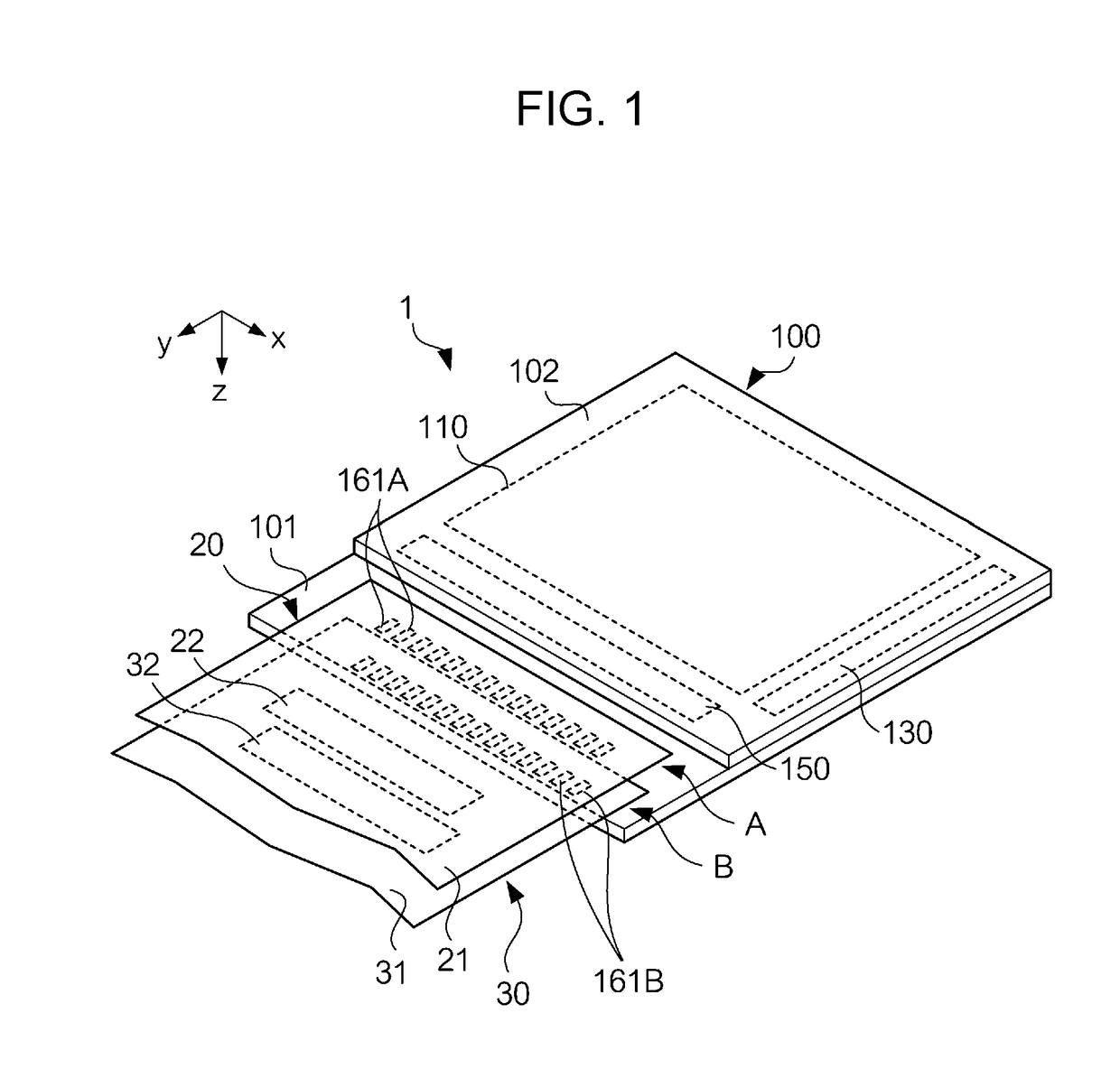

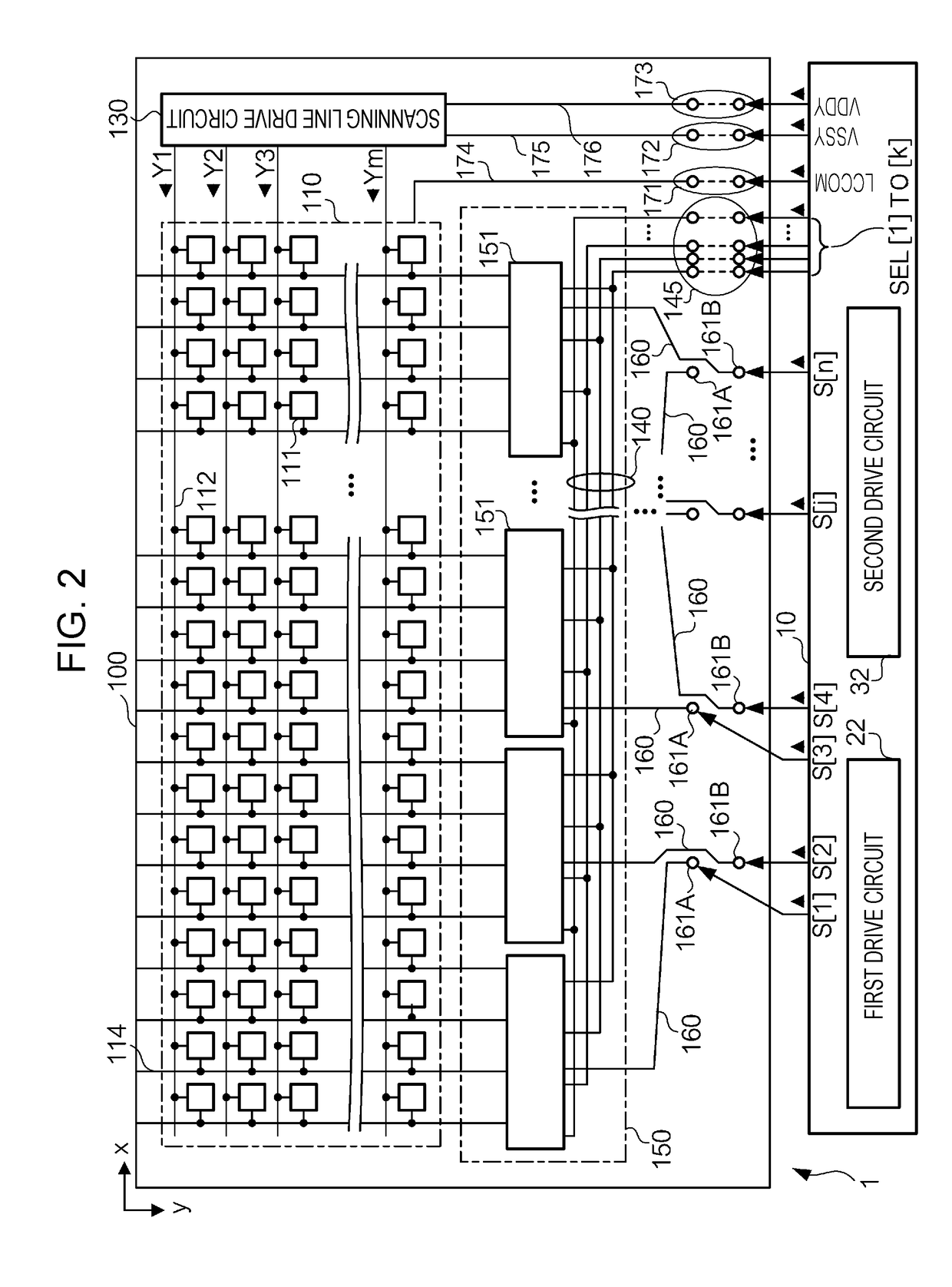

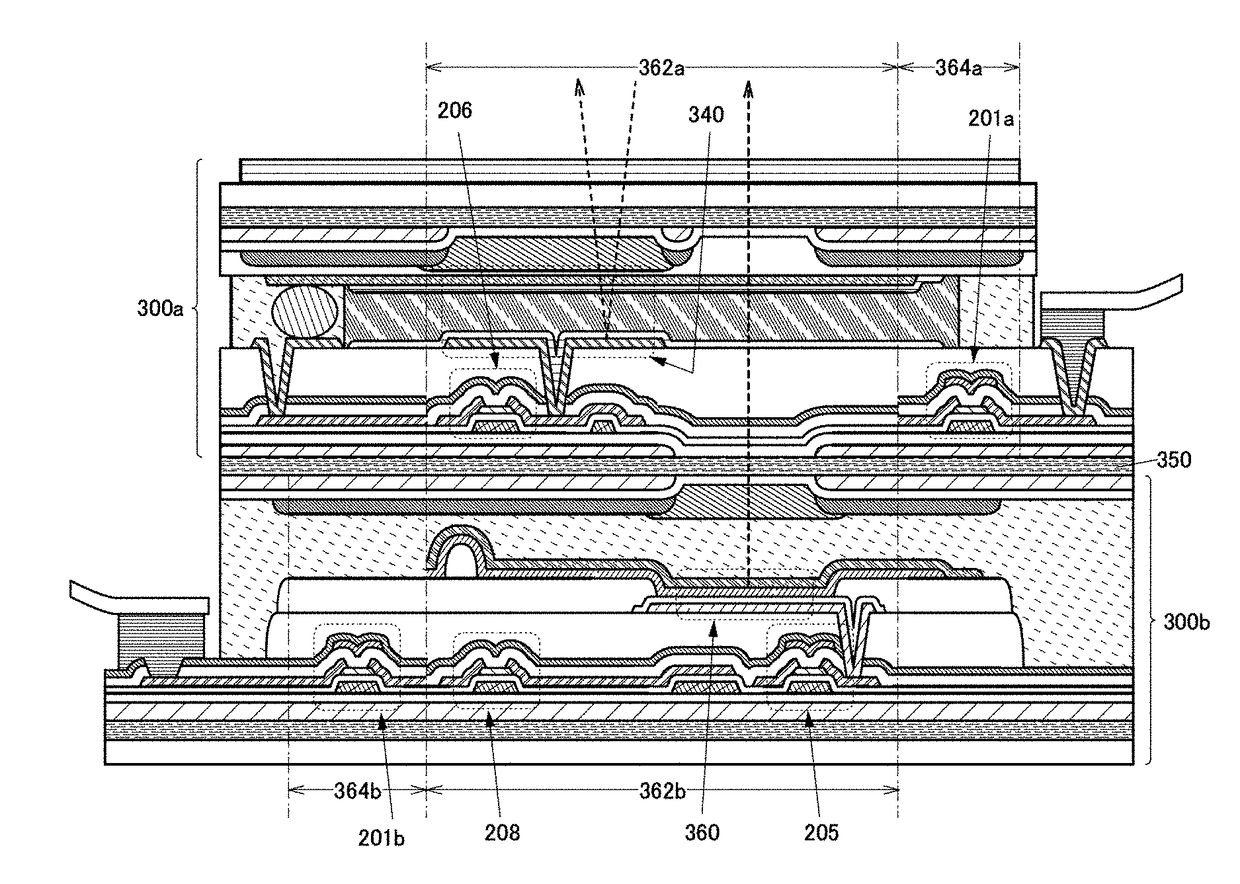

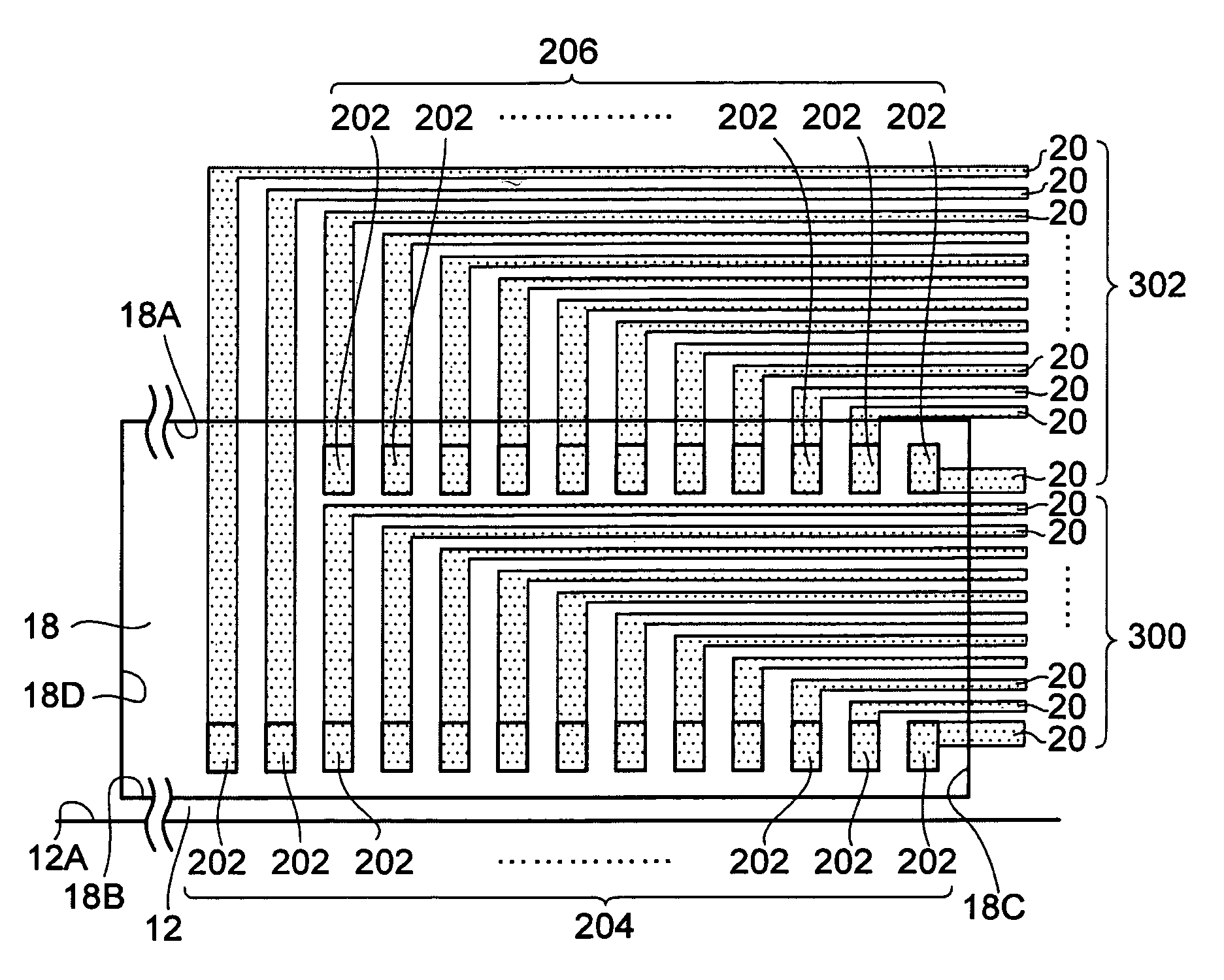

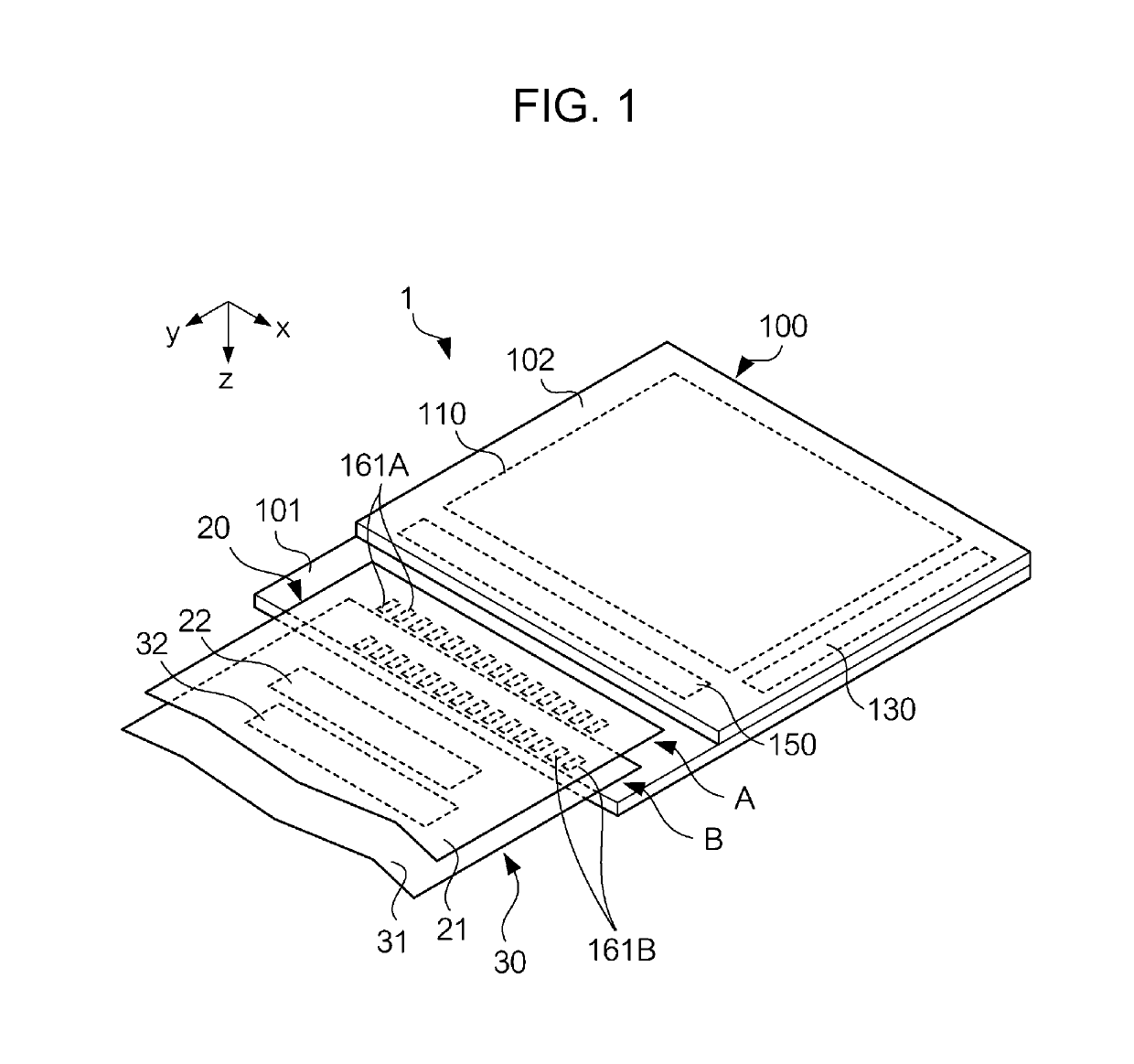

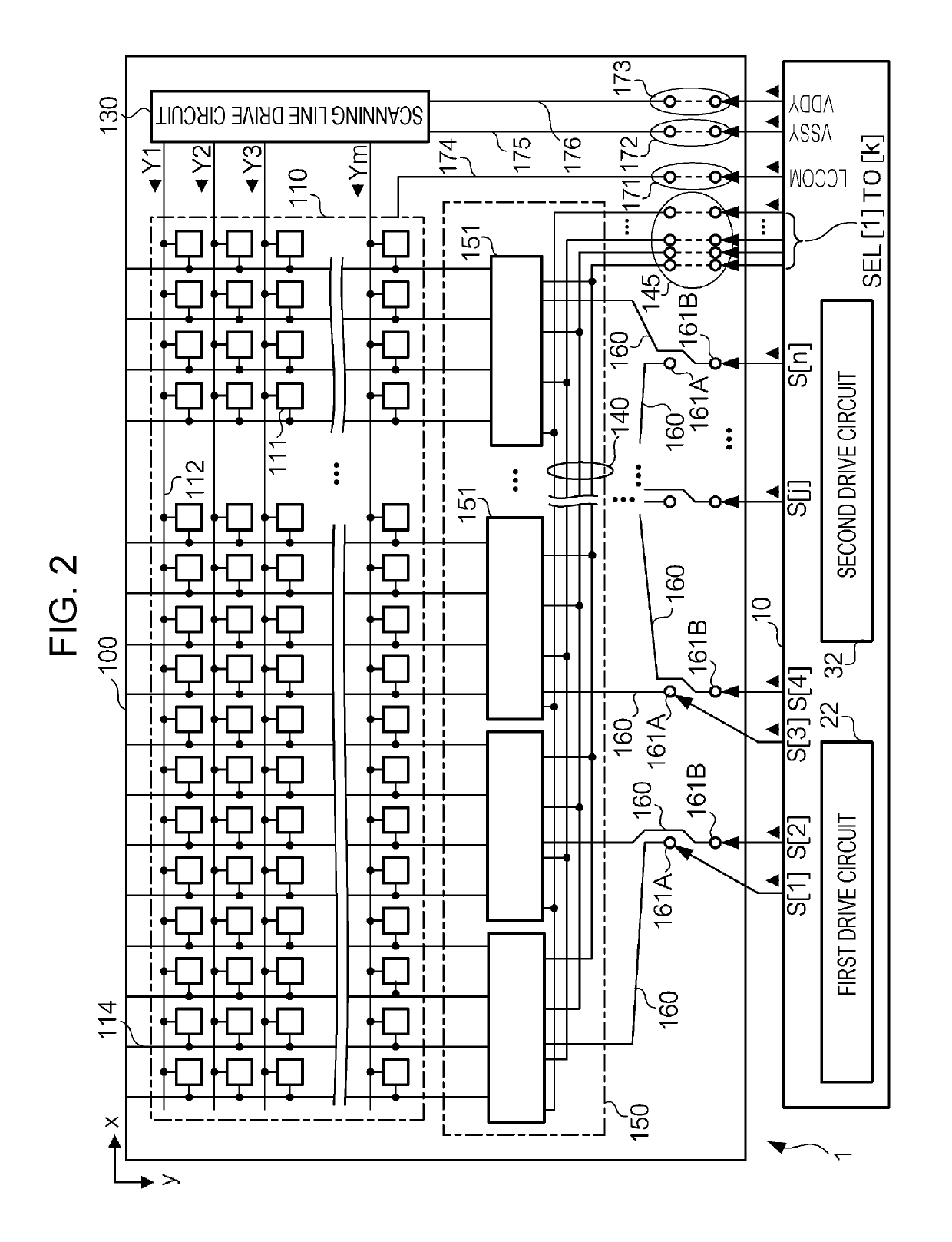

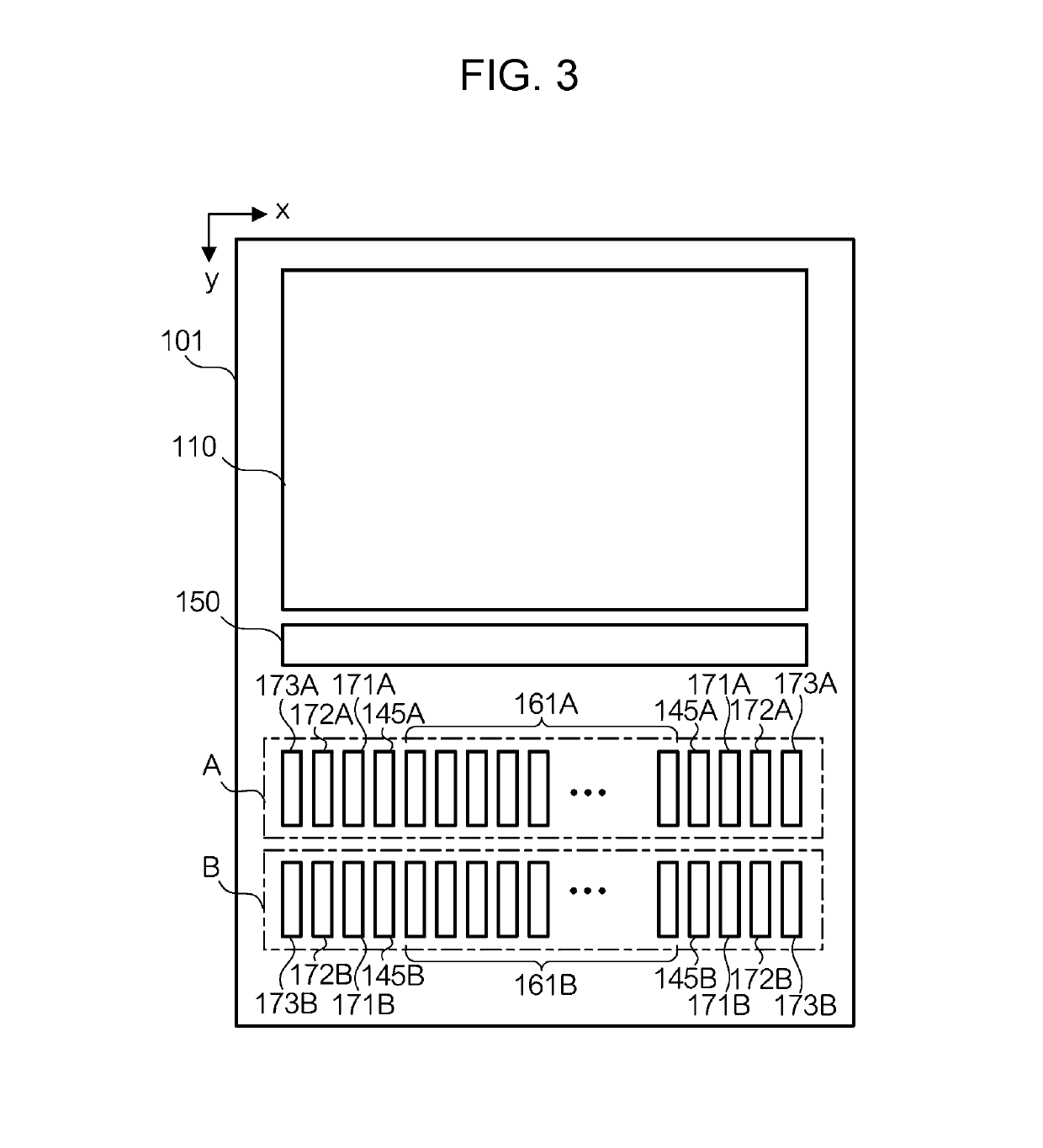

Electro-optical device and electronic apparatus

ActiveUS20180031892A1Reduce the use of areaIncrease in inhibition areaCross-talk/noise/interference reductionPrinted circuit aspectsEngineeringElectron

Owner:SEIKO EPSON CORP

Semiconductor integrated circuit

InactiveUS20060102967A1Increase in inhibition areaSemiconductor/solid-state device detailsSolid-state devicesHigh densityEngineering

A multi-storage nonvolatile memory of high density, high speed and high reliability has a memory transistor and switch transistors disposed on both the sides of the memory transistor. The memory transistor includes a gate insulating film having discrete traps and a memory gate electrode, whereas the switch transistors include switch gate electrodes. The gate insulating film has the discrete traps for storing information charge, can locally inject carriers, and one memory cell constitutes a multi-storage cell for storing at least information of 2 bits. The switch transistors having the switch gate electrodes realize source side injection. The memory transistor is fommed together with the switch transistors in self-aligned diffusion. The memory gate electrode of the memory transistor is connected to a word line so as to perform word-line erase.

Owner:RENESAS ELECTRONICS CORP

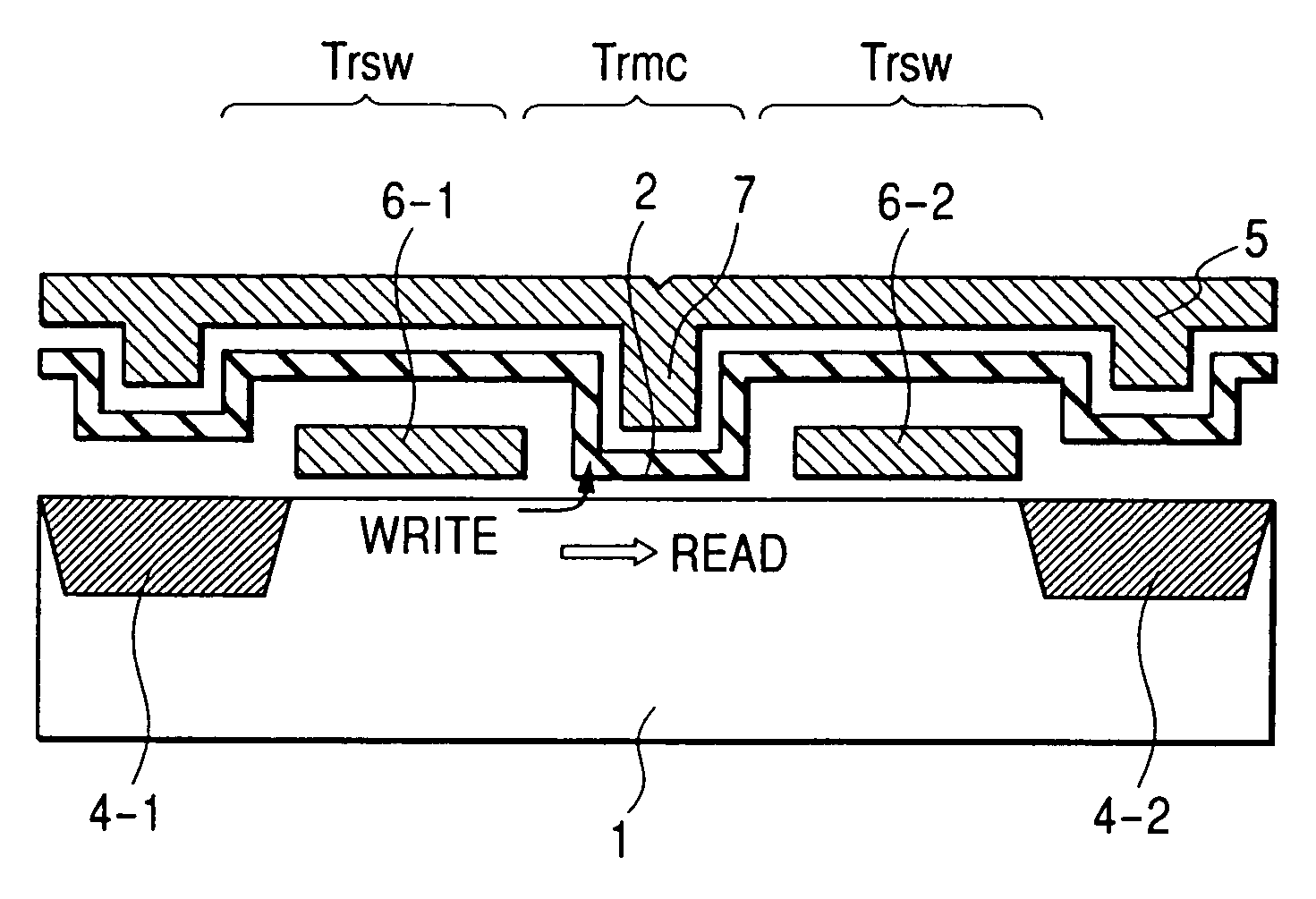

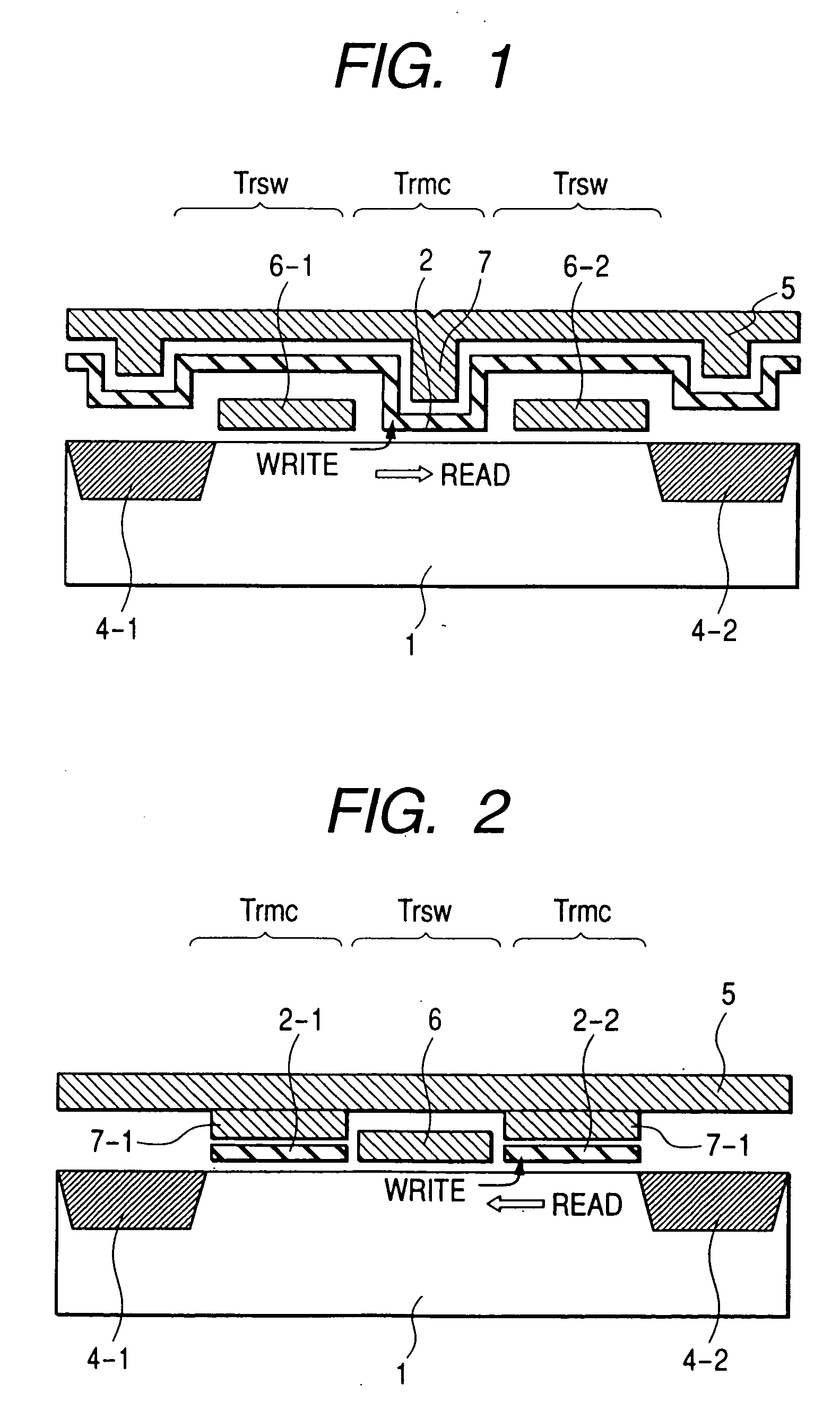

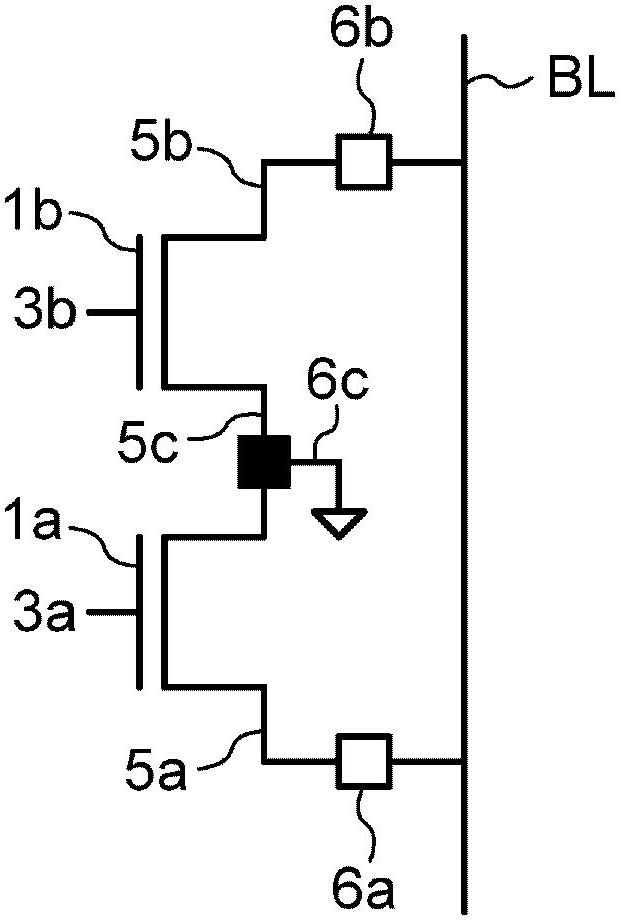

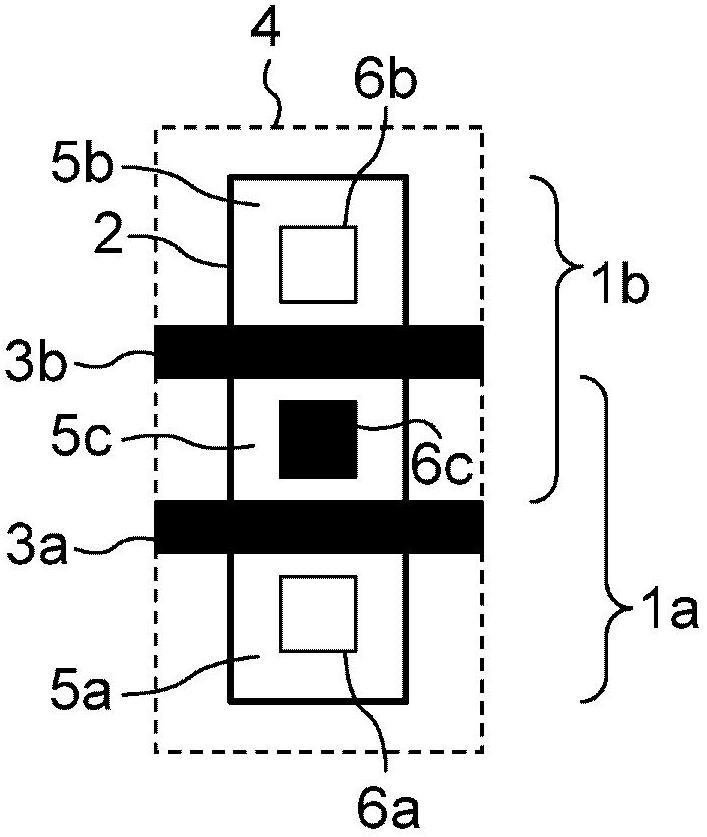

Semiconductor integrated circuit having two switch transistors formed between two diffusion-layer lines

InactiveUS6894344B2Increase in inhibition areaTransistorSolid-state devicesHigh densityDiffusion layer

A multi-storage nonvolatile memory of high density, high speed and high reliability has a memory transistor and switch transistors disposed on both the sides of the memory transistor. The memory transistor includes a gate insulating film having discrete traps and a memory gate electrode, whereas the switch transistors include switch gate electrodes. The gate insulating film has the discrete traps for storing information charge, can locally inject carriers, and one memory cell constitutes a multi-storage cell for storing at least information of 2 bits. The switch transistors having the switch gate electrodes realize source side injection. The memory transistor is fommed together with the switch transistors in self-aligned diffusion. The memory gate electrode of the memory transistor is connected to a word line so as to perform word-line erase.

Owner:RENESAS ELECTRONICS CORP

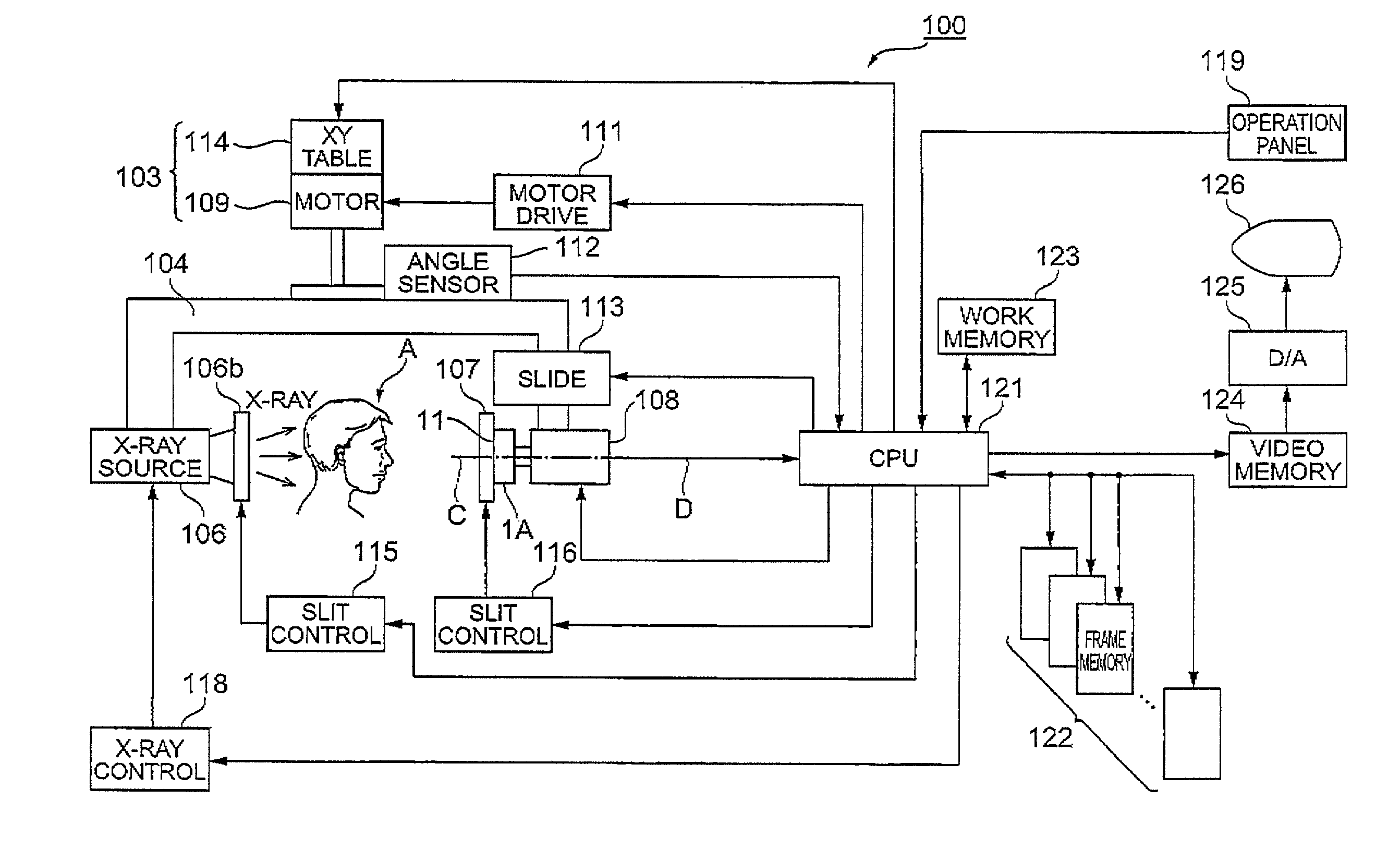

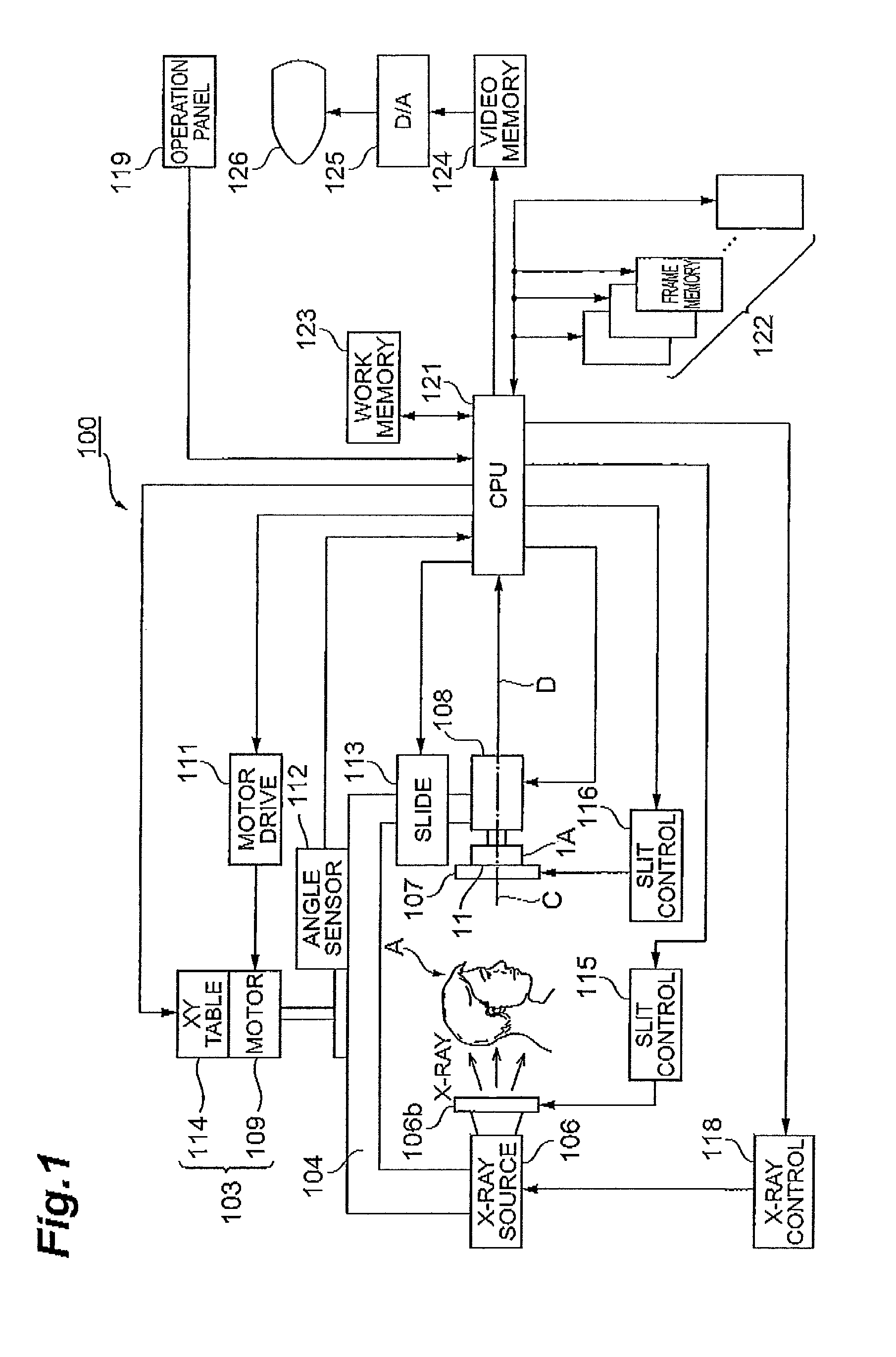

X-ray imaging system for medical use

ActiveUS20110141255A1Increase in inhibition areaTelevision system detailsComputerised tomographsX-rayEngineering

A solid-state image pickup apparatus 1A is formed such that M×N (where M<N and M and N are integers greater than or equal to 2) pixels are two-dimensionally arrayed in M rows and N columns, and has a photodetecting section 10A having a rectangular photosensitive surface whose longitudinal direction is the row direction. The solid-state image pickup apparatus 1A is supported rotatably by a rotation controlling section, and the rotation controlling section controls a rotation angle of the solid-state image pickup apparatus 1A such that the longitudinal direction of the photodetecting section 10A is made parallel to a moving direction B of the solid-state image pickup apparatus 1A in one imaging mode of the two imaging modes, and the longitudinal direction of the photodetecting section 10A is made perpendicular to the moving direction B of the solid-state image pickup apparatus 1A in the other imaging mode of the two imaging modes.

Owner:HAMAMATSU PHOTONICS KK

Semiconductor memory device and method of manufacturing the same

InactiveUS7271454B2Improve reliabilityIncrease in inhibition areaTransistorSolid-state devicesEngineeringBody region

Owner:RENESAS ELECTRONICS CORP

Display panel

ActiveUS20110216490A1Suppress increase in areaIncrease number of inputCathode-ray tube indicatorsPrinted circuit manufactureEngineeringSurface plate

Owner:LAPIS SEMICON CO LTD

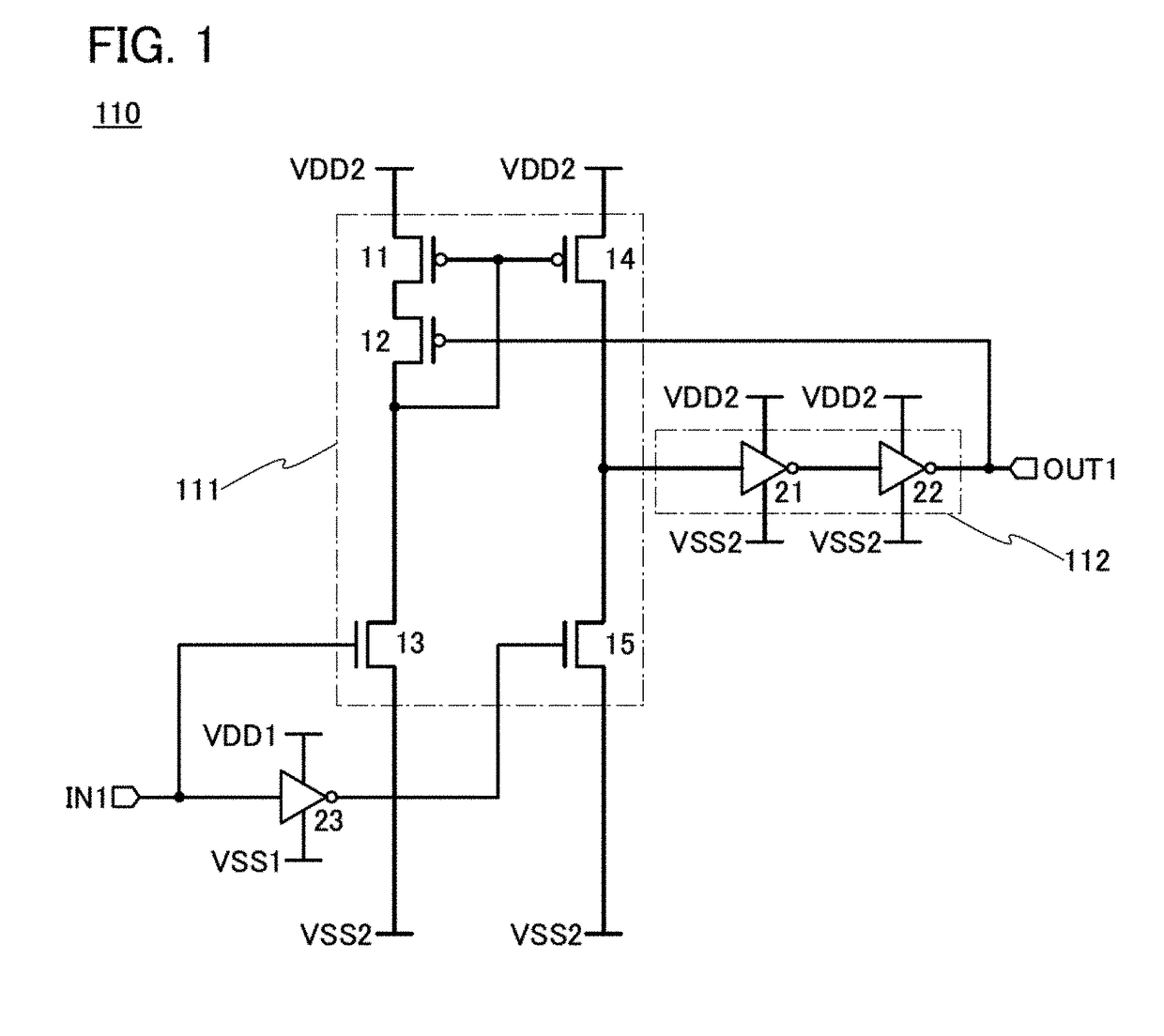

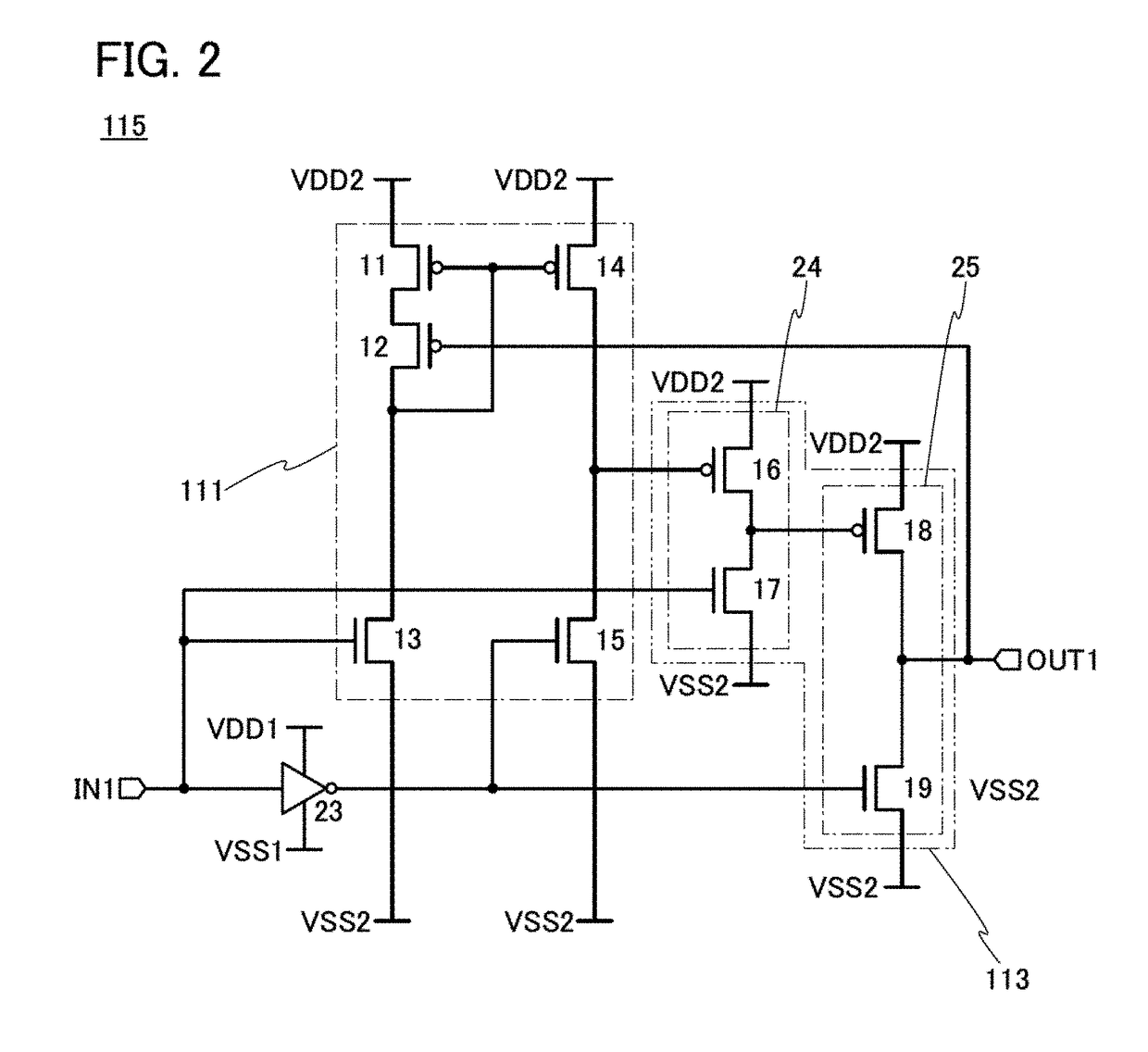

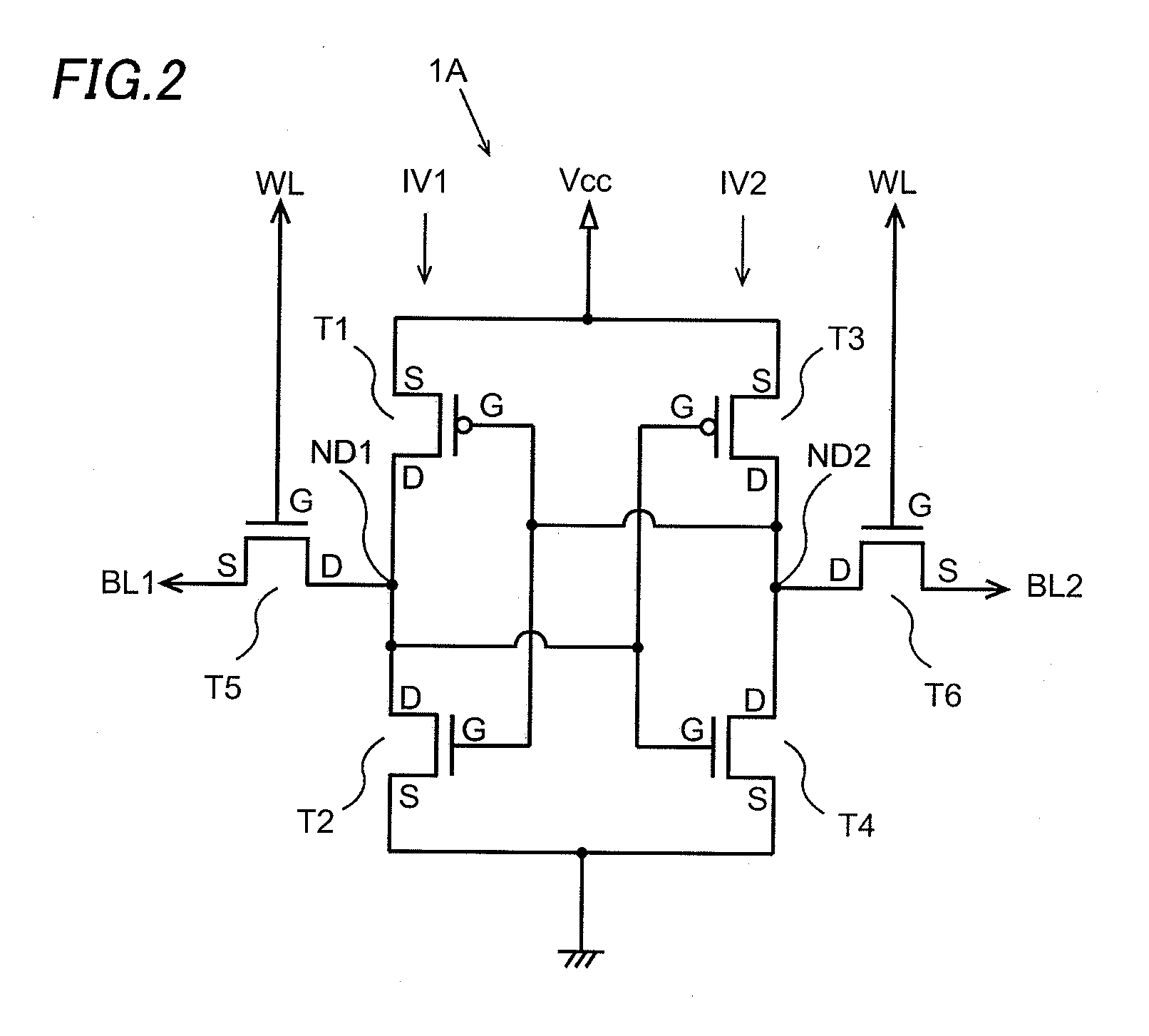

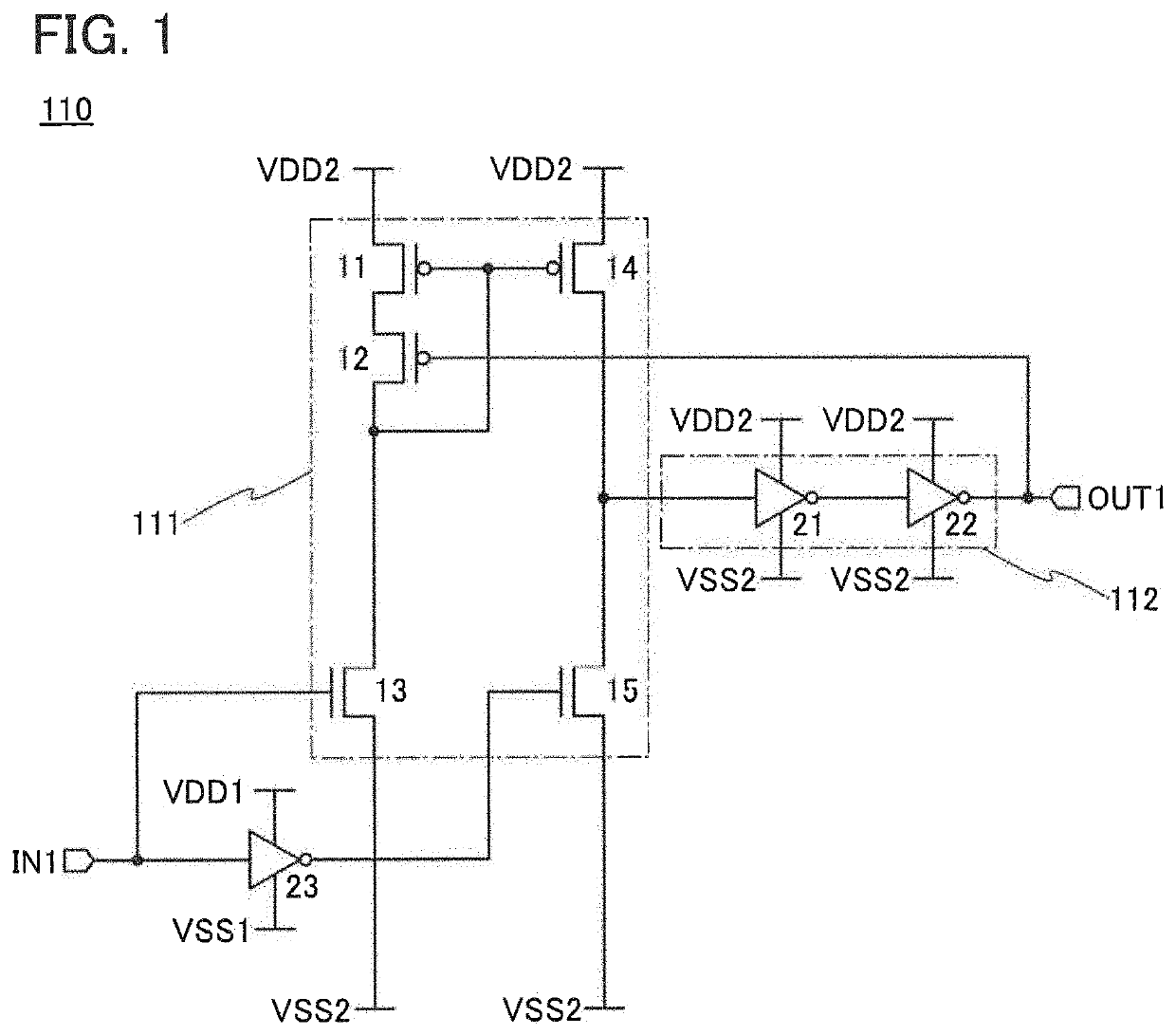

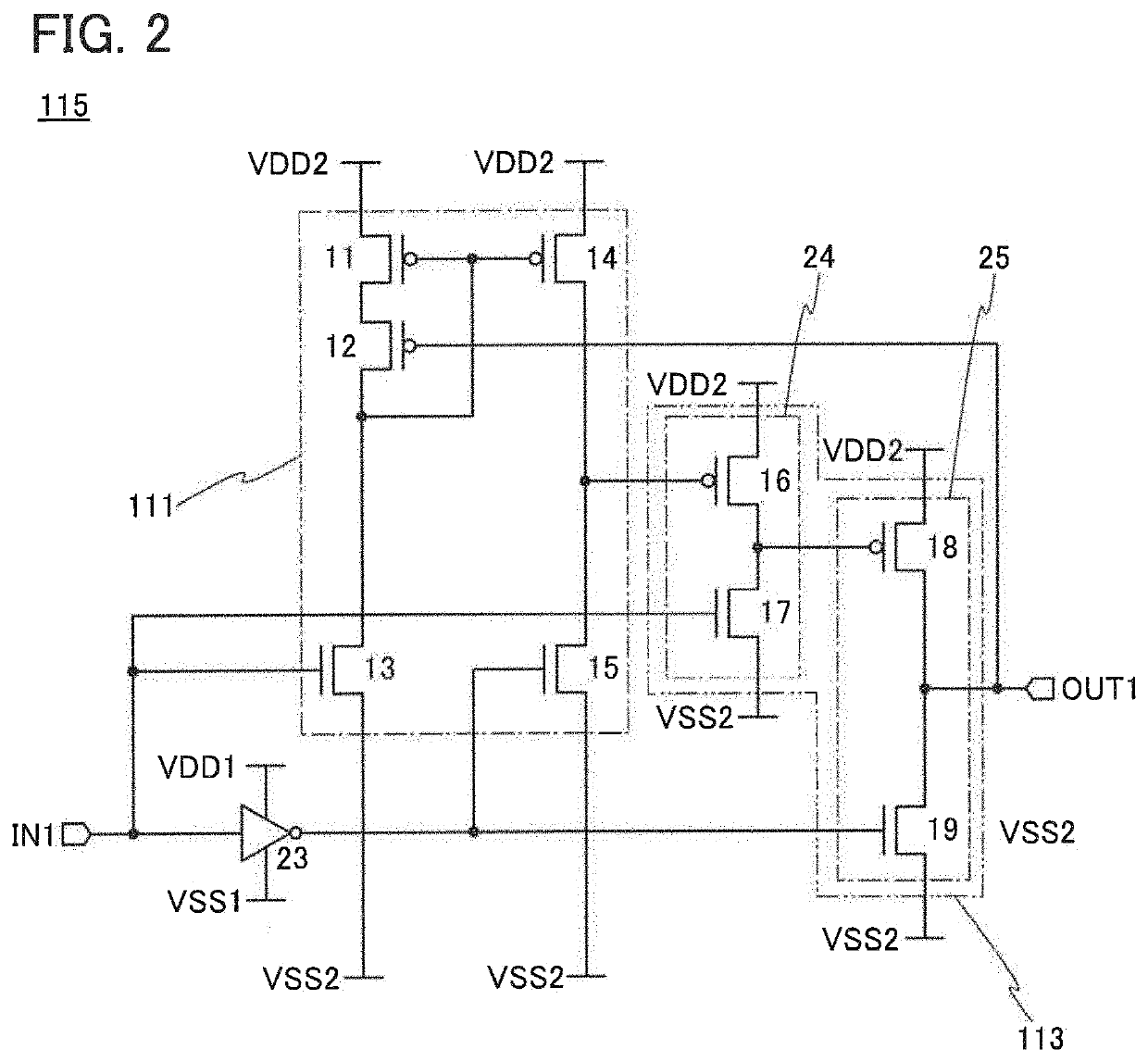

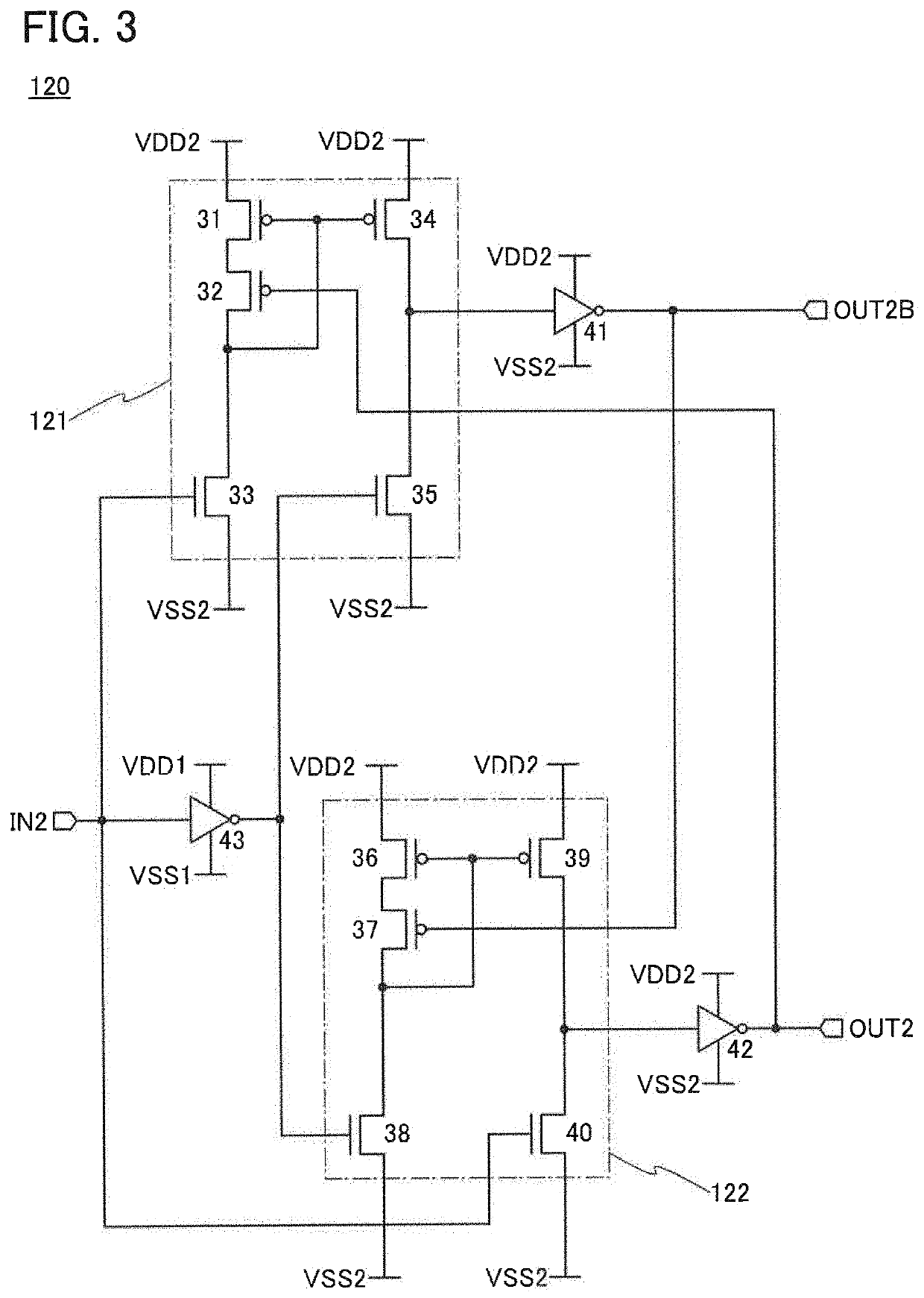

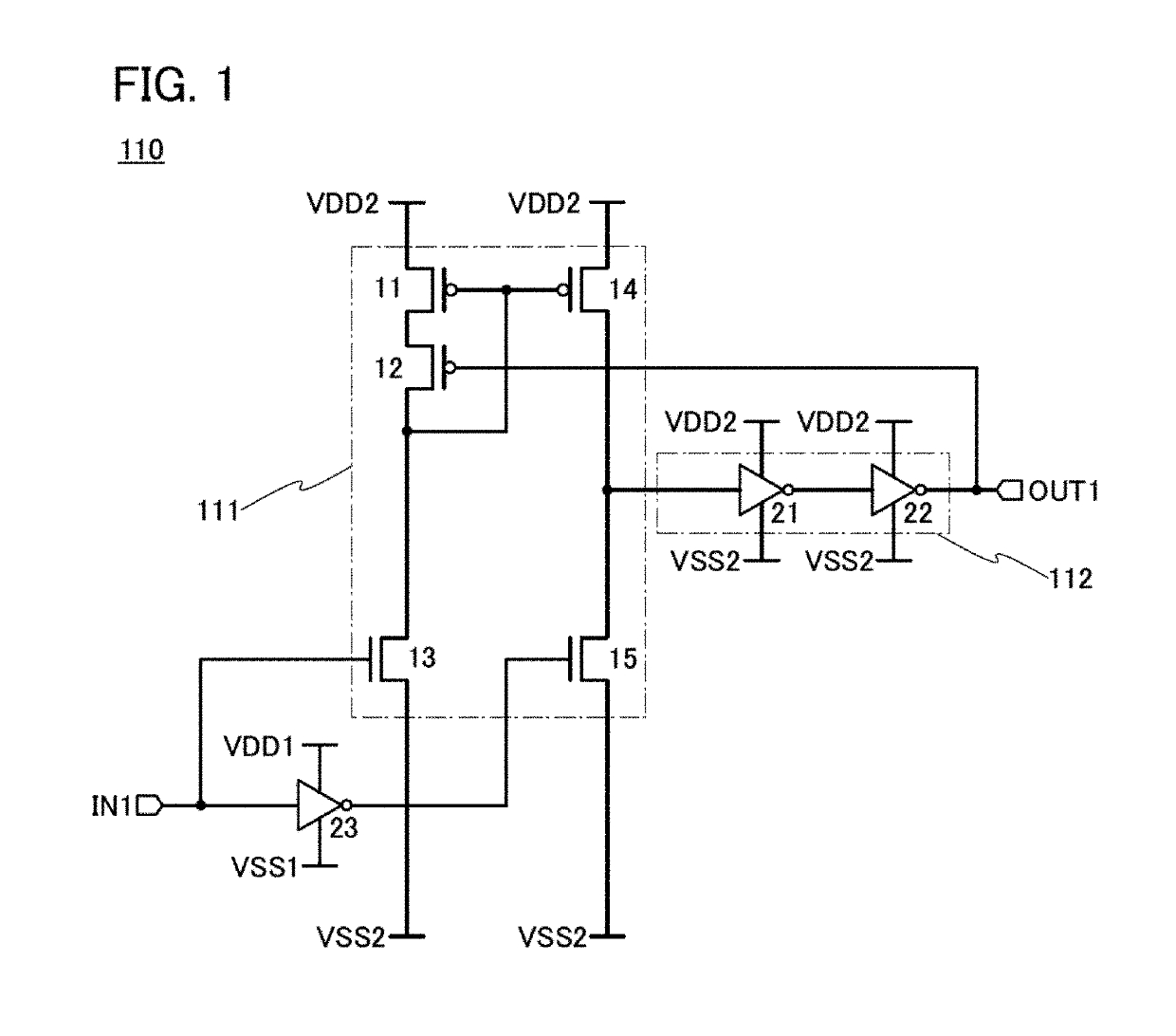

Semiconductor device and electronic device

InactiveUS20180091121A1Reduce areaGuaranteed uptimePower reduction in field effect transistorsStatic indicating devicesPower semiconductor deviceEngineering

An object is to provide a level shift circuit that operates stably. A semiconductor device includes a level shift circuit including first to fourth transistors and a buffer circuit. One of a source and a drain (S / D) of the first transistor is connected to one of a source and a drain of the second transistor. The other of the source and the drain of the second transistor is connected to one of a source and a drain of the third transistor. A gate of the first transistor and a gate of the fourth transistor are connected to the other of the source and the drain of the second transistor and the one of the source and the drain of the third transistor. A gate of the third transistor is connected to a wiring to which an input signal is input. An input terminal of the buffer circuit is connected to one of a source and a drain of the fourth transistor. An output terminal of the buffer circuit is connected to a gate of the second transistor and a wiring to which an output signal is output.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

In a memory cell including CMOS inverters, an increase in an area of the memory cell caused by restrictions on a gate wiring due to a leakage current and restrictions due to design rules is suppressed. A first wiring and a second wiring are laid out as a first metal layer in the memory cell that includes a first inverter and a second inverter. The first wiring is connected with two drains in the first inverter and a second gate wiring in the second inverter. The second wiring is connected with two drains in the second inverter and a first gate wiring in the first inverter. The first wiring is laid out to overlap with the second gate wiring, and the second wiring is laid out to overlap with the first gate wiring. A second metal layer is laid out above the first metal layer, and a third metal layer is laid out above the second metal layer.

Owner:SEMICON COMPONENTS IND LLC

X-ray imaging system for medical use

ActiveUS8988517B2Increase in inhibition areaTelevision system detailsColor television detailsSoft x rayX-ray

A solid-state image pickup apparatus 1A is formed such that M×N (where M<N and M and N are integers greater than or equal to 2) pixels are two-dimensionally arrayed in M rows and N columns, and has a photodetecting section 10A having a rectangular photosensitive surface whose longitudinal direction is the row direction. The solid-state image pickup apparatus 1A is supported rotatably by a rotation controlling section, and the rotation controlling section controls a rotation angle of the solid-state image pickup apparatus 1A such that the longitudinal direction of the photodetecting section 10A is made parallel to a moving direction B of the solid-state image pickup apparatus 1A in one imaging mode of the two imaging modes, and the longitudinal direction of the photodetecting section 10A is made perpendicular to the moving direction B of the solid-state image pickup apparatus 1A in the other imaging mode of the two imaging modes.

Owner:HAMAMATSU PHOTONICS KK

Medical X-ray imaging system

ActiveUS8050381B2Increase in inhibition areaIncrease the areaTelevision system detailsX-ray/infra-red processesSoft x rayX-ray

The solid-state image pick-up device (1) includes a photodetecting section (10) which is formed by two-dimensionally aligning M×N (M and N are integers not less than 2) pixels in M rows and N columns and has a rectangular photodetecting surface. This solid-state image pick-up device (1) is supported rotatably by a rotation controlling section, and the rotation controlling section controls the rotation angle of the solid-state image pick-up device (1) so that the row direction or column direction of the photodetecting section (10) becomes parallel to the movement direction (B) of the solid-state image pick-up device (1) in one of the two imaging modes, and both of the row direction and the column direction of the photodetecting section (10) tilt with respect to the movement direction (B) of the solid-state image pick-up device (1) in the other imaging mode of the two imaging modes.

Owner:HAMAMATSU PHOTONICS KK

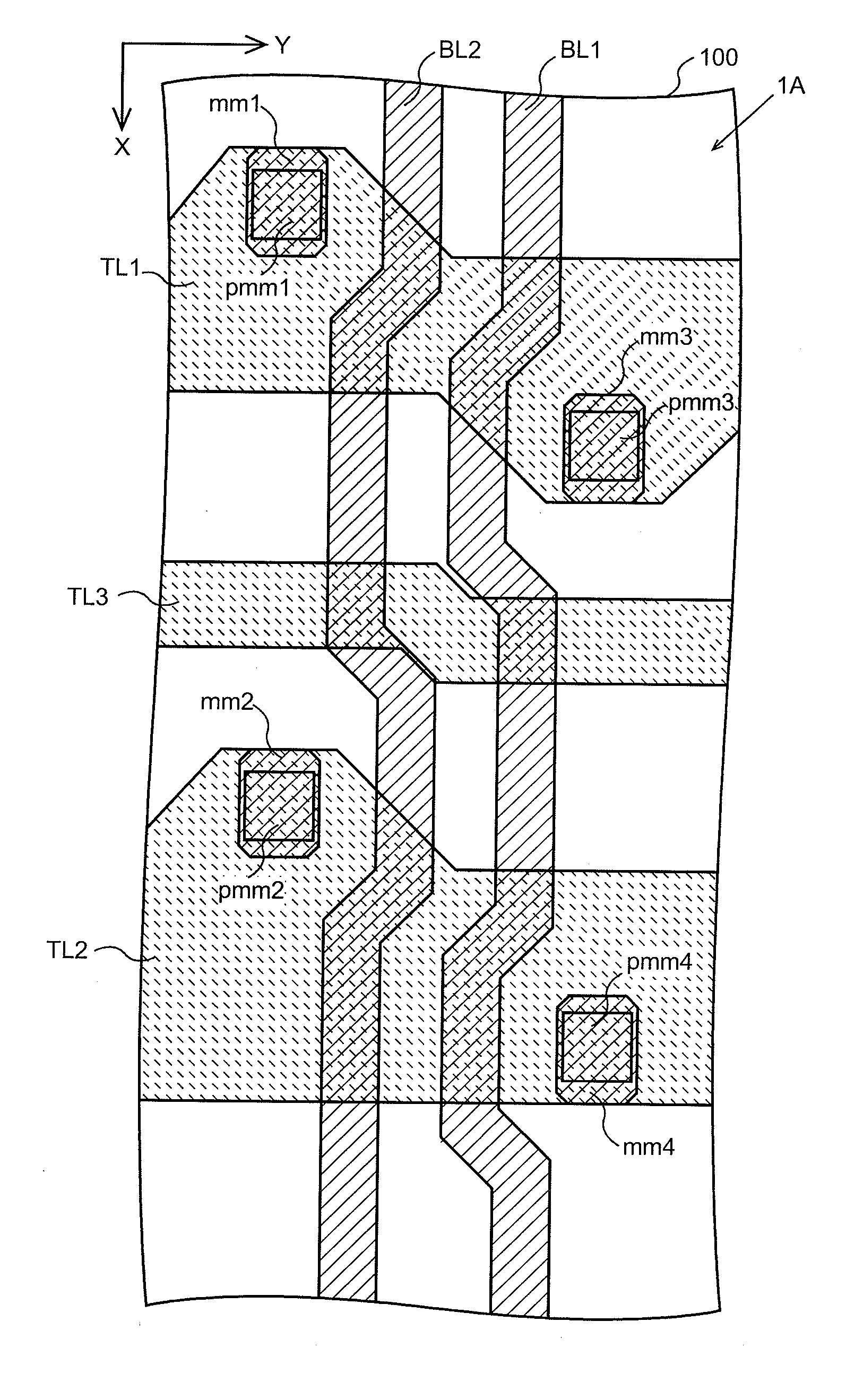

Semiconductor storage device

InactiveCN102640281AIncrease in inhibition areaWide Bit Line Separation WidthSolid-state devicesRead-only memoriesDiffusionBit line

In a semiconductor storage device that includes memory cells each constituted by one transistor, two adjacent bits of the memory cells form a diffusion pattern (4), two adjacent transistors share a common source region, and the two drain regions are separated from each other. A plurality of arrays (120, 130) each including at least one line of the diffusion patterns (4) have bit lines that are independent for each array. In addition, end portions of the bit lines for each array are located on the two drain regions separated from each other with the common source regions interposed therebetween in one diffusion pattern (4) at an array-dividing border portion. With this, the area can be reduced while a sufficient separation width between the bit lines can be ensured.

Owner:SOCIONEXT INC

Semiconductor integrated circuit having discrete trap type memory cells

InactiveUS7190023B2Increase in inhibition areaTransistorSolid-state devicesHigh densitySemiconductor

A multi-storage nonvolatile memory of high density, high speed and high reliability has a memory transistor and switch transistors disposed on both the sides of the memory transistor. The memory transistor includes a gate insulating film having discrete traps and a memory gate electrode, whereas the switch transistors include switch gate electrodes. The gate insulating film has the discrete traps for storing information charge, can locally inject carriers, and one memory cell constitutes a multi-storage cell for storing at least information of 2 bits. The switch transistors having the switch gate electrodes realize source side injection. The memory transistor is fommed together with the switch transistors in self-aligned diffusion. The memory gate electrode of the memory transistor is connected to a word line so as to perform word-line erase.

Owner:RENESAS ELECTRONICS CORP

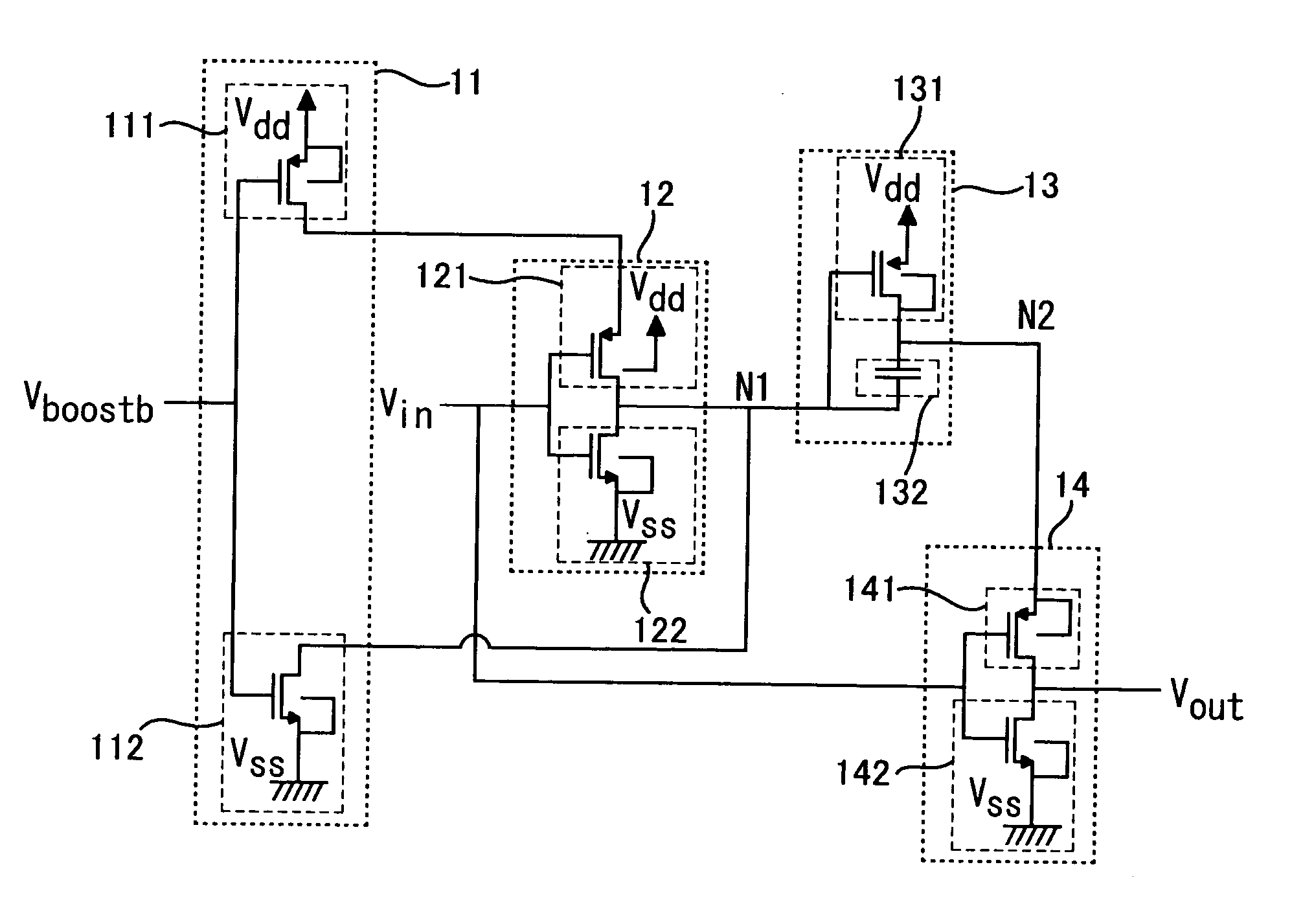

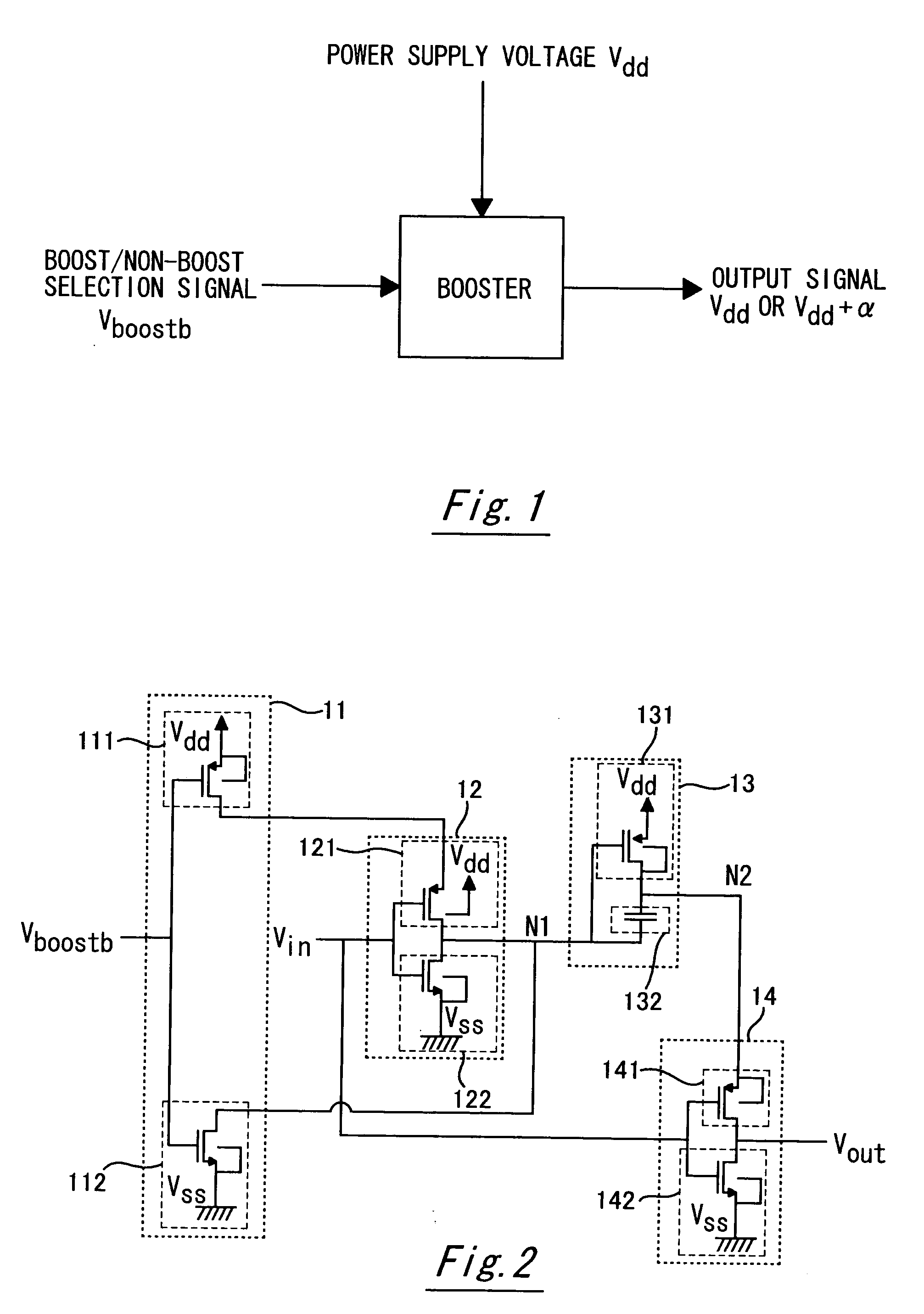

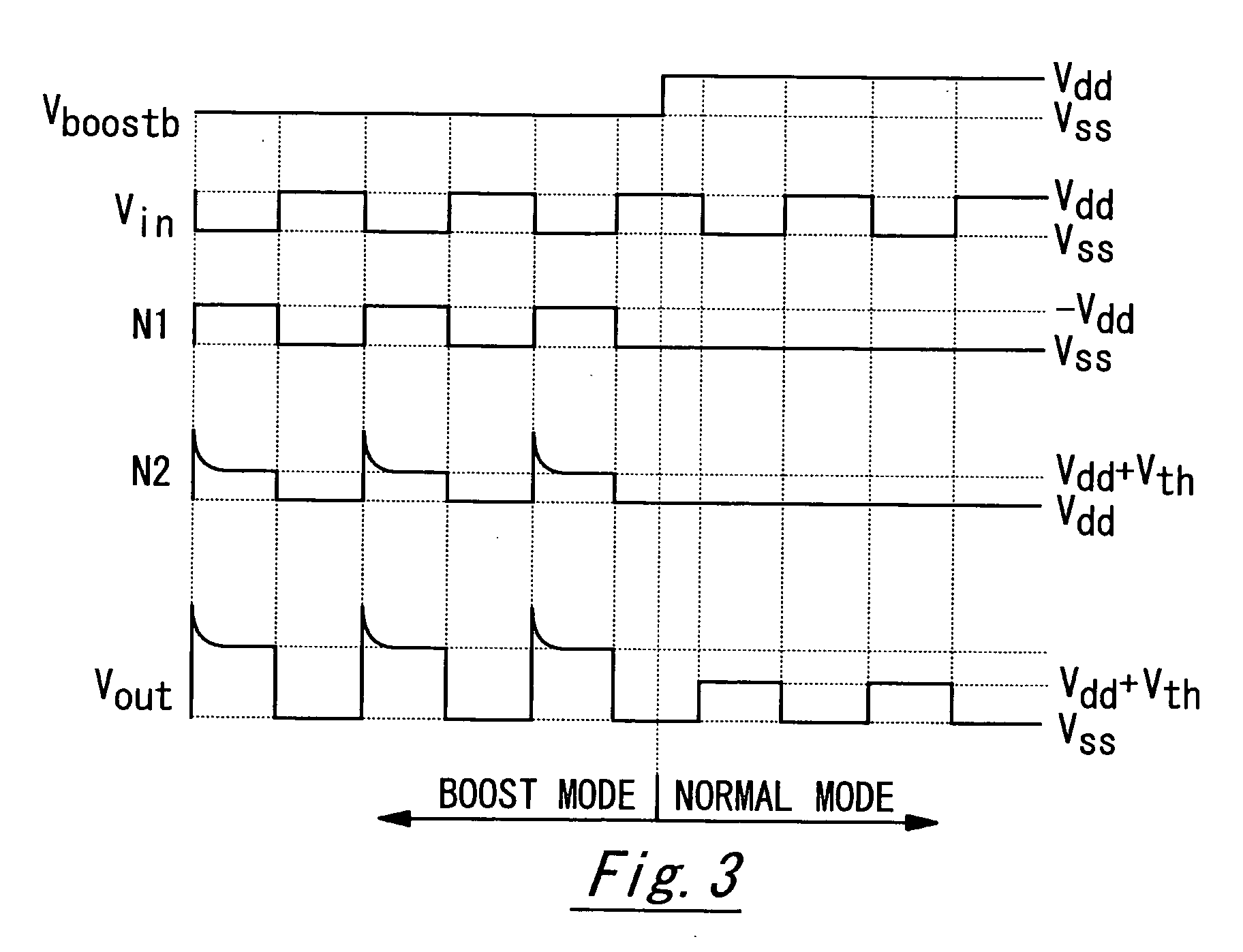

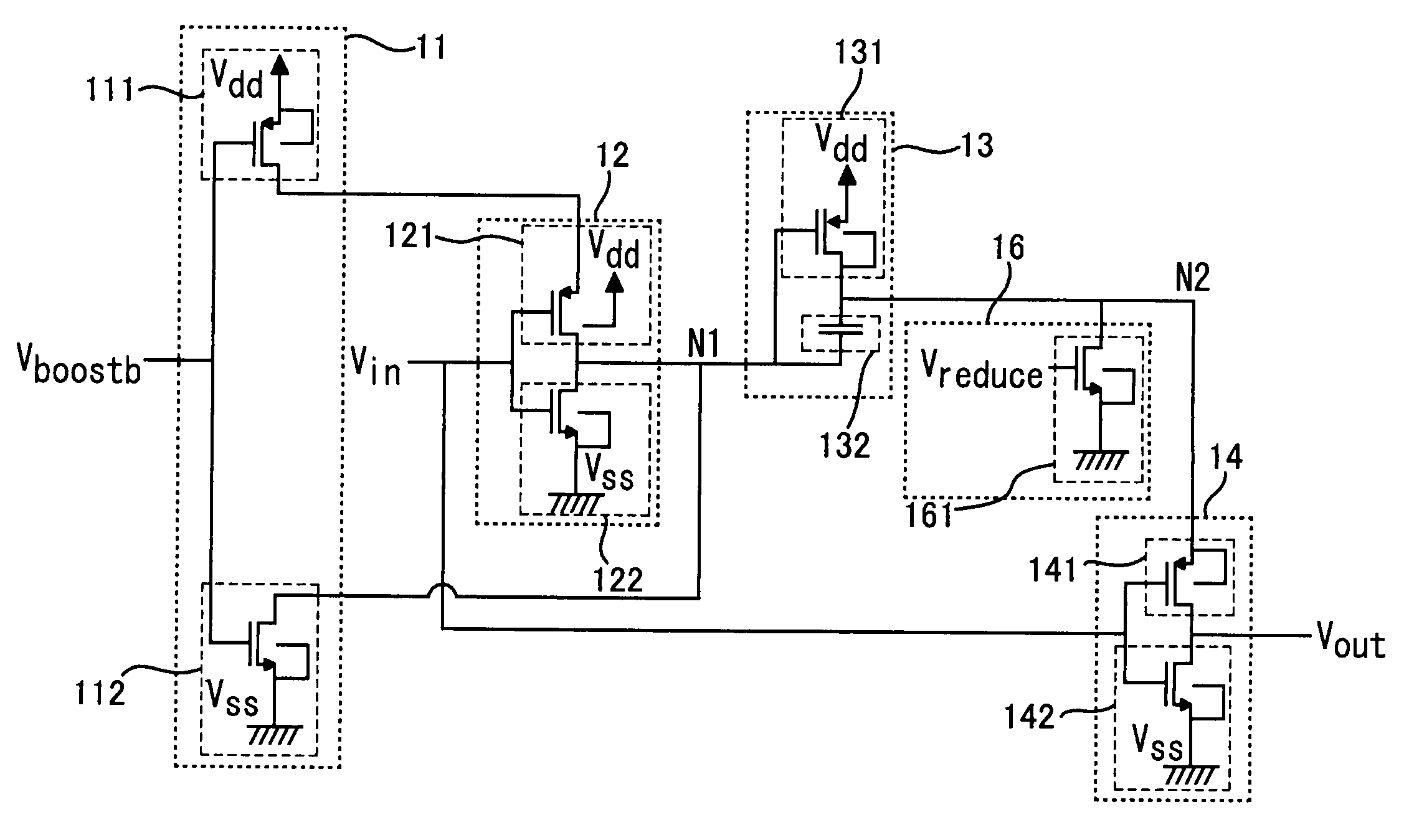

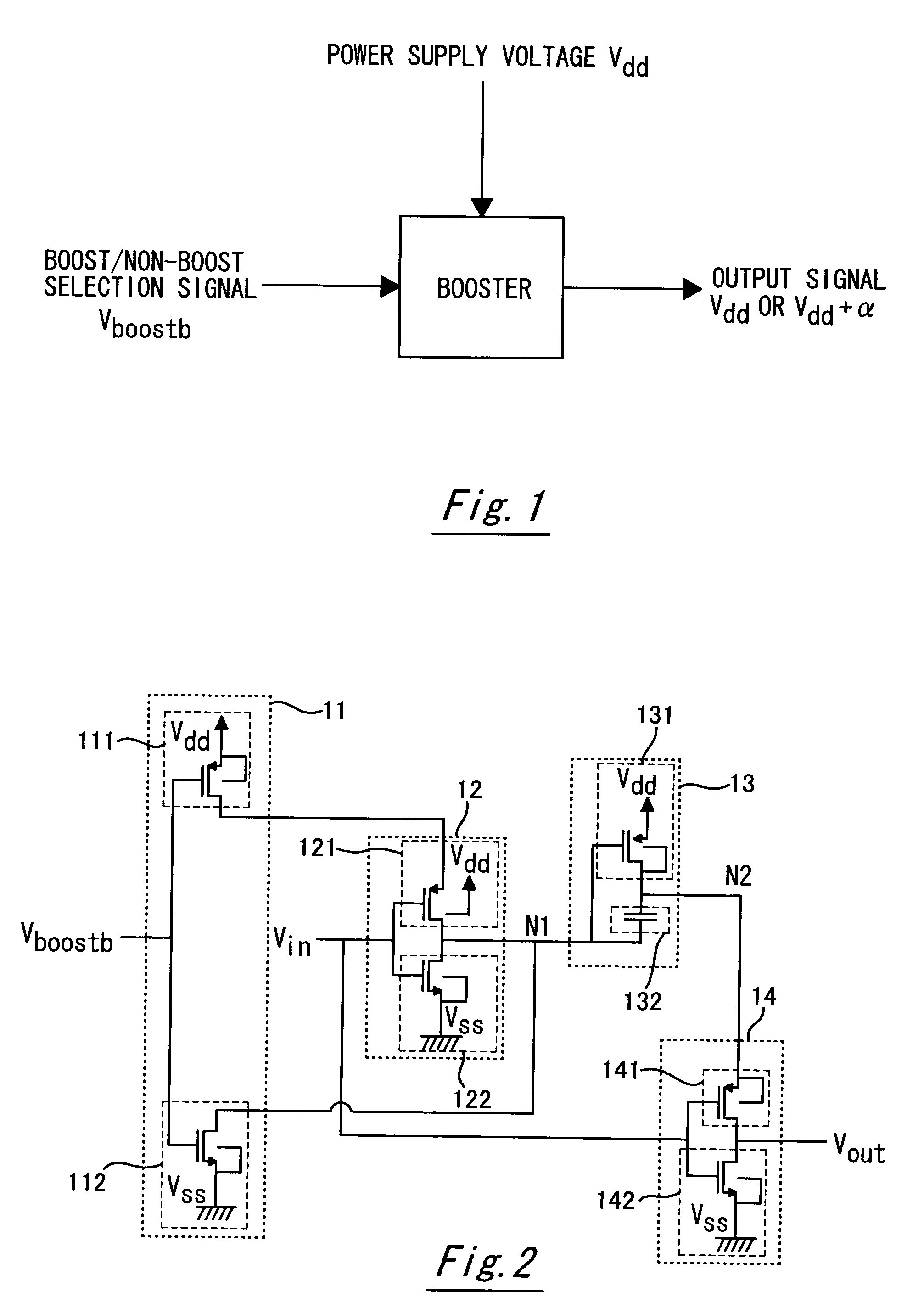

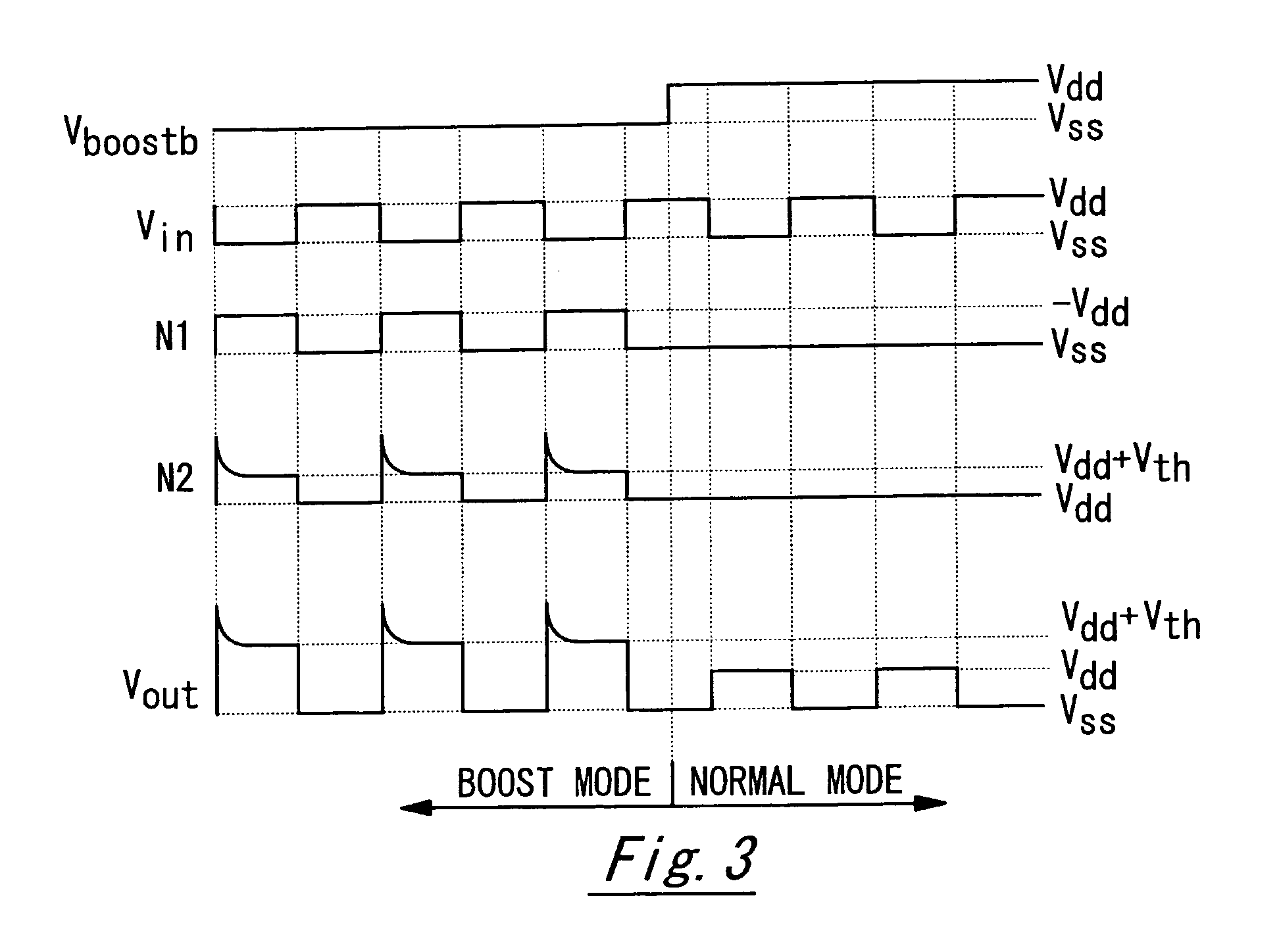

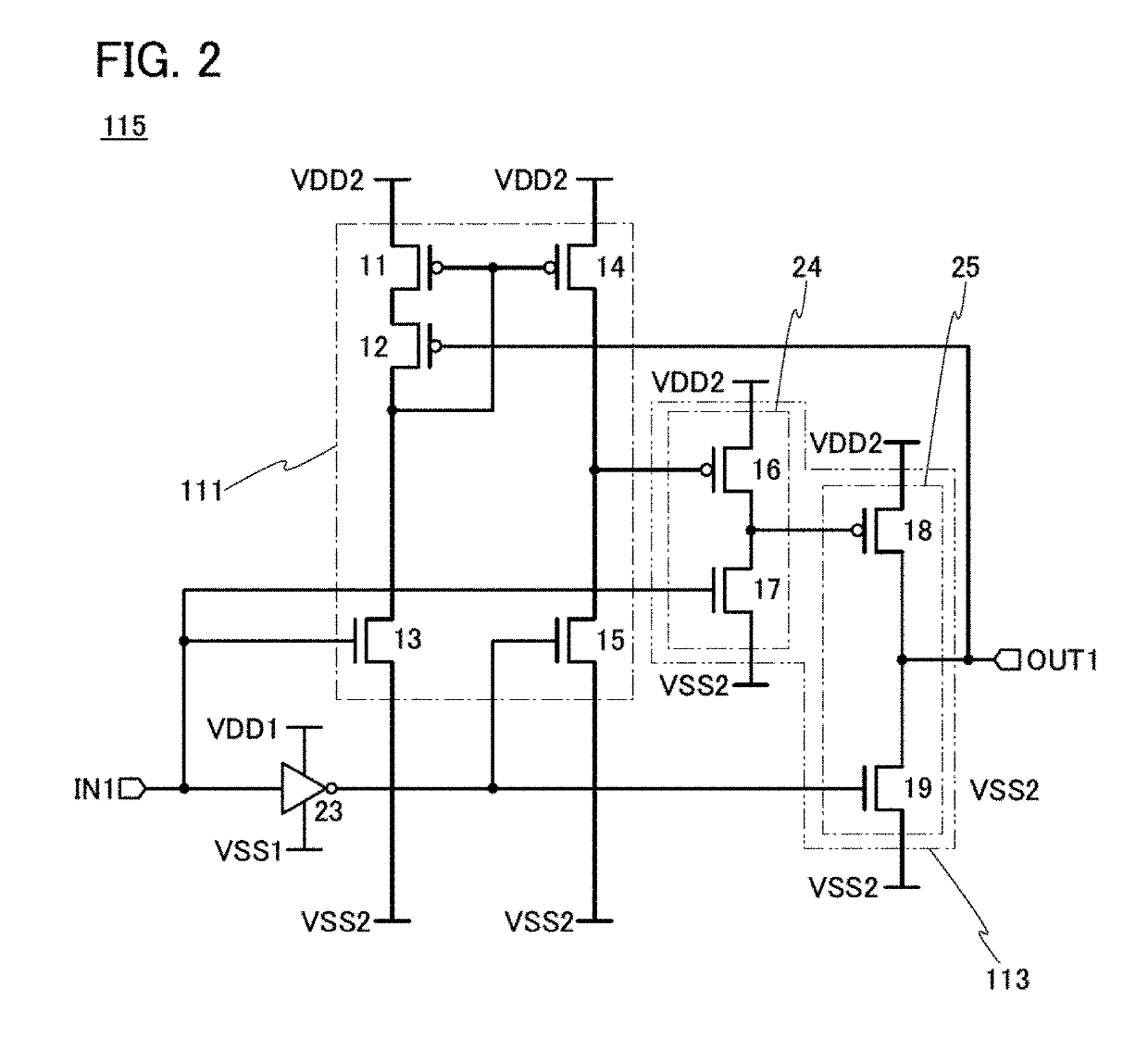

Semiconductor circuit apparatus

InactiveUS20060267670A1Increase in inhibition areaHigh power supply voltageElectronic switchingApparatus without intermediate ac conversionBoost controllerSemiconductor

A semiconductor circuit apparatus includes a booster which is connected to a single power supply and outputs a power supply voltage of the power supply or a voltage different from the power supply voltage, and a boost controller which controls whether to output the power supply voltage of the power supply or the voltage different from the power supply voltage.

Owner:RENESAS ELECTRONICS CORP

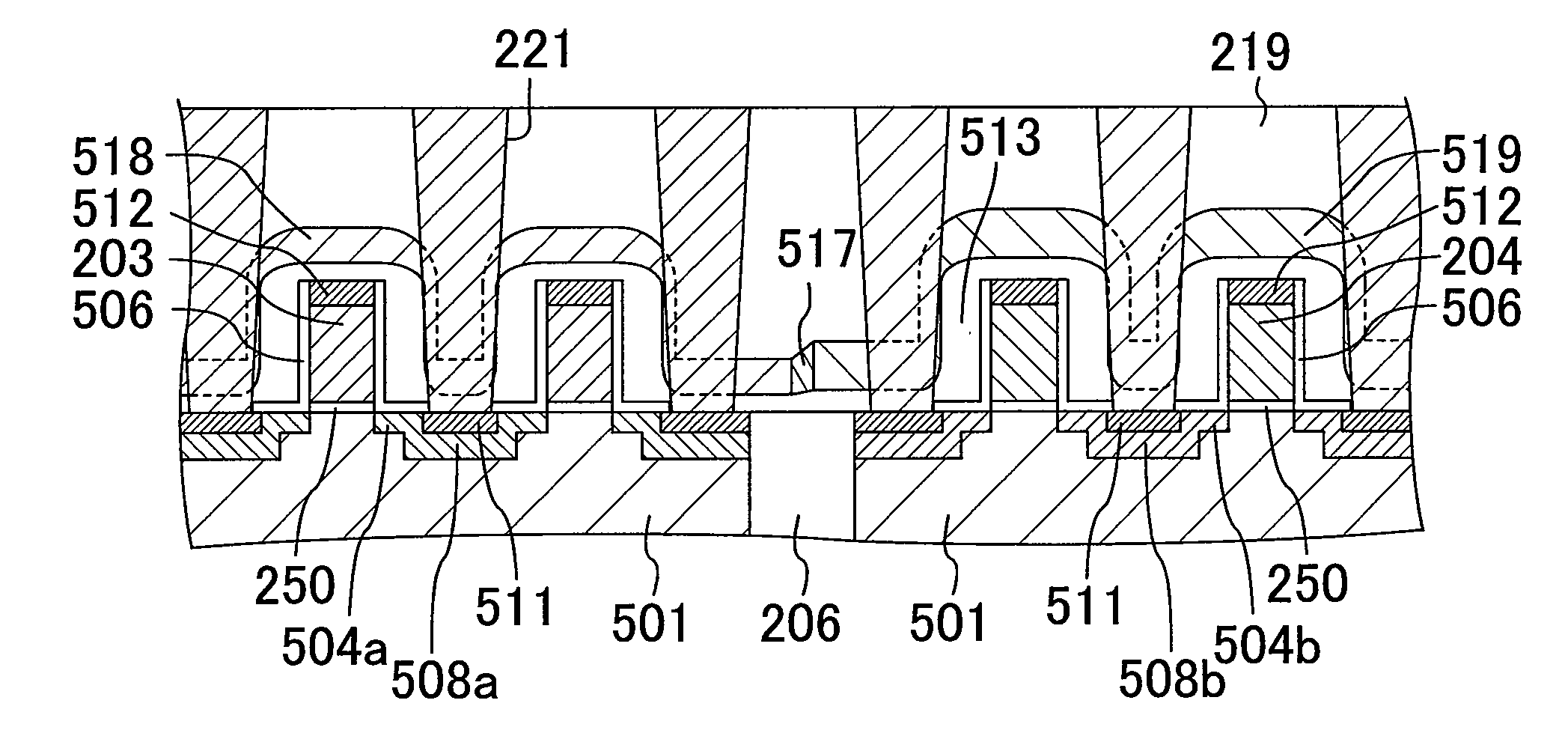

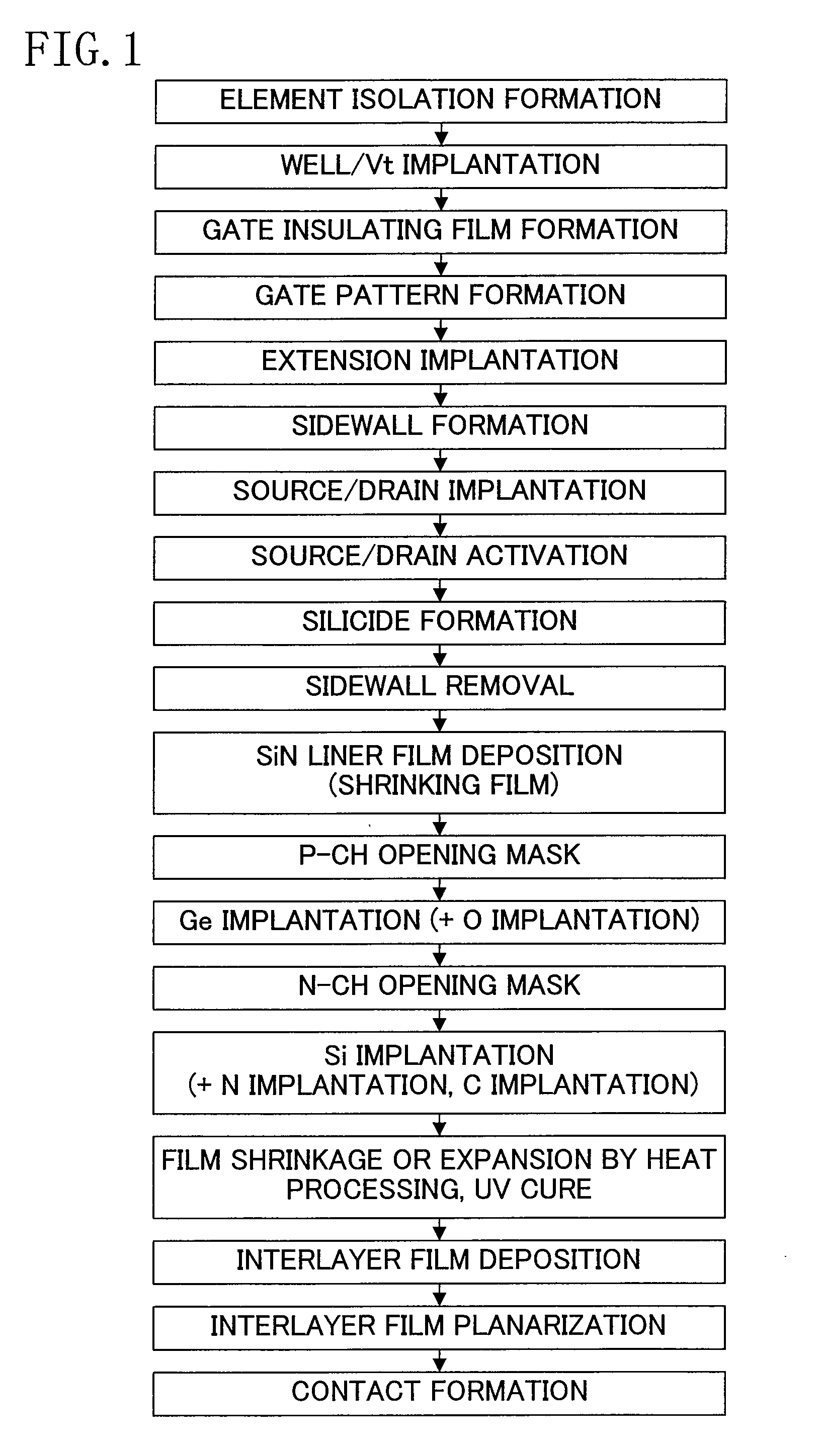

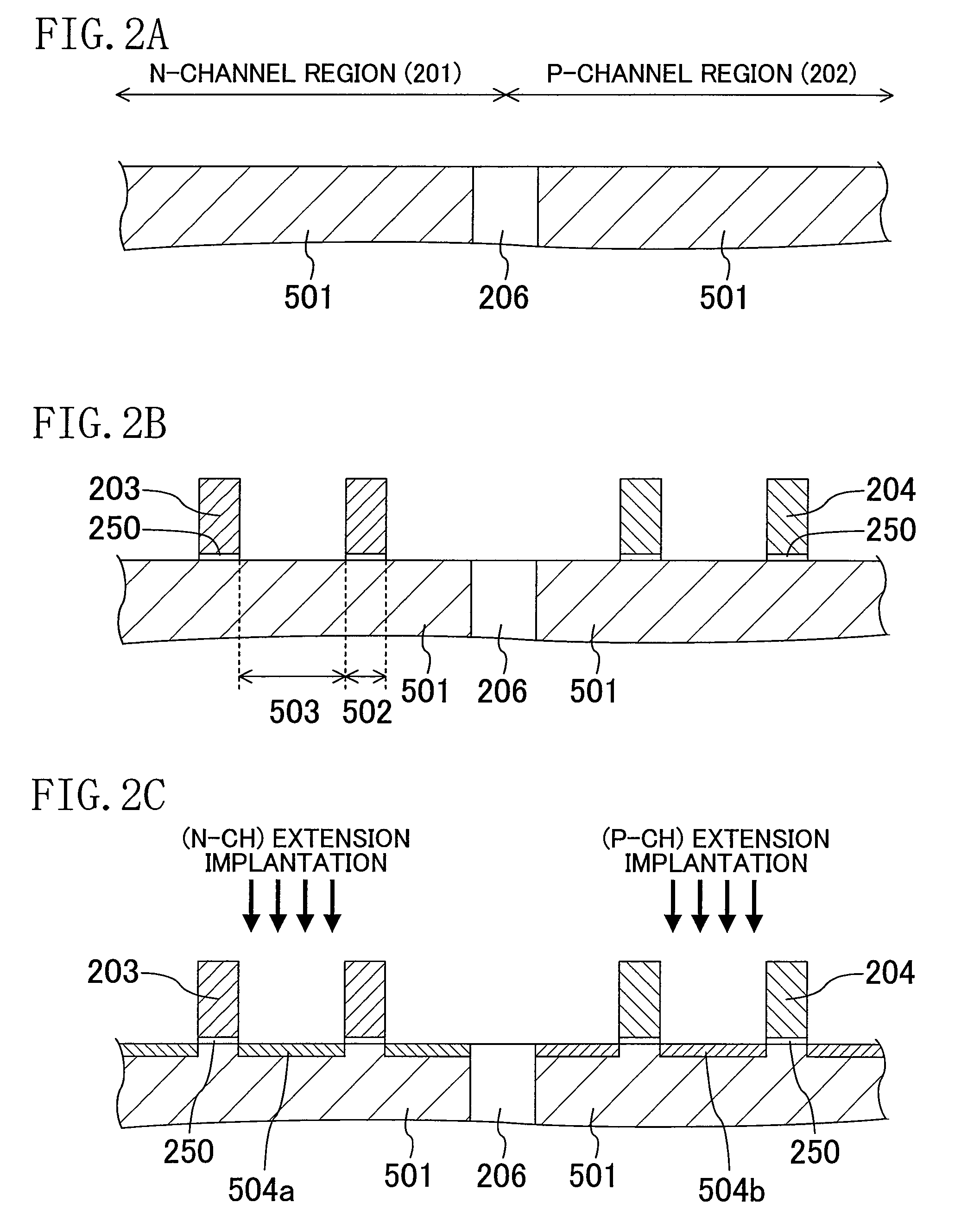

Semiconductor device and manufacturing method thereof

ActiveUS8084826B2Increase in inhibition areaReduce yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

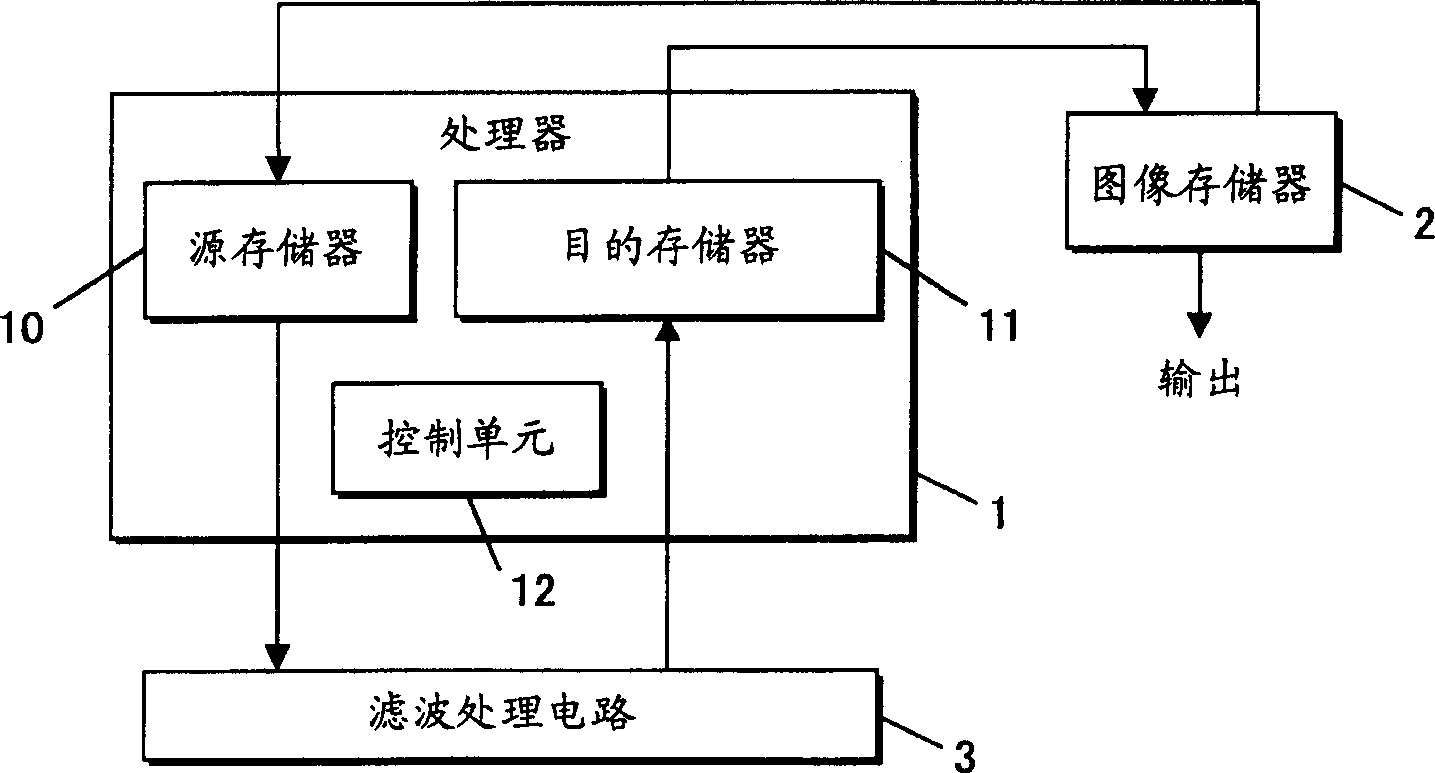

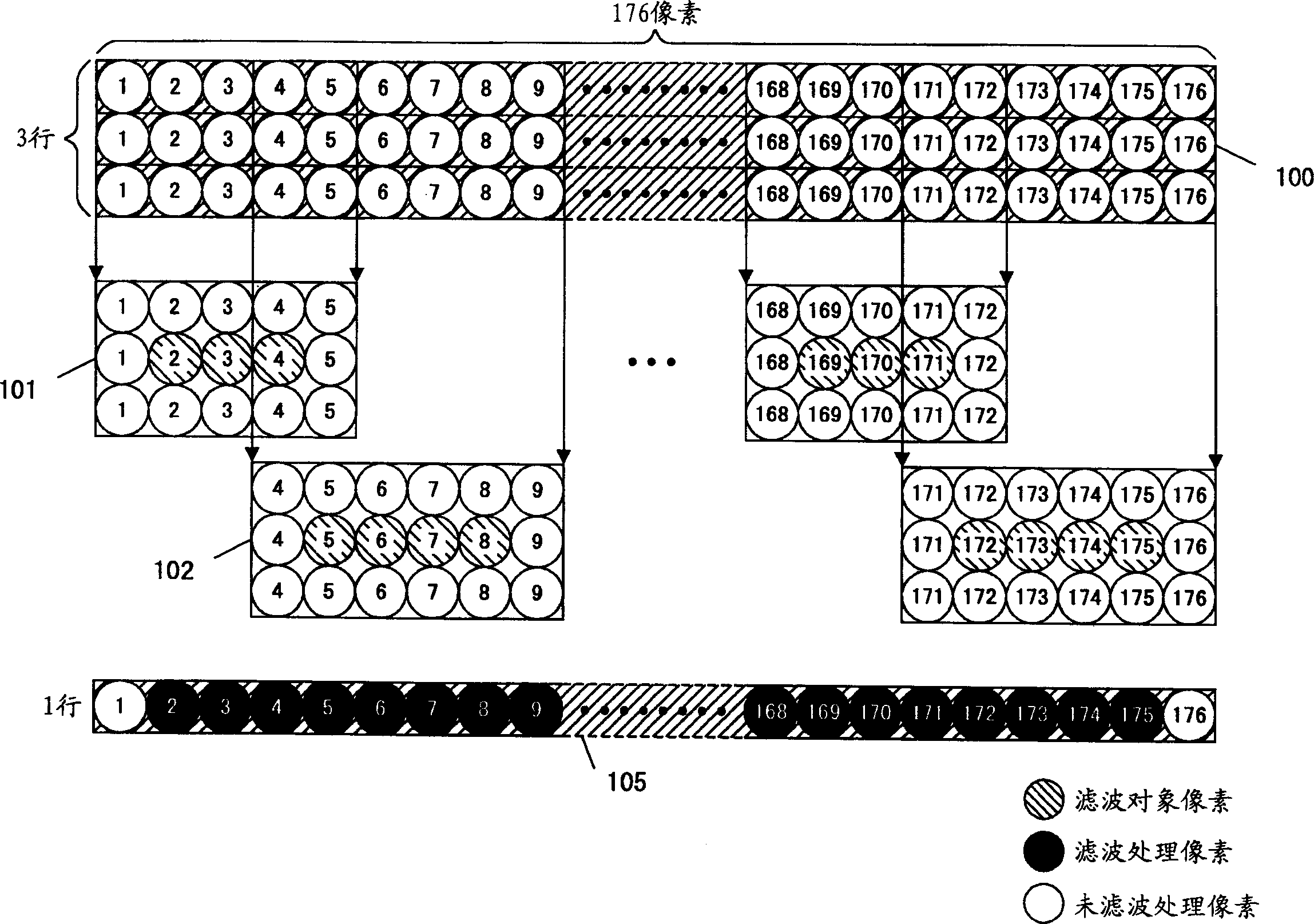

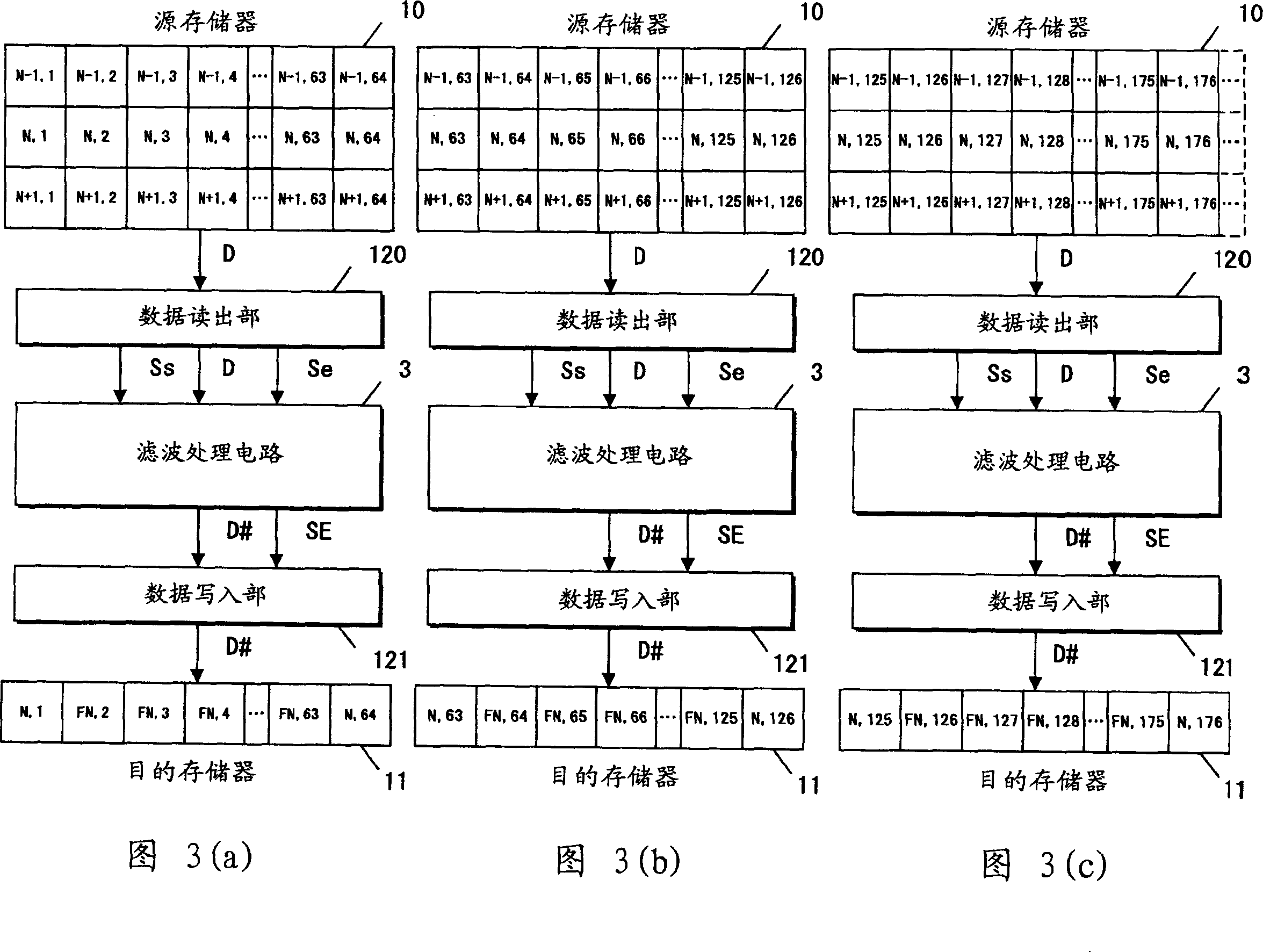

Image processing method and its processor

InactiveCN1499844AIncrease in inhibition areaReduce processing timeTelevision system detailsImage enhancementImaging processingComputer graphics (images)

Owner:PANASONIC CORP

Display panel

ActiveUS9185817B2Increase in inhibition areaIncrease the number ofPrinted circuit assemblingCathode-ray tube indicatorsFace sheetElectrical and Electronics engineering

Owner:LAPIS SEMICON CO LTD

Medical instrument

ActiveUS20140066834A1Stably handle fluidIncrease in inhibition areaTransistorElectrotherapyEngineeringElectrical conductor

A medical instrument includes a multilayer wiring board having first, second and third wirings, a fourth wiring formed in a first wiring layer, and a fifth wiring formed in a second wiring layer. A first via conductor electrically connects the third and fifth wirings. A second via conductor electrically connects the fourth and fifth wirings. The medical instrument further includes first and second transistors, a second transistor, and a capacitor mounted on the first wiring layer side of the multilayer wiring board. The drain and source electrodes of the first transistor are electrically connected to the first and second wirings, respectively. The drain electrode of the second transistor is electrically connected to the second wiring. The source electrode of the second transistor is electrically connected to the third wiring. The first and second electrodes of the capacitor are electrically connected to the first and fourth wirings, respectively.

Owner:COLUMBIA PEAK VENTURES LLC

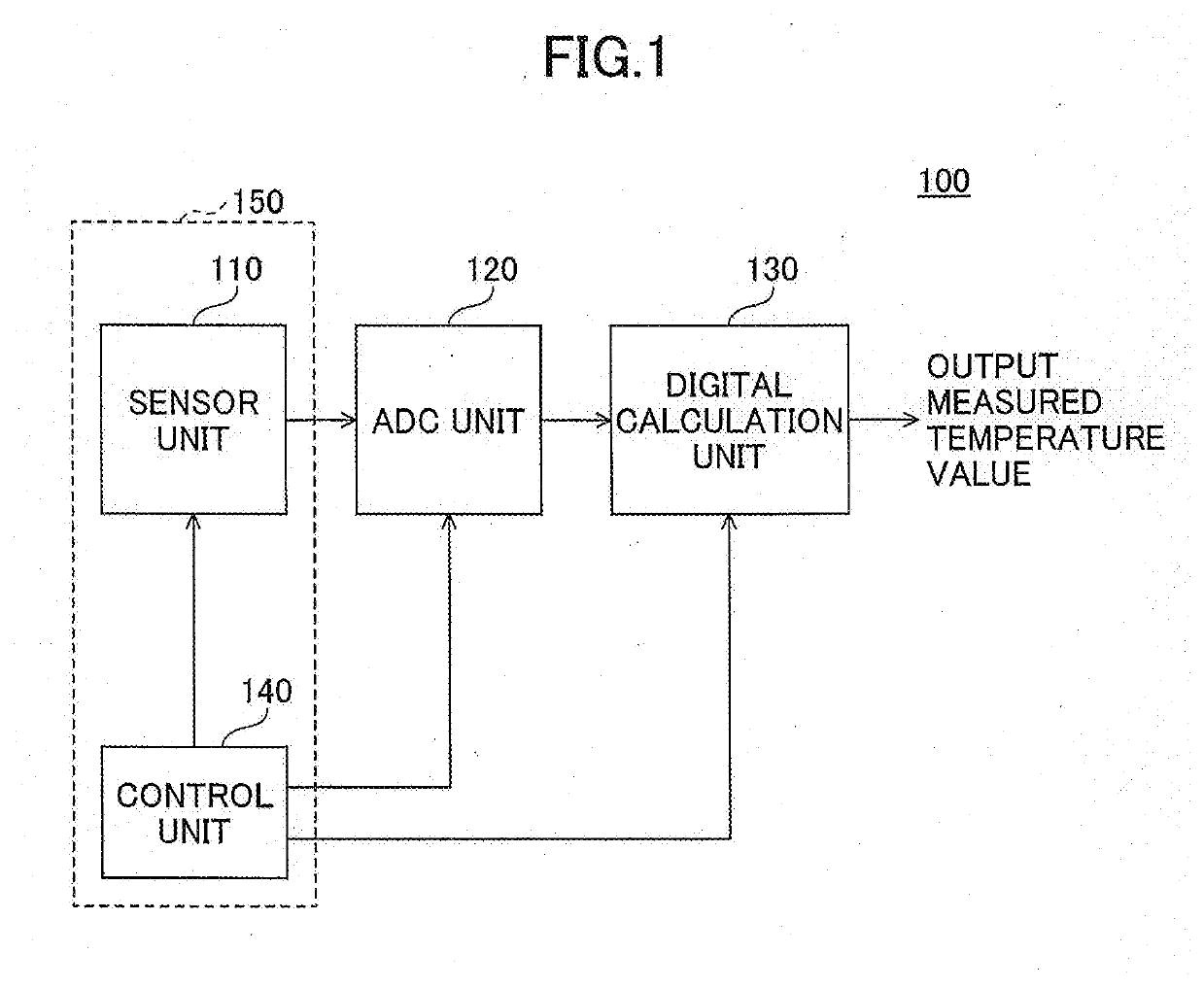

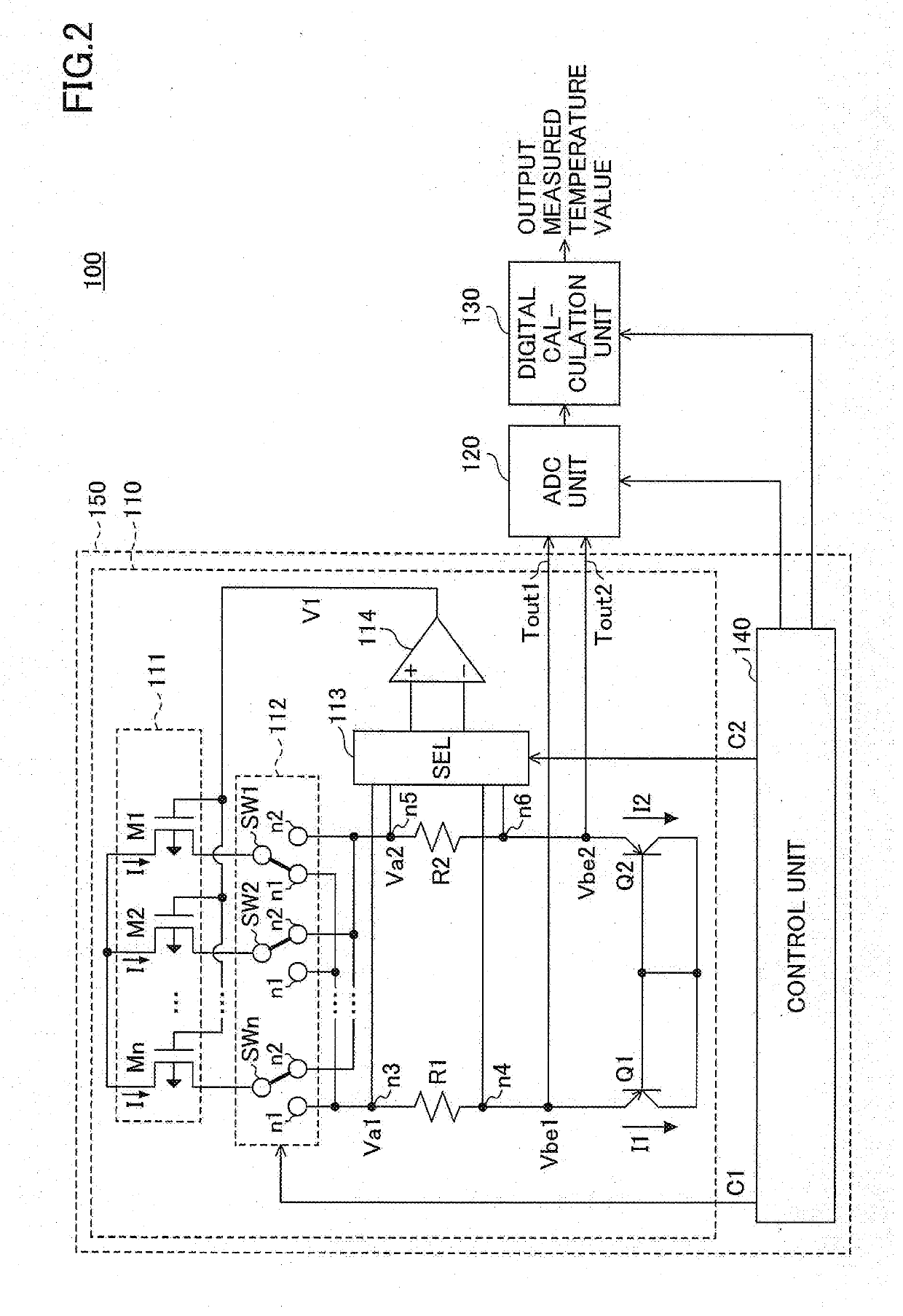

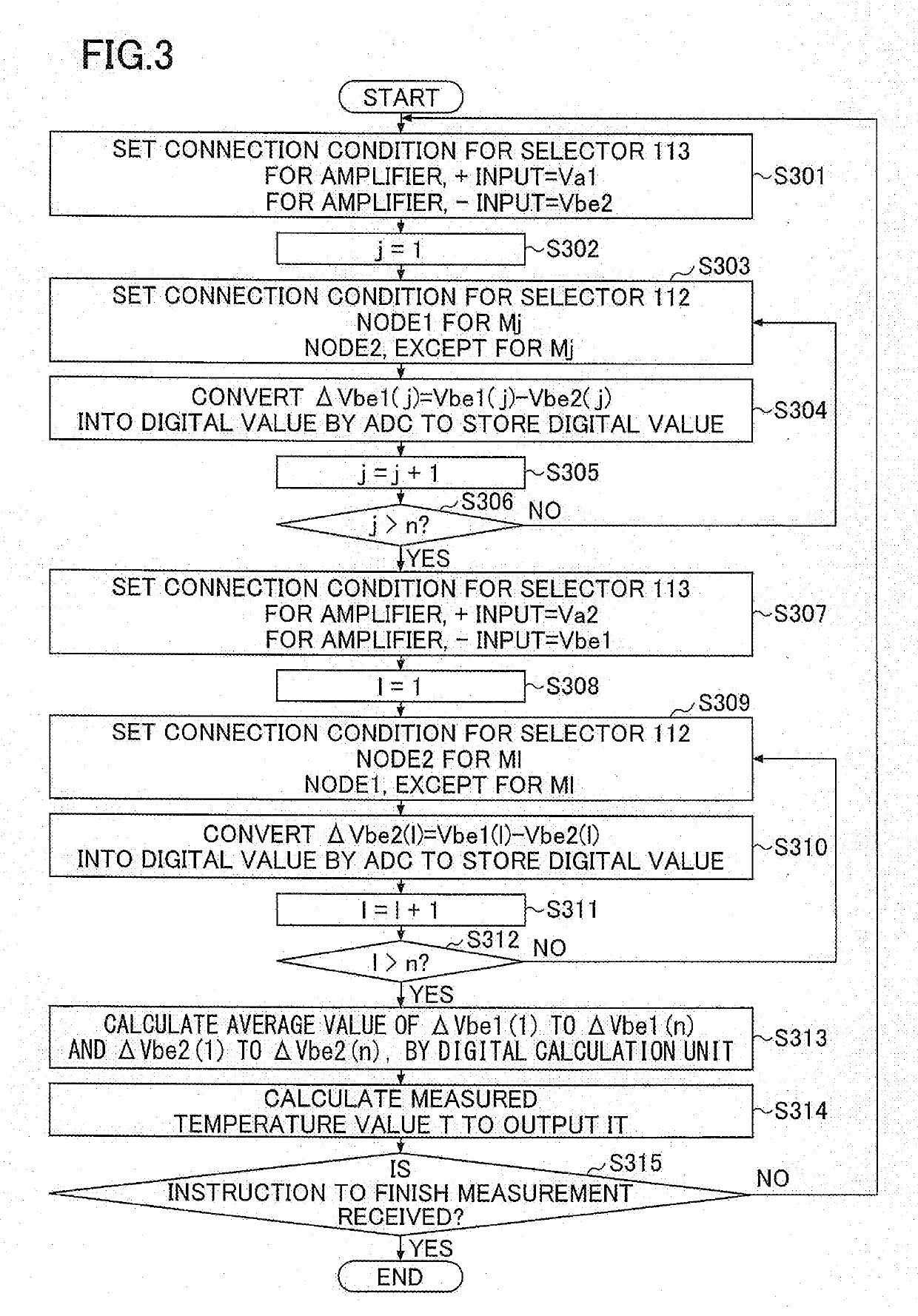

Temperature measuring device and method for measuring temperature

ActiveUS20200064206A1Reduce mismatch effectsSmall sizeThermometer with A/D convertersThermometers using electric/magnetic elementsEngineering physicsMaterials science

A temperature measuring device includes first and second semiconductor elements each of which has a p-n junction, a transistor group including a plurality of transistors of which respective sources are connected to a power source and of which respective gates are connected to each other, the plurality of transistors constituting a current source, the transistor group being configured to output a first current and a second current having a different magnitude from the first current to the first and second semiconductor elements, respectively, and a selector configured to select at least one first transistor and a plurality of second transistors different from the first transistor, from among the plurality of transistors.

Owner:SOCIONEXT INC

Semiconductor circuit apparatus with voltage boost

InactiveUS7525369B2Increase in inhibition areaHigh power supply voltageApparatus without intermediate ac conversionElectronic switchingBoost controllerEngineering

A semiconductor circuit apparatus includes a booster which is connected to a single power supply and outputs a power supply voltage of the power supply or a voltage different from the power supply voltage, and a boost controller which controls whether to output the power supply voltage of the power supply or the voltage different from the power supply voltage.

Owner:RENESAS ELECTRONICS CORP

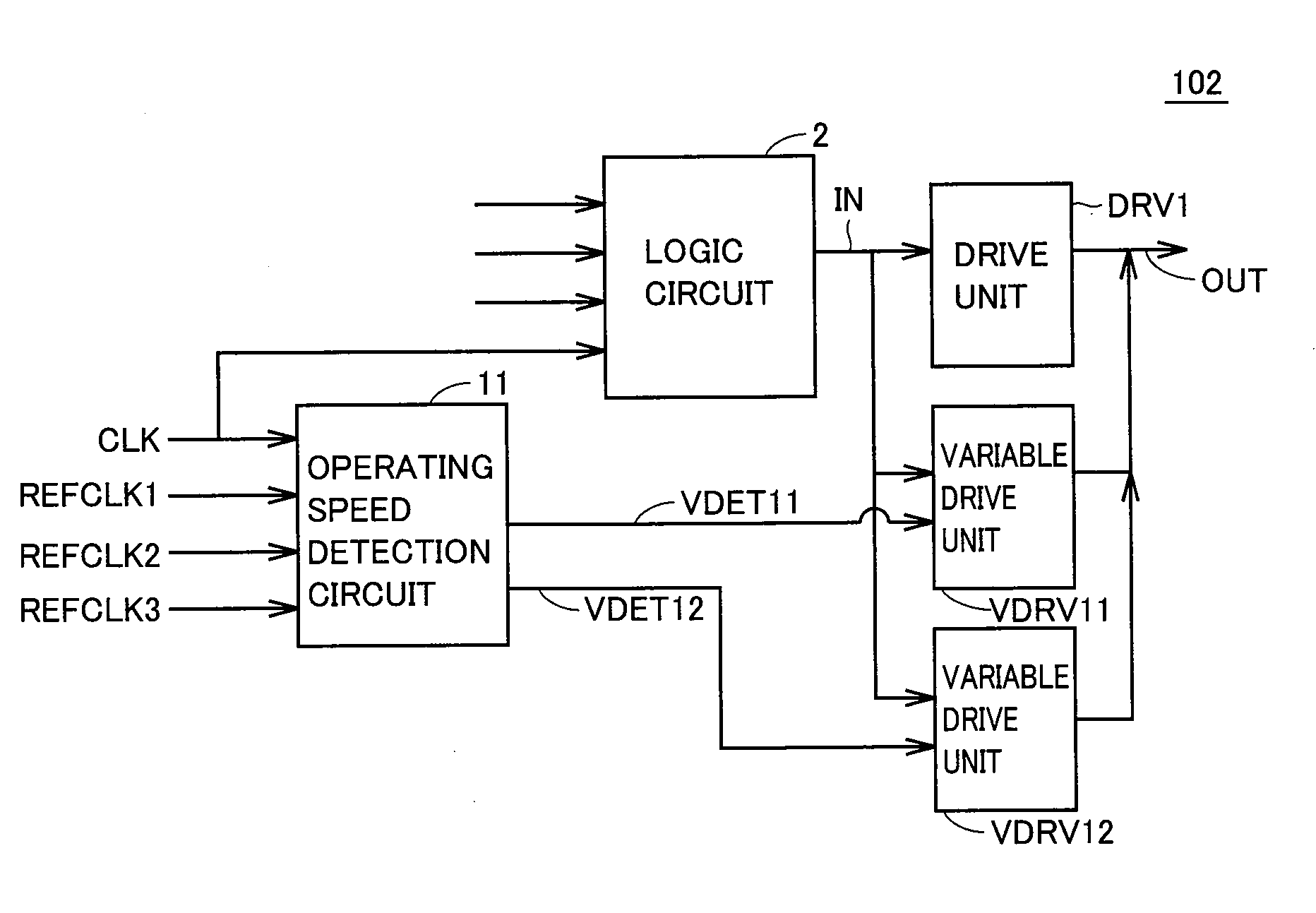

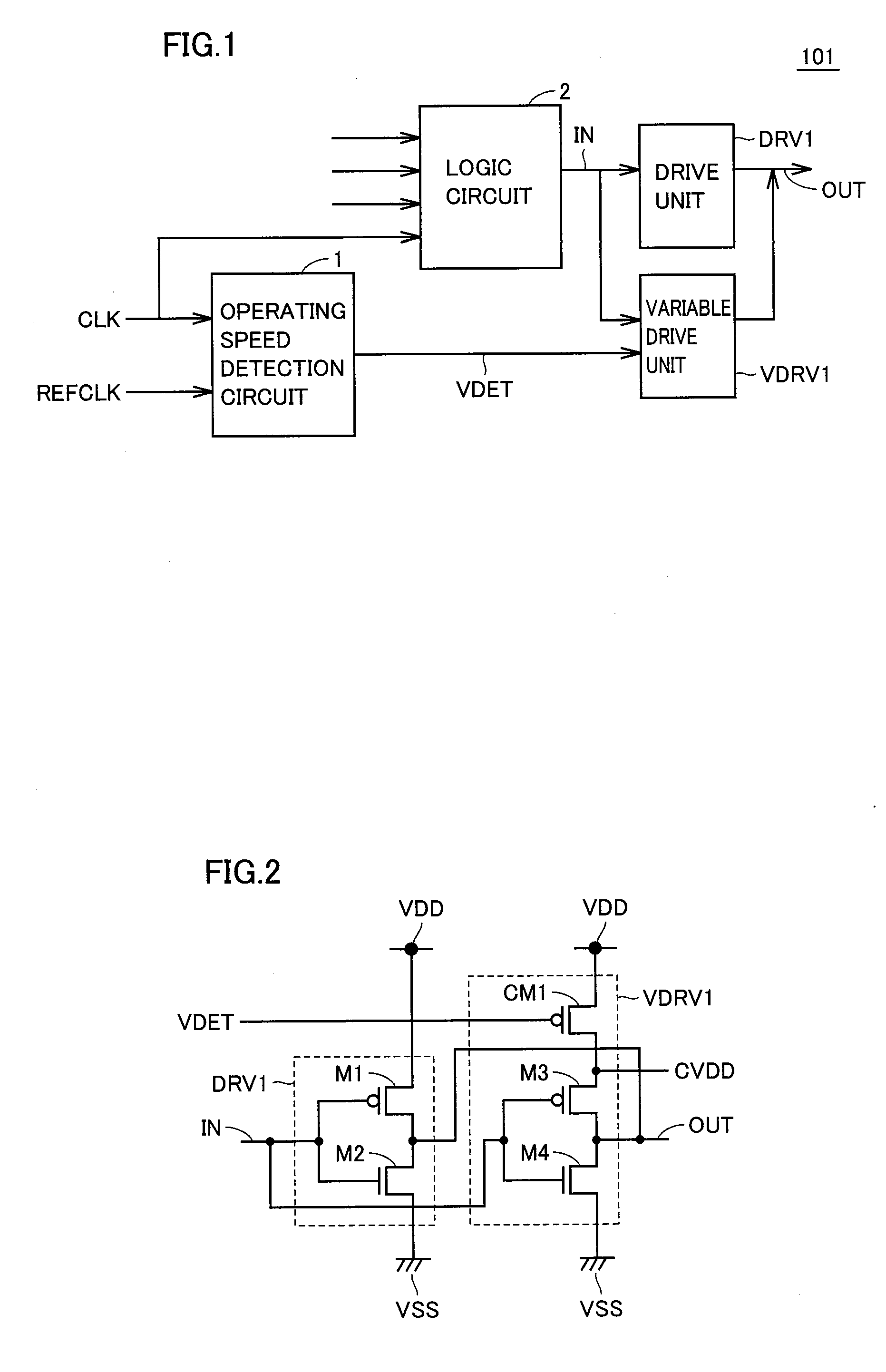

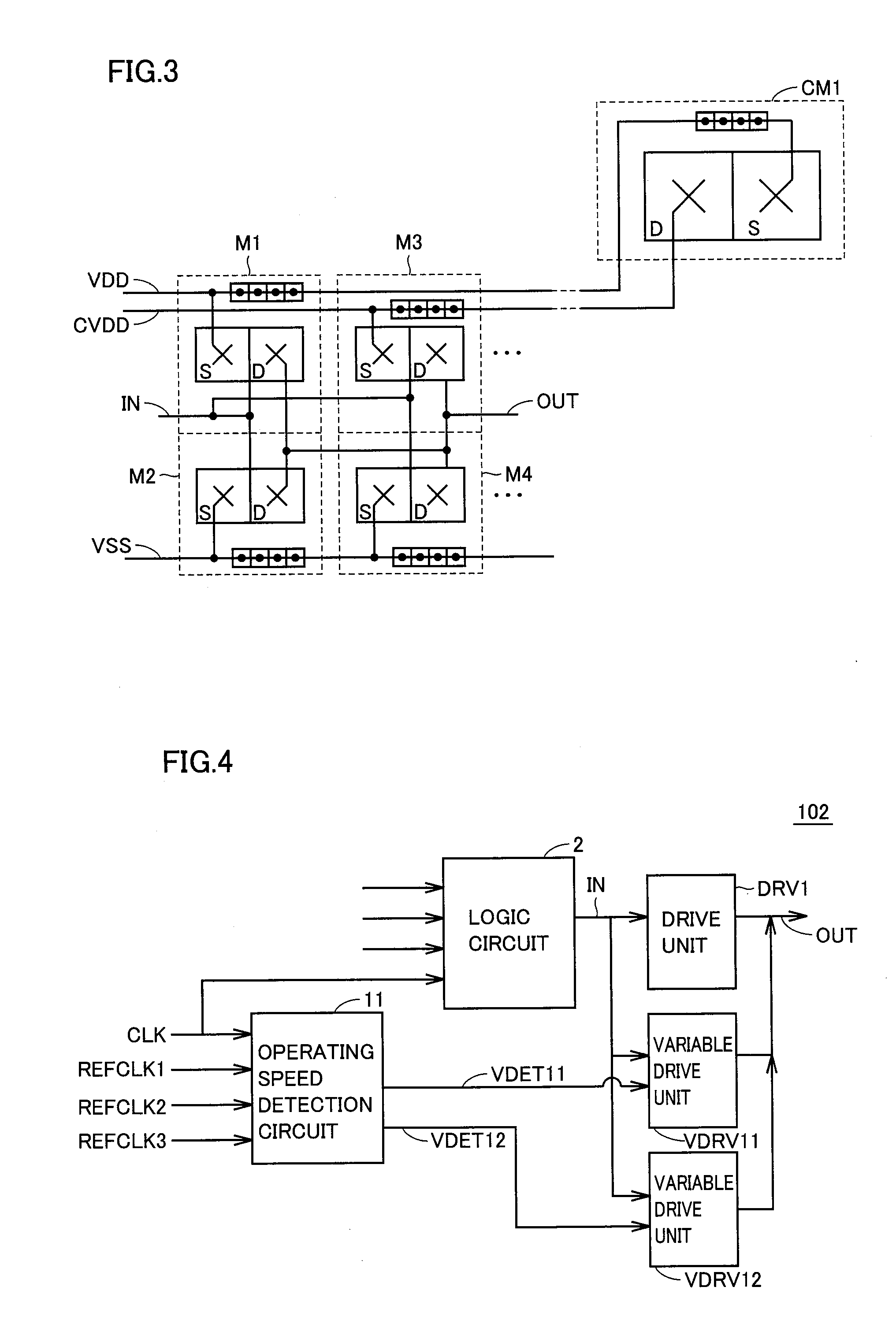

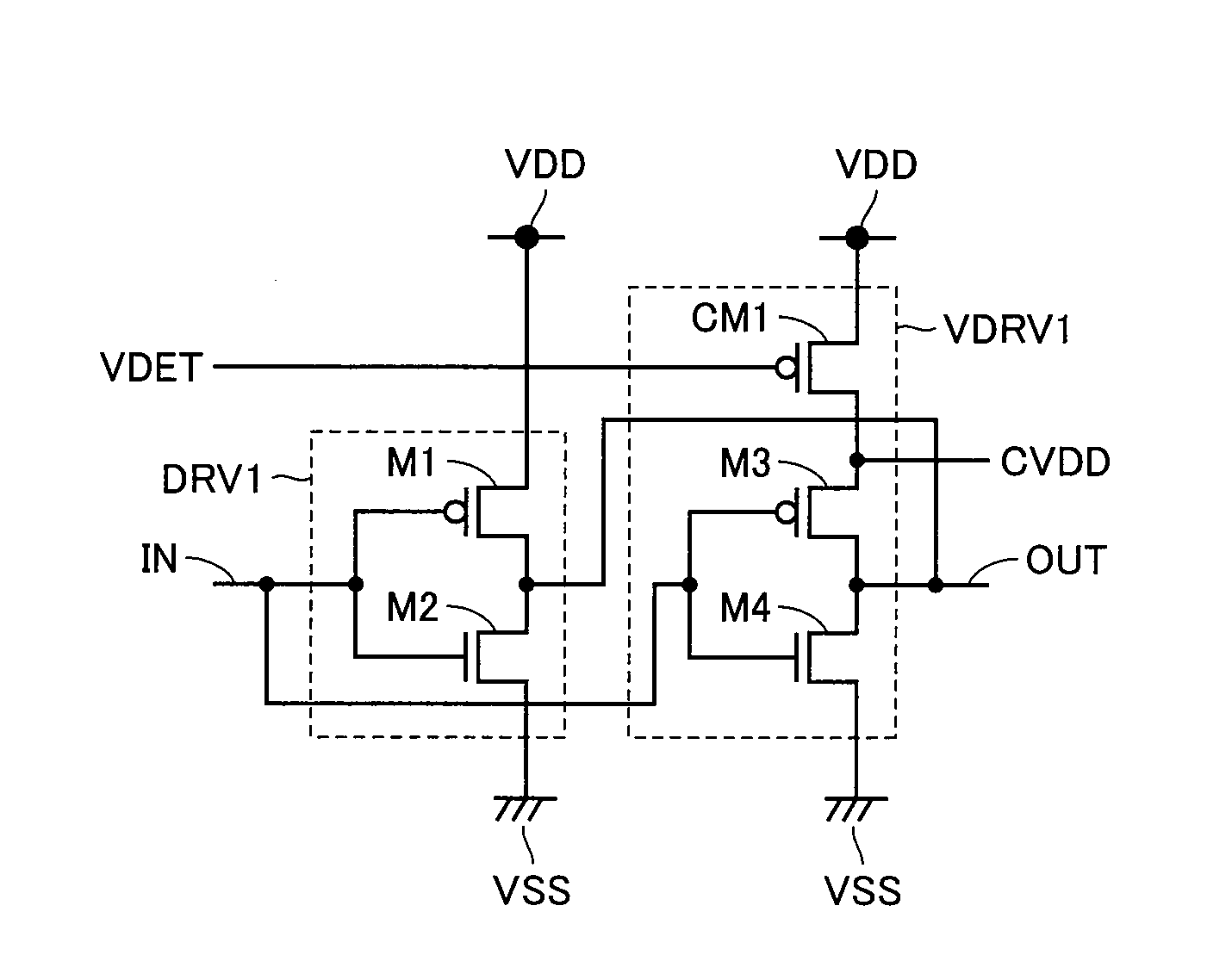

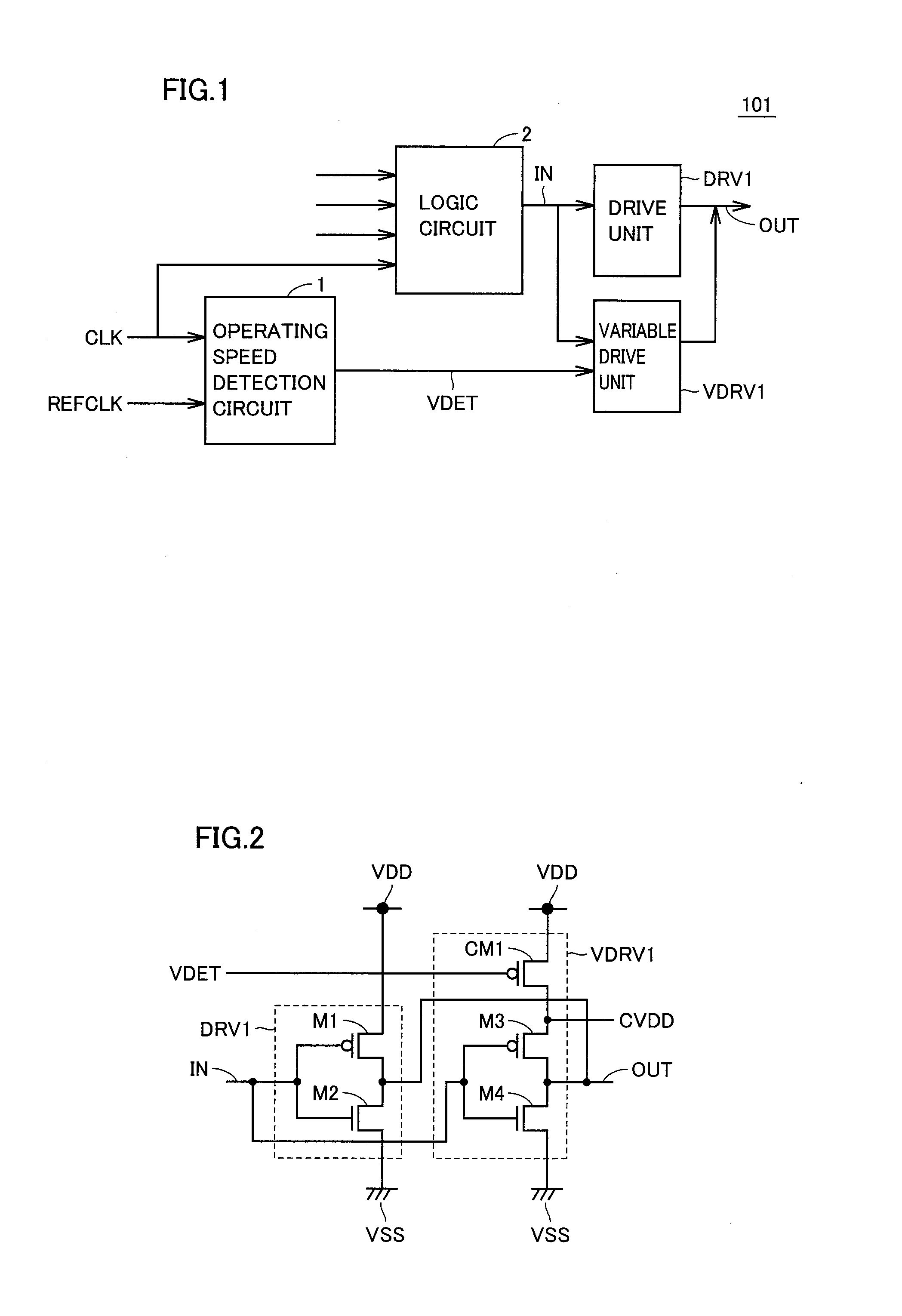

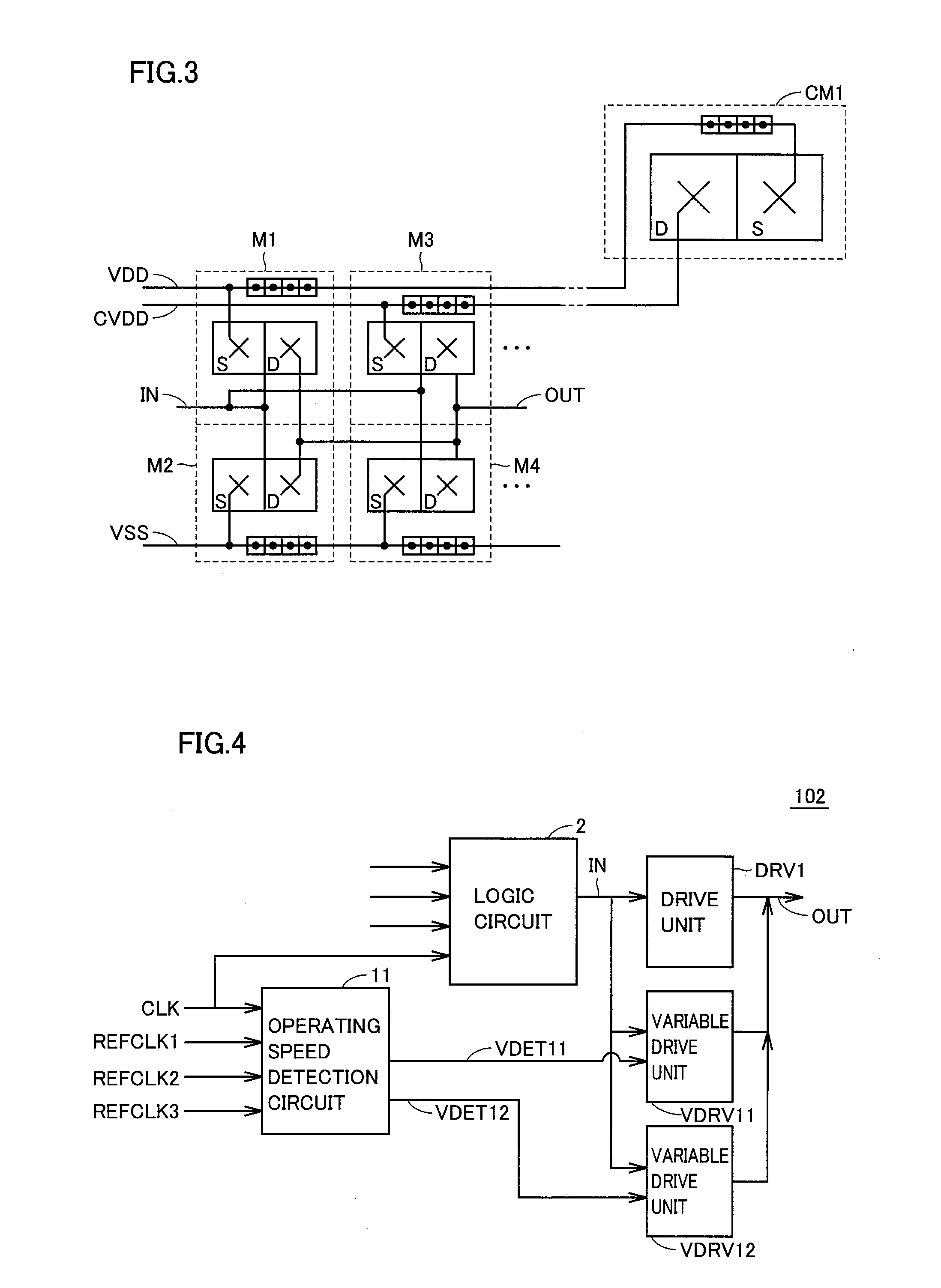

Semiconductor device reducing leakage current of transistor

InactiveUS20090085628A1Total current dropIncrease in inhibition areaPower reduction in field effect transistorsElectric pulse generatorControl signalDevice material

A semiconductor device includes: a first transistor having a control electrode coupled to an input node receiving a signal synchronized with a clock, a first conductive electrode coupled to an output node, and a second conductive electrode; a second transistor having a control electrode coupled to the input node, a first conductive electrode coupled to the output node, and a second conductive electrode coupled to a power supply node; and a first switch element connected between the power supply node and the second conductive electrode of the second transistor and turned on and off based on a first control signal indicating a detection result of a frequency of the clock.

Owner:RENESAS TECH CORP

Semiconductor device, liquid discharge head, and liquid discharge apparatus

ActiveUS9393779B2Increase in inhibition areaEnsure resistance to static electricity appliedPrintingResidual vibrationDriven element

A semiconductor device which is provided to correspond to each of a plurality of nozzles discharging a liquid and controls a plurality of drive elements causing a liquid to be discharged from each nozzle by an application of a drive signal includes a detection circuit which detects a residual vibration signal of the drive element, an output terminal which is provided to correspond to each of the plurality of drive elements, a discharge transistor which controls an application of the drive signal to the drive element through the output terminal, and a detection transistor which controls an application of the residual vibration signal to the detection circuit through the output terminal, in which the detection transistor is smaller than the discharge transistor in size, and the discharge transistor is disposed between the detection transistor and the output terminal.

Owner:SEIKO EPSON CORP

Electro-optical device and electronic apparatus

ActiveUS10353254B2Increase in inhibition areaCross-talk/noise/interference reductionPrinted circuit aspectsEngineeringElectric devices

Owner:SEIKO EPSON CORP

Semiconductor device and electronic device

InactiveUS20190341913A1Reduce needIncrease in inhibition areaPower reduction in field effect transistorsStatic indicating devicesSemiconductorTransistor

An object is to provide a level shift circuit that operates stably. A semiconductor device includes a level shift circuit including first to fourth transistors and a buffer circuit. One of a source and a drain (S / D) of the first transistor is connected to one of a source and a drain of the second transistor. The other of the source and the drain of the second transistor is connected to one of a source and a drain of the third transistor. A gate of the first transistor and a gate of the fourth transistor are connected to the other of the source and the drain of the second transistor and the one of the source and the drain of the third transistor. A gate of the third transistor is connected to a wiring to which an input signal is input. An input terminal of the buffer circuit is connected to one of a source and a drain of the fourth transistor. An output terminal of the buffer circuit is connected to a gate of the second transistor and a wiring to which an output signal is output.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device reducing leakage current of transistor

ActiveUS20100164613A1Total current dropIncrease in inhibition areaPower reduction in field effect transistorsSolid-state devicesControl signalEngineering

A semiconductor device includes: a first transistor having a control electrode coupled to an input node receiving a signal synchronized with a clock, a first conductive electrode coupled to an output node, and a second conductive electrode; a second transistor having a control electrode coupled to the input node, a first conductive electrode coupled to the output node, and a second conductive electrode coupled to a power supply node; and a first switch element connected between the power supply node and the second conductive electrode of the second transistor and turned on and off based on a first control signal indicating a detection result of a frequency of the clock.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and electronic device

InactiveUS10355673B2Reduce needIncrease in inhibition areaPower reduction in field effect transistorsStatic indicating devicesPower semiconductor deviceEngineering

An object is to provide a level shift circuit that operates stably. A semiconductor device includes a level shift circuit including first to fourth transistors and a buffer circuit. One of a source and a drain (S / D) of the first transistor is connected to one of a source and a drain of the second transistor. The other of the source and the drain of the second transistor is connected to one of a source and a drain of the third transistor. A gate of the first transistor and a gate of the fourth transistor are connected to the other of the source and the drain of the second transistor and the one of the source and the drain of the third transistor. A gate of the third transistor is connected to a wiring to which an input signal is input. An input terminal of the buffer circuit is connected to one of a source and a drain of the fourth transistor. An output terminal of the buffer circuit is connected to a gate of the second transistor and a wiring to which an output signal is output.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com