Built-in self test and built-in self-repairing technology of TSV (Through Silicon Via) interconnection of 3D chip

A built-in self-test and built-in self-repair technology, applied in the field of built-in self-test and built-in self-repair technology, can solve problems such as the accuracy of the RC model that needs to be demonstrated, so as to reduce dependence, strengthen flexibility, and improve finished products rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

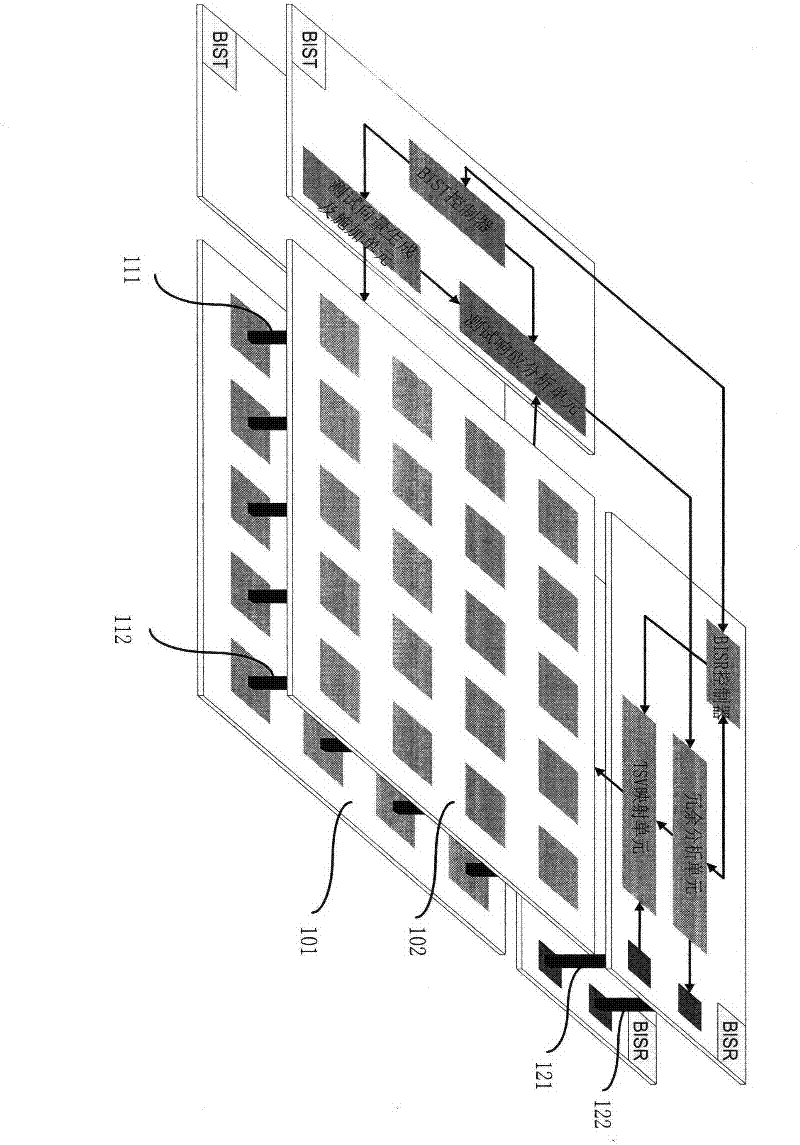

[0017] The built-in self-test and built-in self-repair technology of 3D chip TSV interconnection provided by the present invention will be described in detail below with reference to the accompanying drawings.

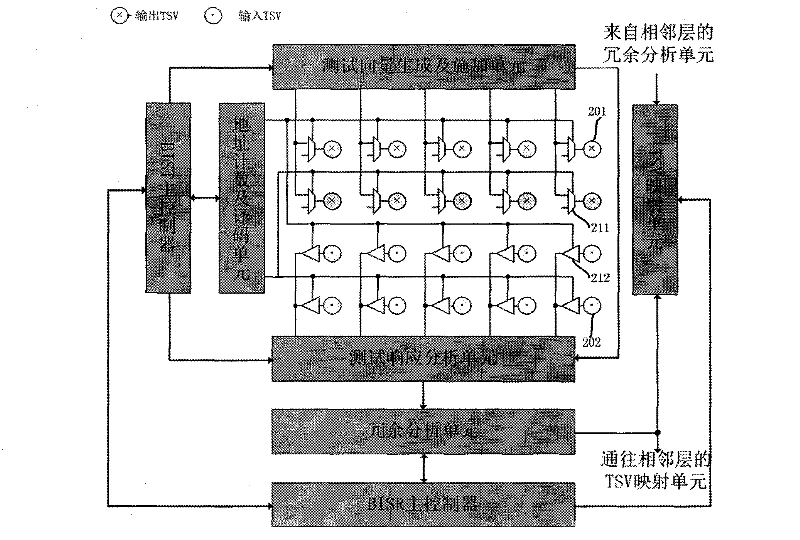

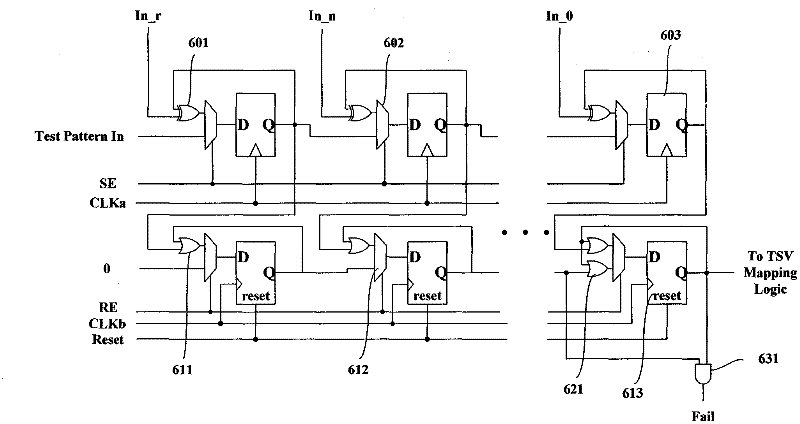

[0018] The technology mainly includes two parts, TSV built-in self-test circuit (BIST) and TSV built-in self-repair circuit (BISR). The BIST part includes the following parts: BIST controller, test vector generation and sending unit, address counting and decoding unit, test response analysis unit; BISR includes the following parts: BISR controller, TSV mapping unit, TSV redundancy analysis unit . The following describes the design and implementation of the main modules in conjunction with the accompanying drawings:

[0019] 1. The BIST main controller is used to control the work of other modules in the BIST circuit, and its state transition diagram is as follows Figure 4shown. After receiving the power-on reset signal (Power on Reset), the controller enters the INI...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More