Method for improving compiling speed of silicon-oxide-nitride-oxide-silicon (SONOS) structure device by using stress technology

A technology of stress and technology, which is applied in the field of using stress technology to improve the compilation speed of SONOS structure devices, can solve the problems such as the effect of stress transfer is not obvious, achieve the effect of improving carrier mobility, the effect is obvious, and the interface state is improved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

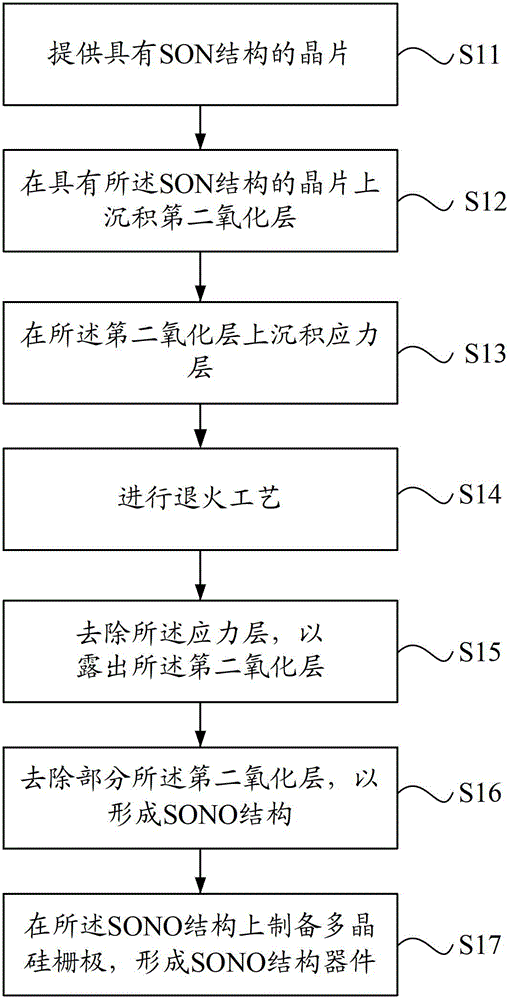

[0046] Please refer to figure 2 and Figure 3a-Figure 3f ,in, figure 2 It is a flowchart of a method for improving the compiling speed of a SONOS structure device using stress technology in the first embodiment of the present invention, Figure 3a-Figure 3f It is a schematic diagram of the process steps of introducing stress in the first embodiment of the present invention.

[0047] first reference figure 2 , the method for improving the compiling speed of a SONOS structure device by using the stress technique comprises the following steps:

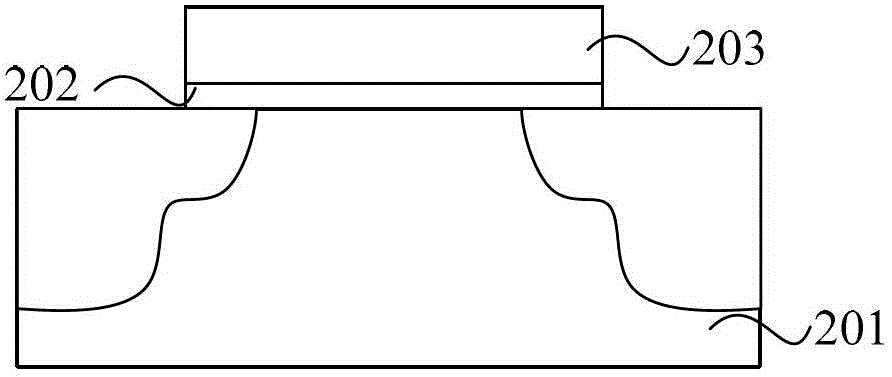

[0048] Step S11, providing a wafer with a SON structure, the SON structure is a silicon semiconductor substrate, a first oxide layer, and a storage nitride layer in sequence from bottom to top;

[0049] Step S12, depositing a second oxide layer on the wafer having the SON structure;

[0050] Step S13, depositing a stress layer on the second oxide layer;

[0051] Step S14, performing an annealing process;

[0052] Step S15, remov...

no. 2 example

[0065] Please refer to Figure 4 and Figure 5a-Figure 5f ,in, Figure 4 It is a flowchart of a method for improving the compiling speed of a SONOS structure device using stress technology according to the second embodiment of the present invention, Figure 5a-Figure 5f It is a schematic diagram of the process steps of introducing stress according to the second embodiment of the present invention.

[0066] first reference Figure 4 , the method for improving the compiling speed of a SONOS structure device by using the stress technique comprises the following steps:

[0067] Step S21, providing a wafer with a SON structure, the SON structure is a silicon semiconductor substrate, a first oxide layer and a nitride layer from bottom to top;

[0068] Step S22, depositing a blocking oxide layer on the wafer having the SON structure;

[0069] Step S23, depositing a stress layer on the blocking oxide layer;

[0070] Step S24, performing an annealing process;

[0071] Step S25, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More