Patents

Literature

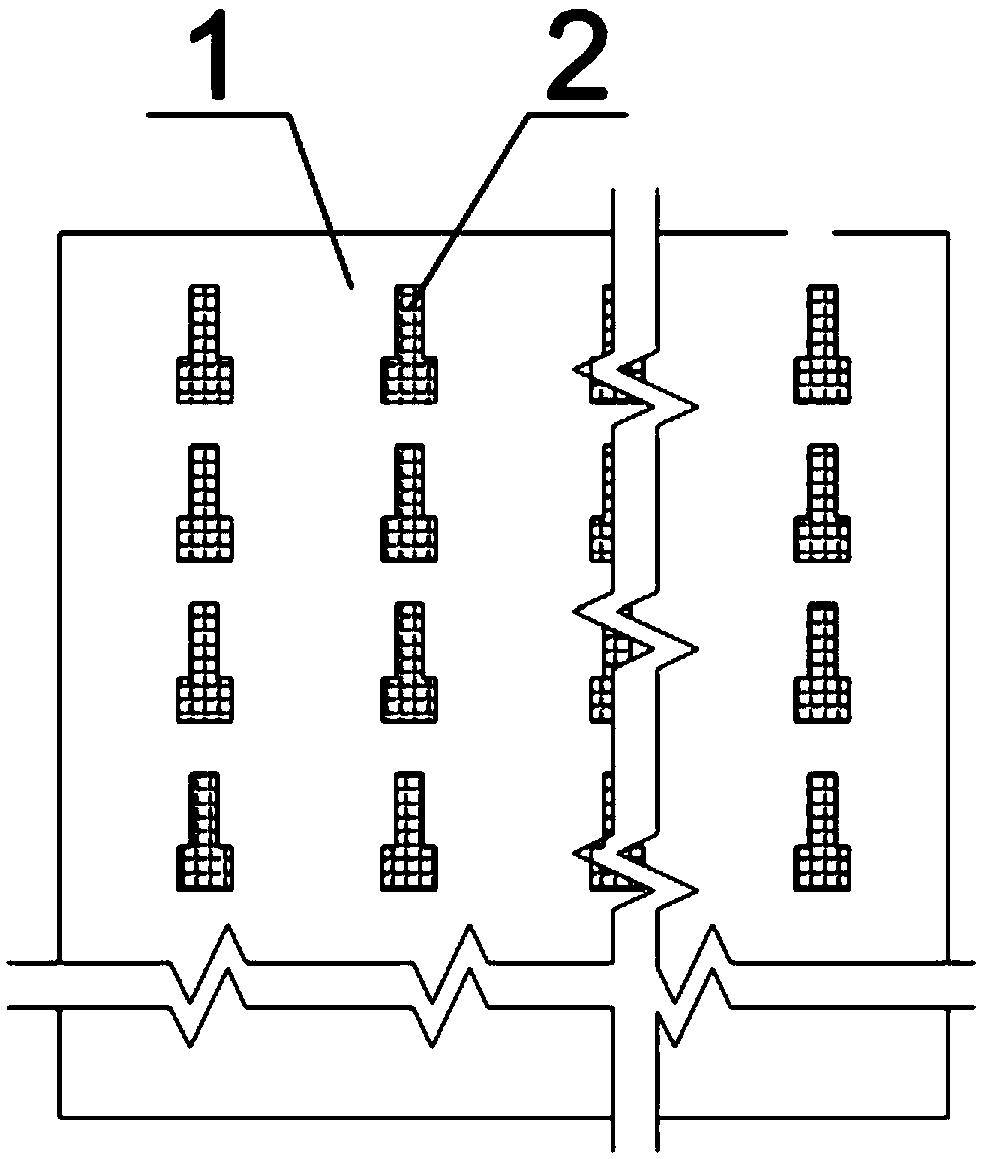

57results about How to "Improve interface state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

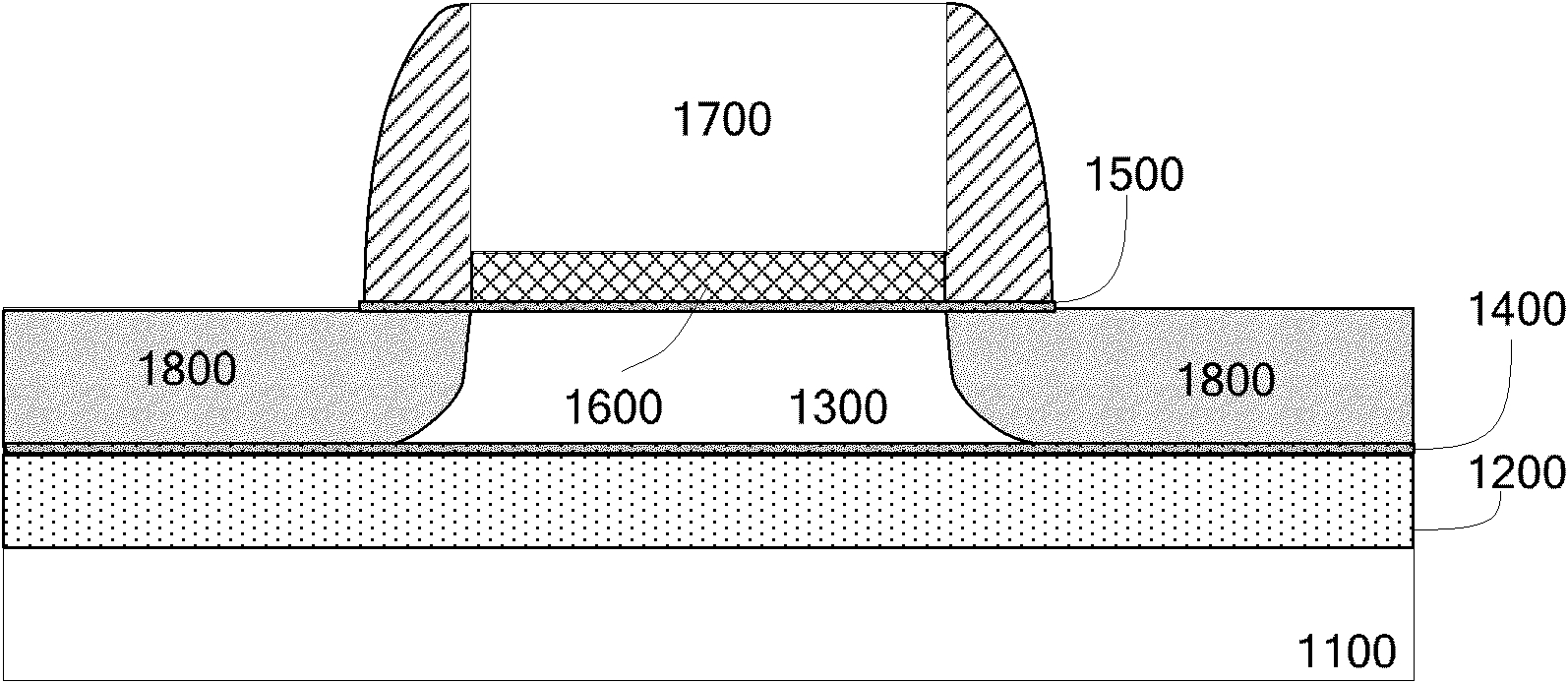

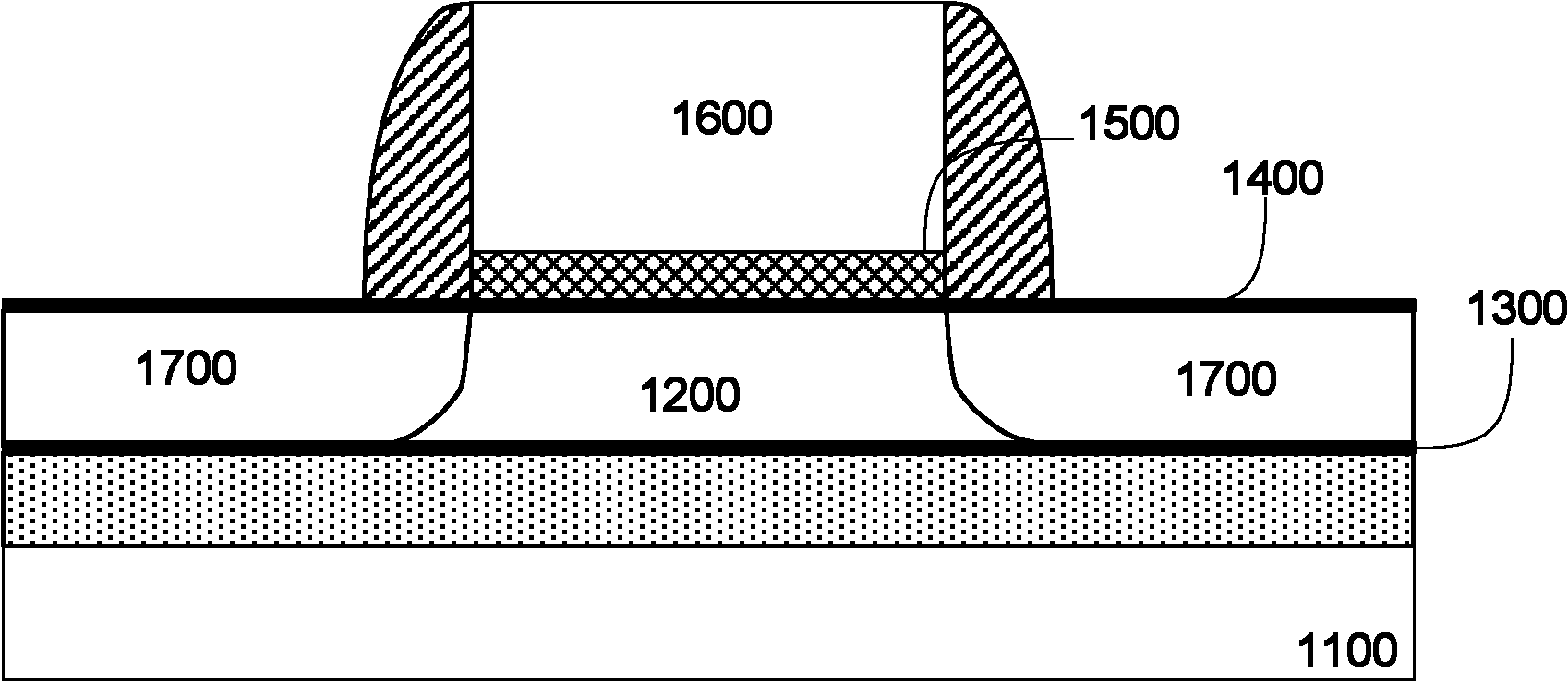

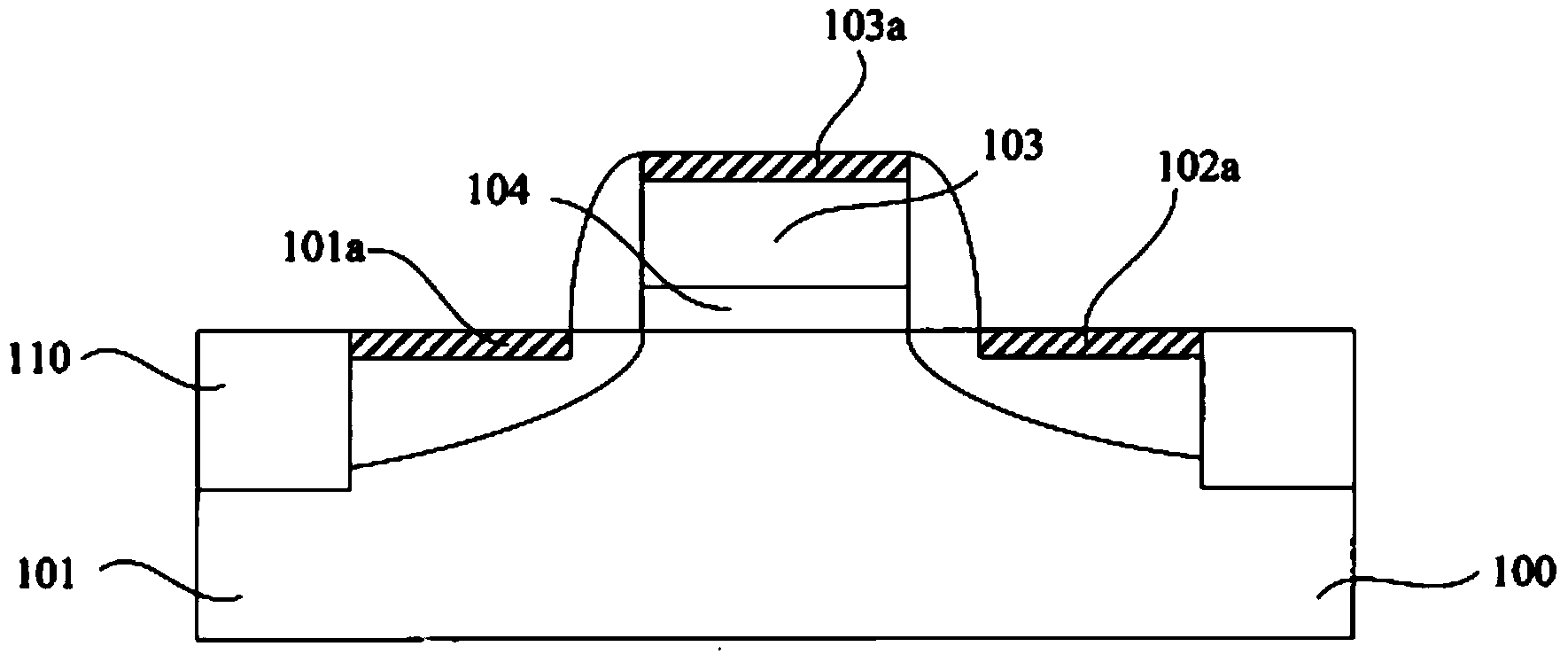

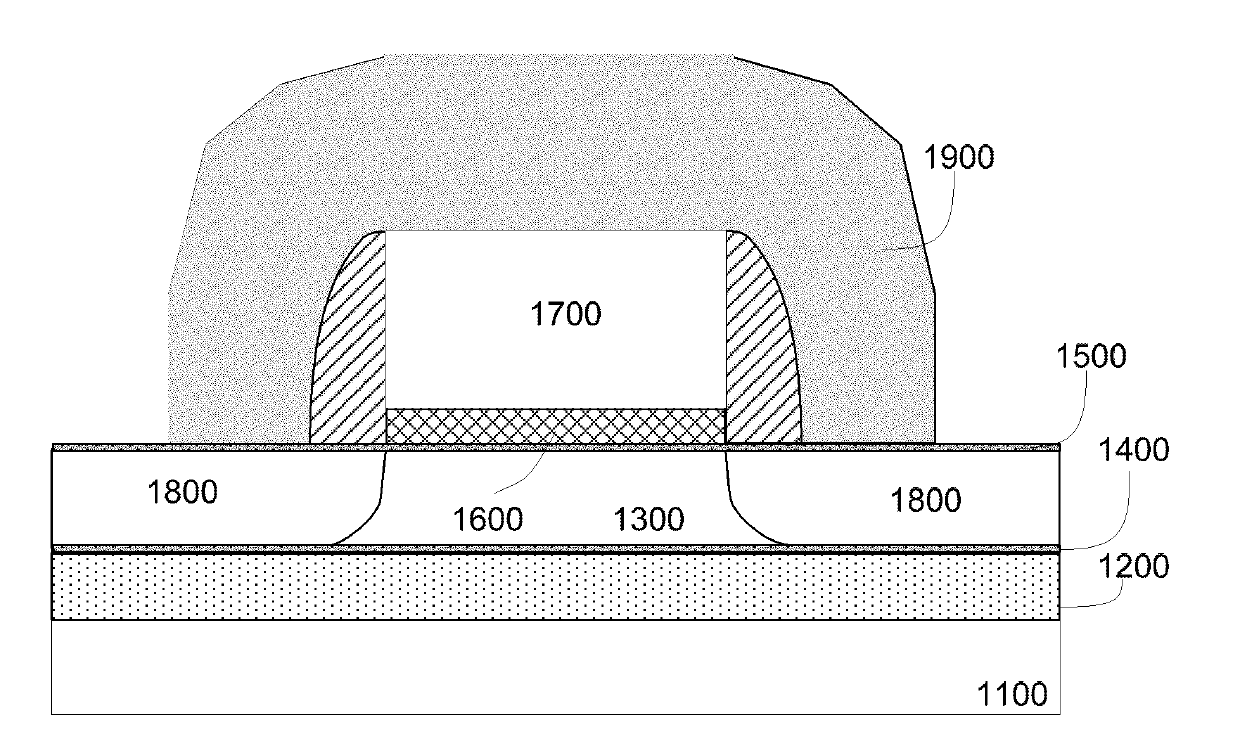

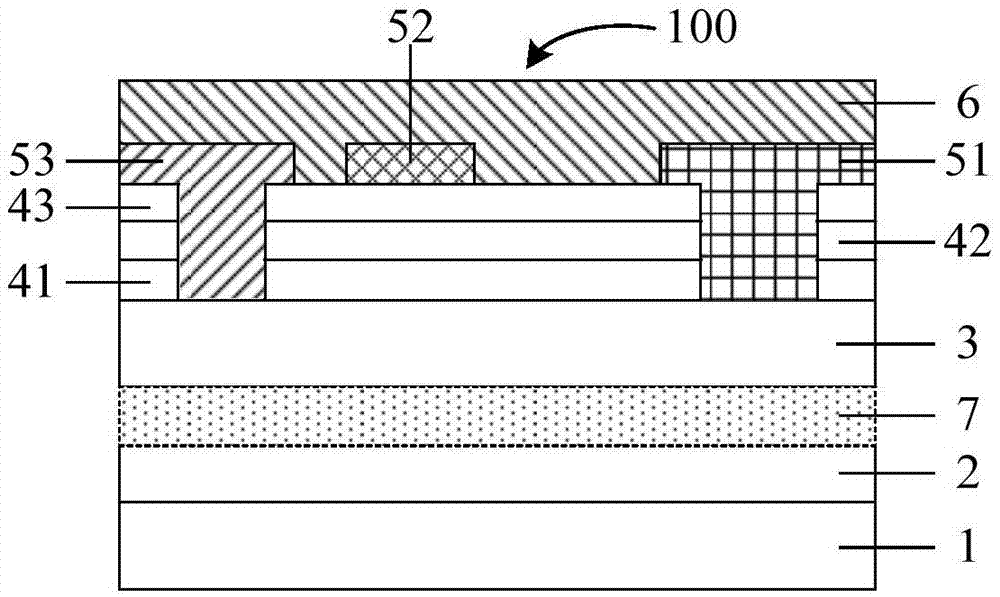

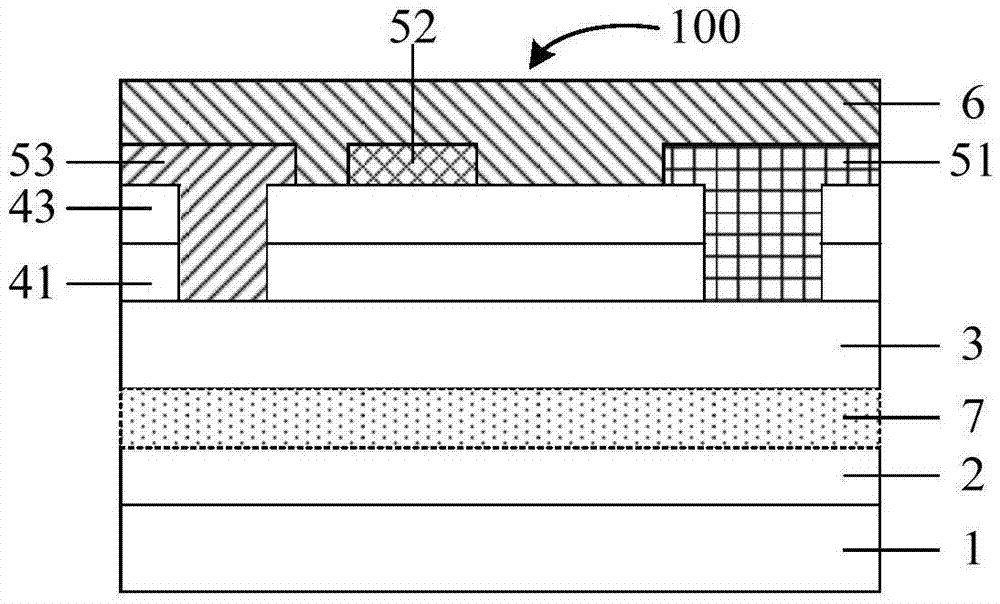

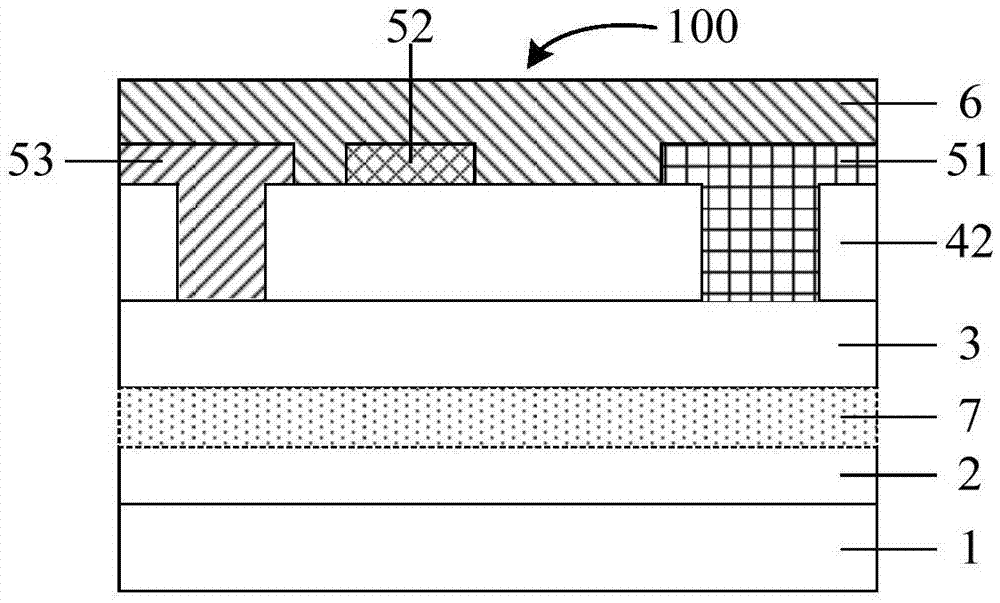

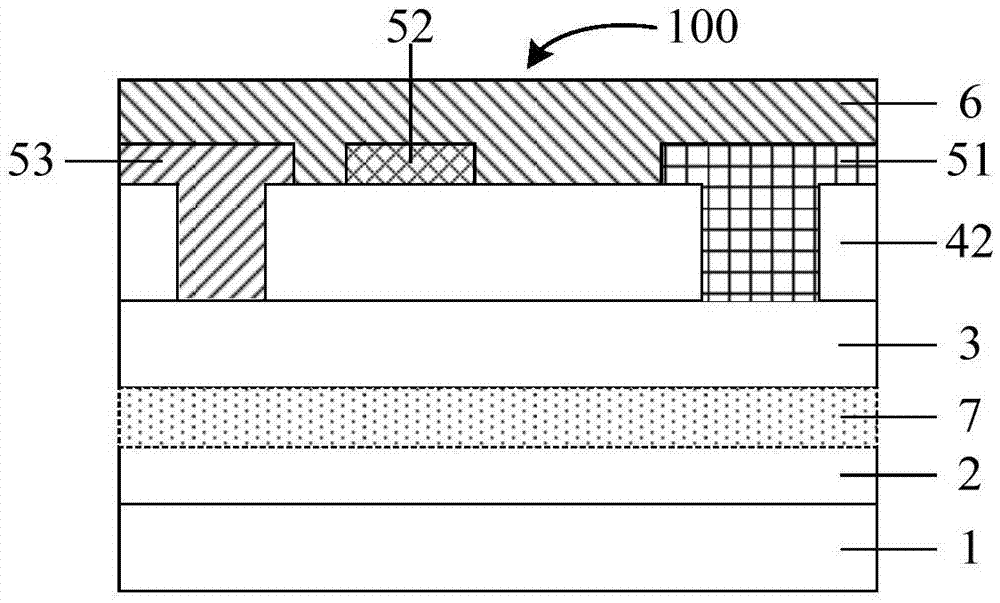

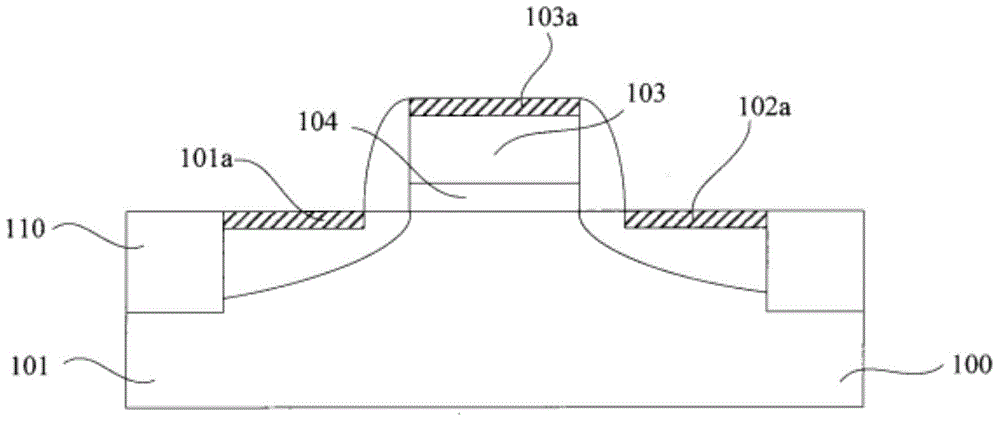

Ge channel device and forming method thereof

ActiveCN102184954AImprove interface stateImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainEngineering

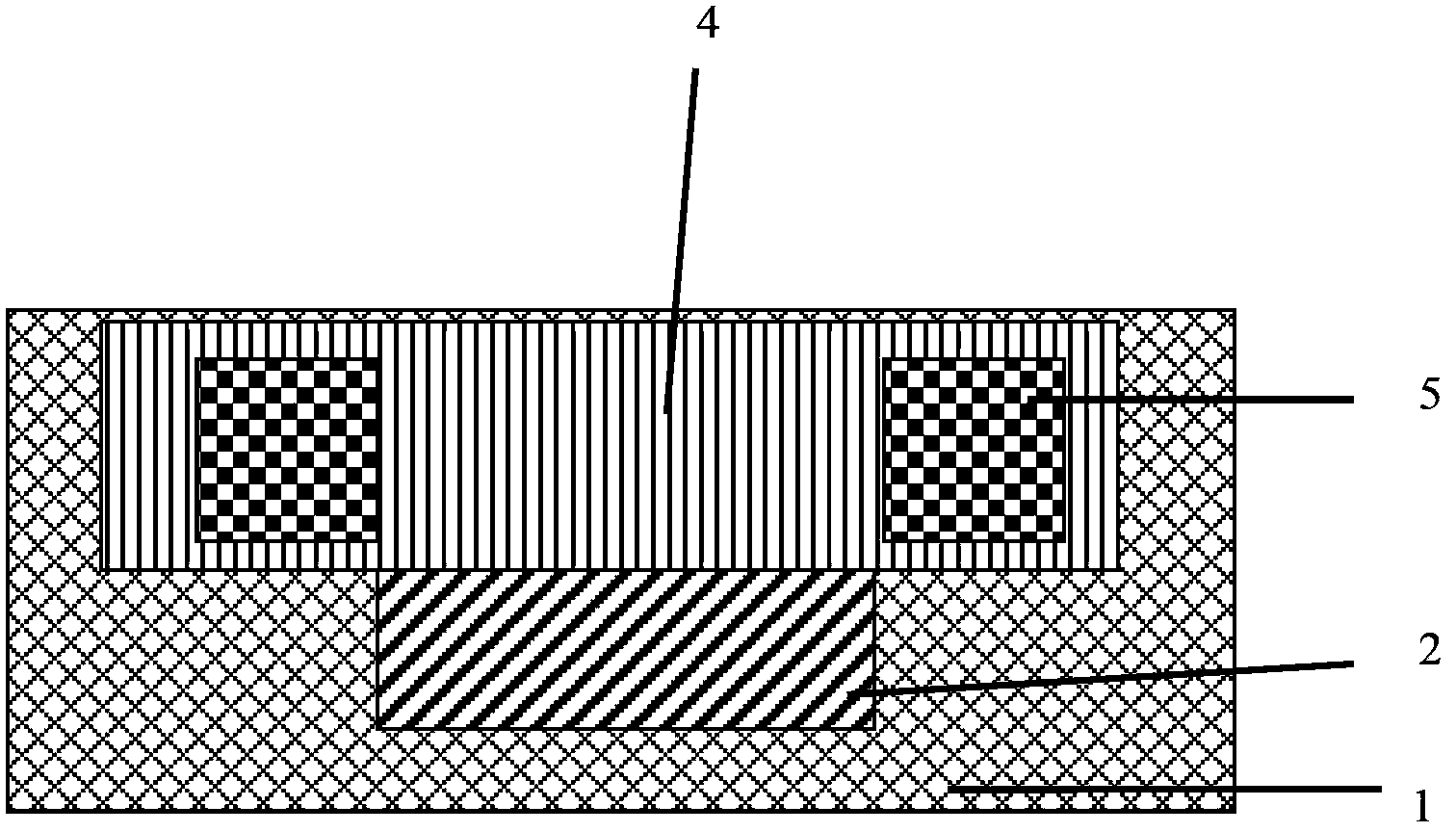

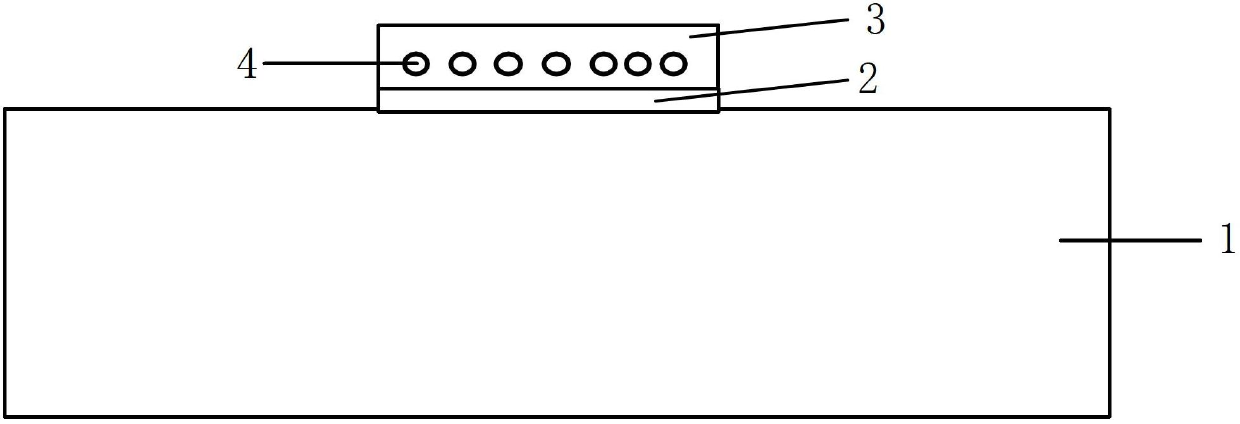

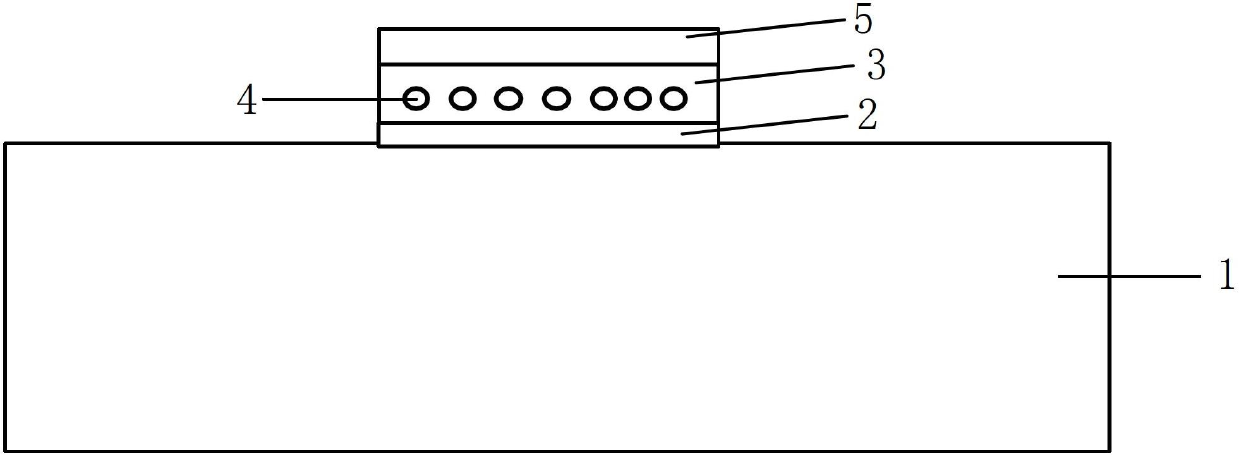

The invention provides a strain Ge channel device. The strain Ge channel device comprises a silicon substrate, a Ge layer, a gate stack, a channel area, a drain electrode and a source electrode, wherein an oxide insulating layer is formed on the surface of the silicon substrate; the Ge layer is formed on the oxide insulating layer; a first thin passivated layer is formed between the Ge layer and the oxide insulating layer; the gate stack is formed on the Ge layer; the channel area is formed below the gate stack; the drain electrode and the source electrode are formed on the two sides of the channel area; and the drain electrode and the source electrode are SiGe1-xCx, so that tensile strain is generated in the channel area, and x is more than or equal to 0 and less than or equal to 1. The Ge channel device consisting of the SiGe1-xCx source electrode and drain electrode formed through the embodiment of the invention has a simple structure and is low in process difficulty and convenientto form. In addition, the tensile strain can be generated in the channel area of the Ge channel device through the SiGe1-xCx source electrode and drain electrode formed through the embodiment of the invention, and then the performance of the Ge channel device is improved.

Owner:TSINGHUA UNIV

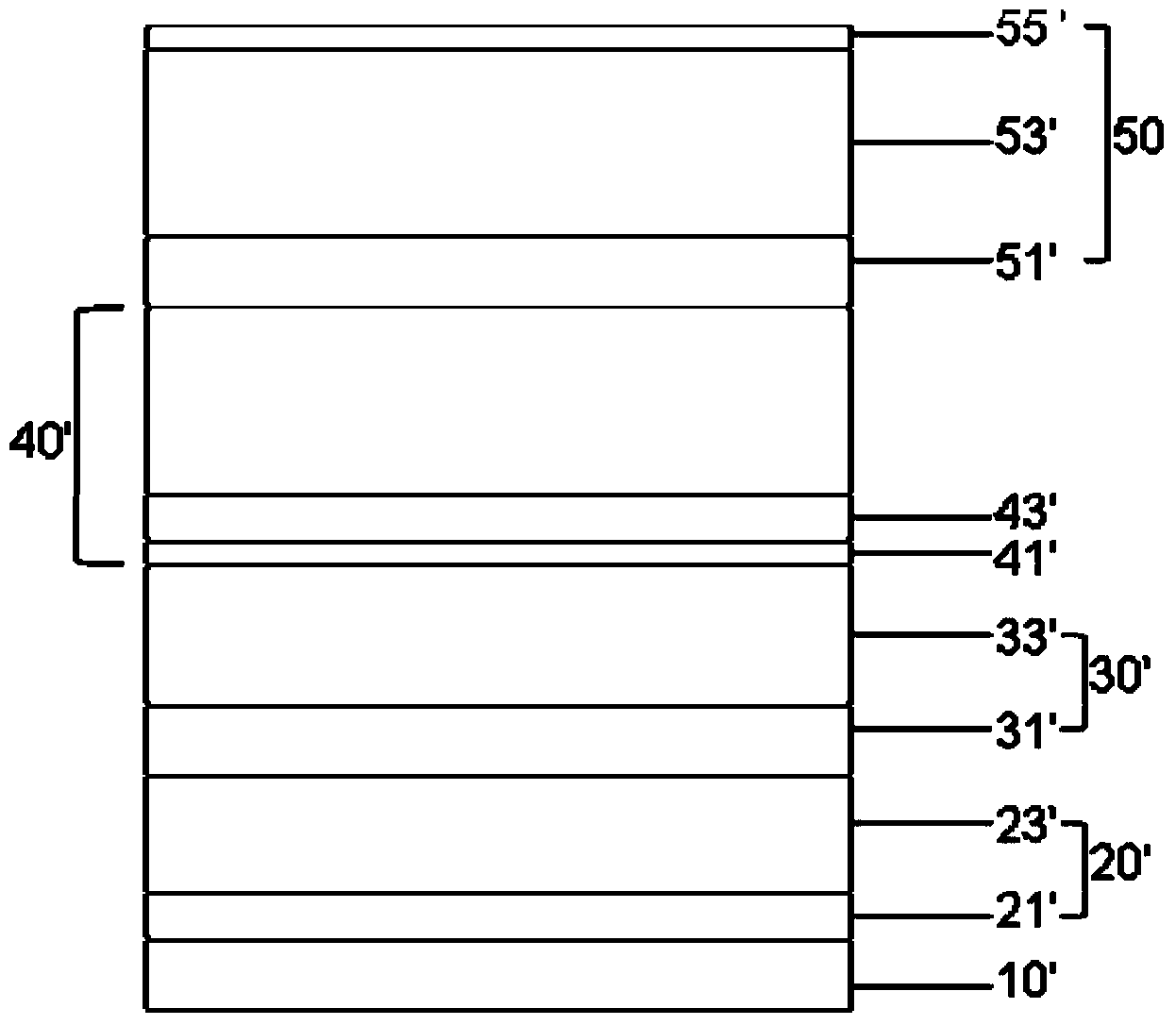

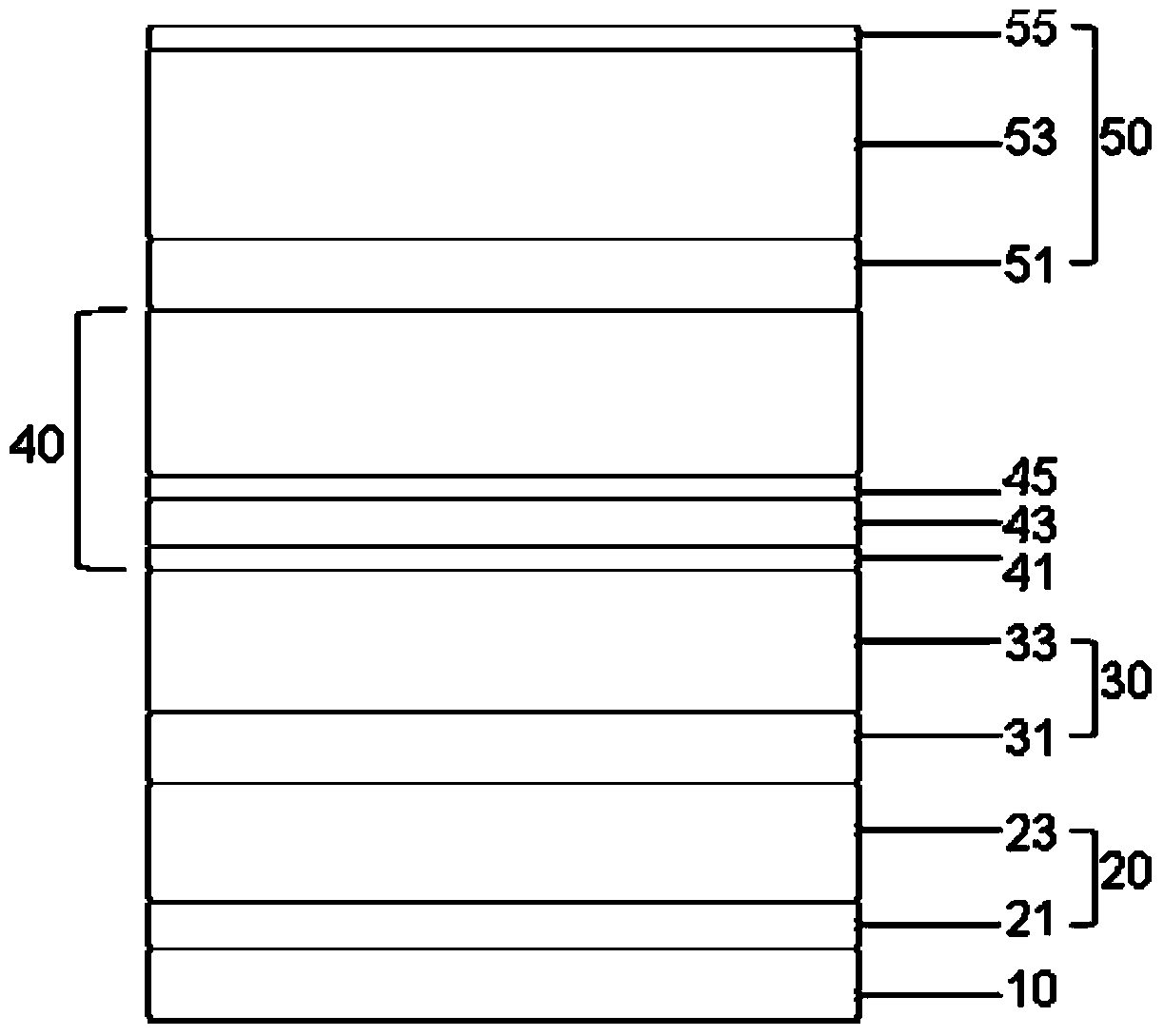

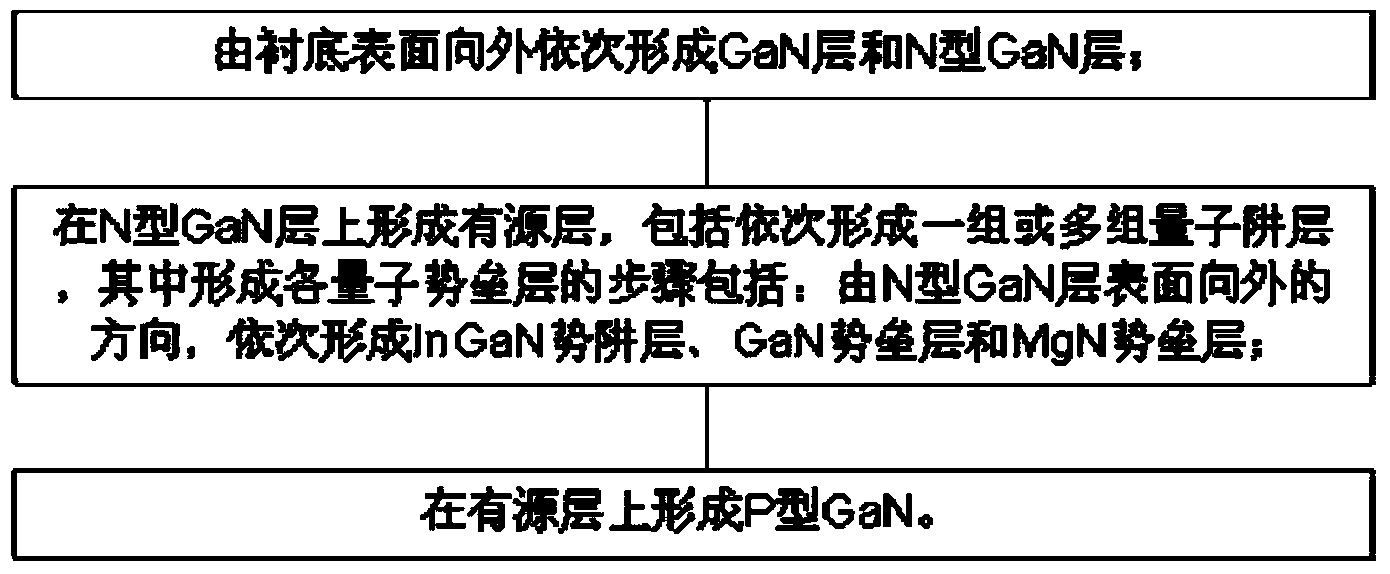

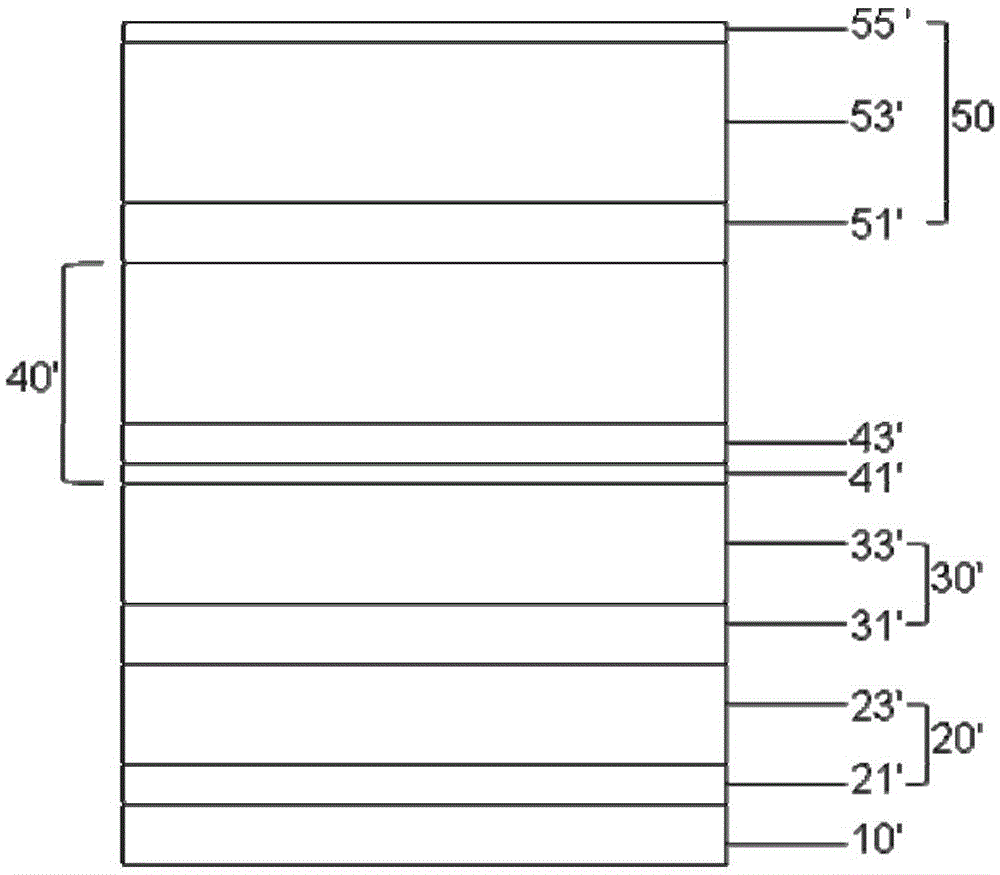

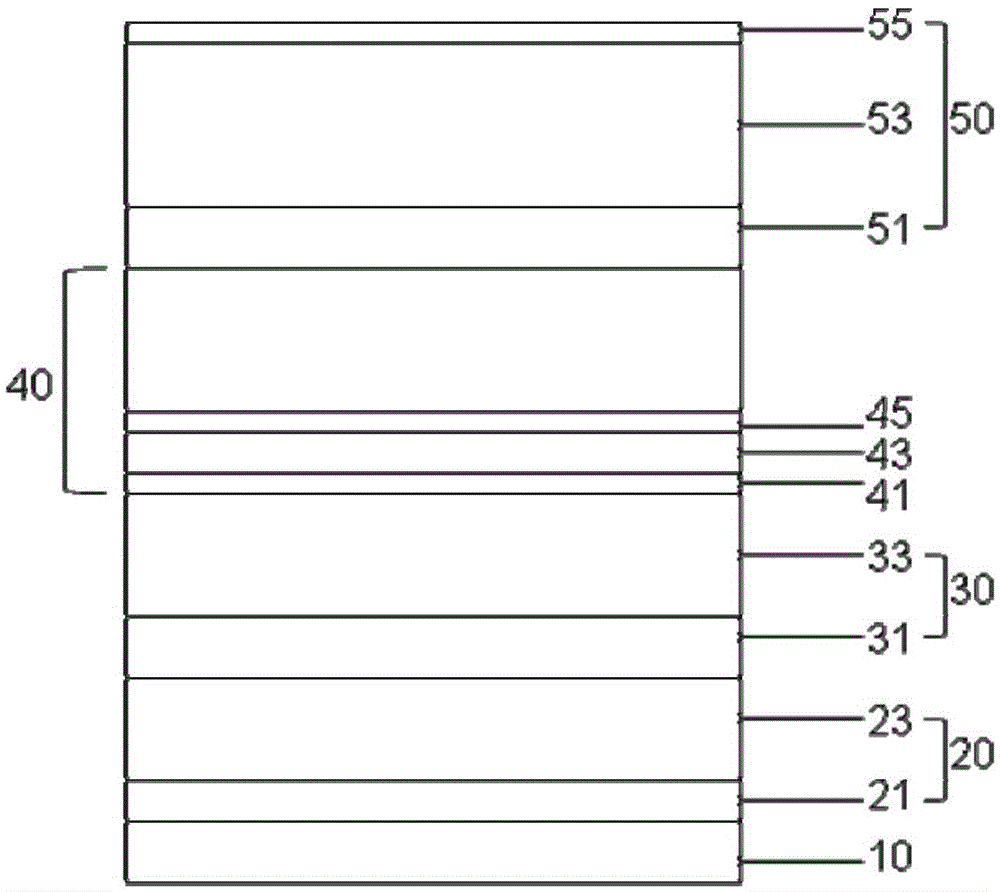

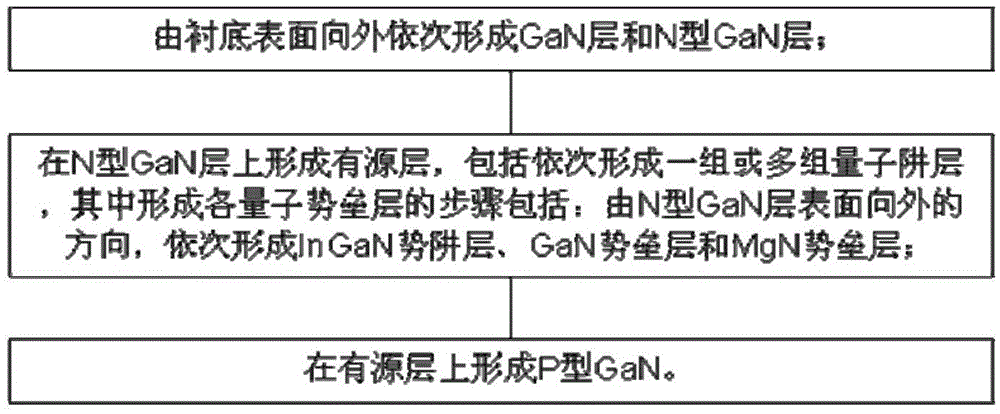

Light-emitting diode (LED) epitaxial wafer, manufacturing method of LED epitaxial wafer and LED chip including LED epitaxial wafer

ActiveCN103474538AImprove interface stateIncrease roughnessSemiconductor devicesPotential wellQuantum efficiency

The invention discloses a light-emitting diode (LED) epitaxial wafer, a manufacturing method of the LED epitaxial wafer and an LED chip including the LED epitaxial wafer. The LED epitaxial wafer comprises an undoped GaN layer, an N-type GaN layer, an active layer and a P-type GaN layer which are sequentially arranged from the substrate surface to the outside. The active layer comprises one or more groups of quantum well layers, wherein each quantum well layer comprises an InGaN potential well layer, a GaN potential barrier layer and an MgN potential barrier layer which are sequentially arranged in the direction away from a substrate. The manufacturing method of the LED epitaxial wafer comprises the steps of sequentially forming the undoped GaN layer, the N-type GaN layer, the active layer and the P-type GaN layer from the substrate surface to the outside, wherein the active layer forming step is that one or more groups of quantum well layers are sequentially formed, and the quantum well layer forming step is that the InGaN potential well layer, the GaN potential barrier layer and the MgN potential barrier layer are sequentially formed from the surface of the N-type GaN layer to the outside. By the adoption of the manufacturing method of the LED epitaxial wafer, the LED luminance and the internal quantum efficiency are improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

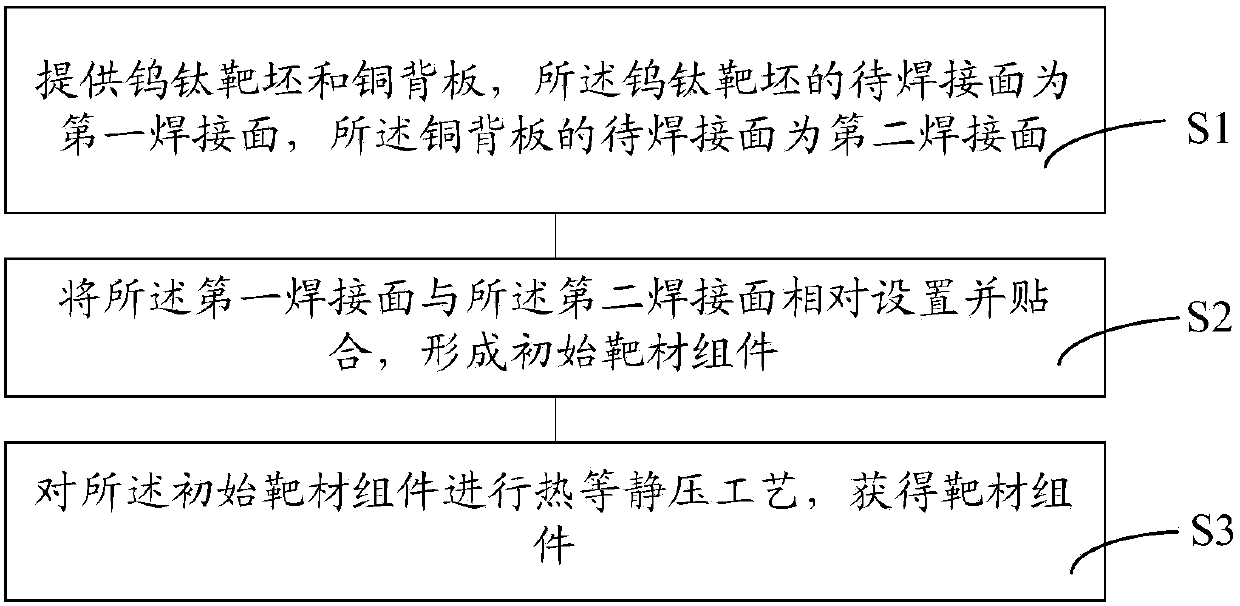

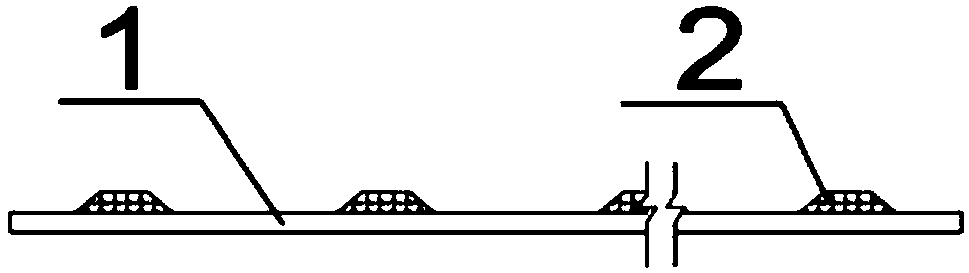

Manufacturing method of target module

InactiveCN107663631AAvoid desolderingRealize large area weldingVacuum evaporation coatingSputtering coatingTitaniumCopper

The invention provides a manufacturing method of a target module. The manufacturing method of the target module comprises the following steps: a tungsten titanium target blank and a copper back plateare provided, wherein a surface to be welded of the tungsten titanium target blank is a first welded surface, and a surface to be welded of the copper back plate is a second welded surface; the firstwelded surface and the second welded surface are oppositely arranged and bonded to form an initial target module; and a hot isostatic pressing process is performed on the initial target module to obtain the target module. As the hot isostatic pressing process is performed on the initial target module, large-area welding of the tungsten titanium target blank and the copper back plate can be realized, the bonding strength of the tungsten titanium target blank and the copper back plate can be improved, the formed target module can reach the welding bonding rate of above 99% and the welding strength of above 50 MPa, and desoldering of the target module in the use process can be prevented.

Owner:KONFOONG MATERIALS INTERNATIONAL CO LTD

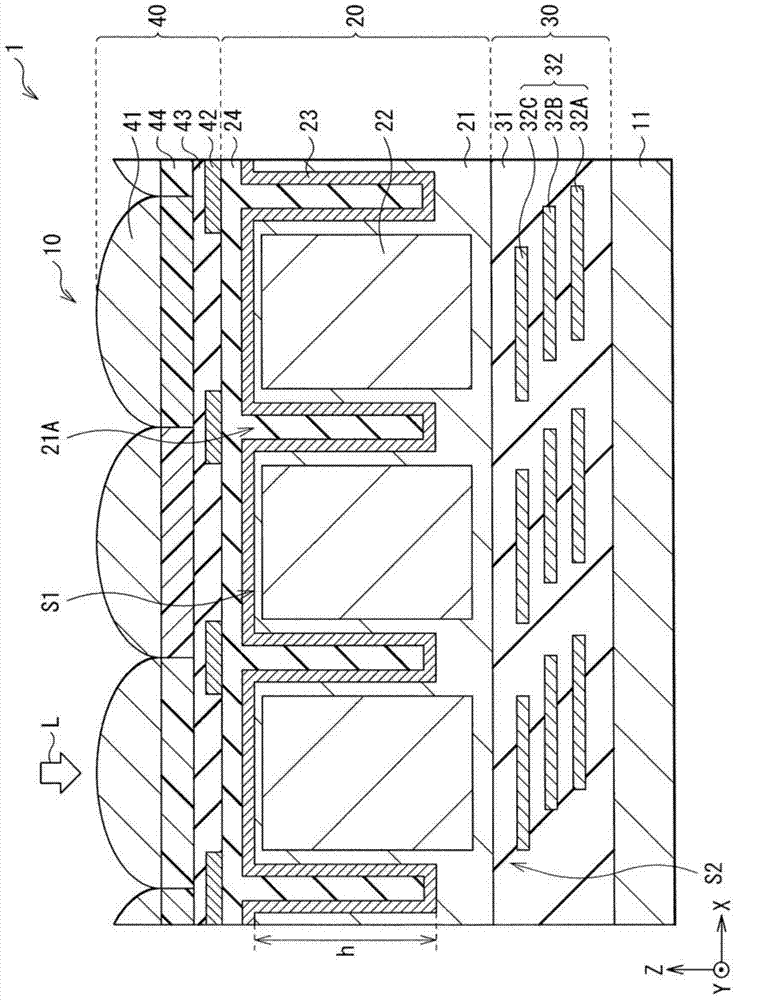

Image pickup element, method of manufacturing image pickup element, and electronic apparatus

ActiveCN104517981AImprove interface stateSuppress dark currentSolid-state devicesDiodeFixed chargeEngineering

An image pickup element includes: a semiconductor substrate including a photoelectric conversion section for each pixel; a pixel separation groove provided in the semiconductor substrate; and a fixed charge film provided on a light-receiving surface side of the semiconductor substrate, wherein the fixed charge film includes a first insulating film and a second insulating film, the first insulating film being provided contiguously from the light-receiving surface to a wall surface and a bottom surface of the pixel separation groove, and the second insulating film being provided on a part of the first insulating film, the part corresponding to at least the light-receiving surface.

Owner:SONY CORP

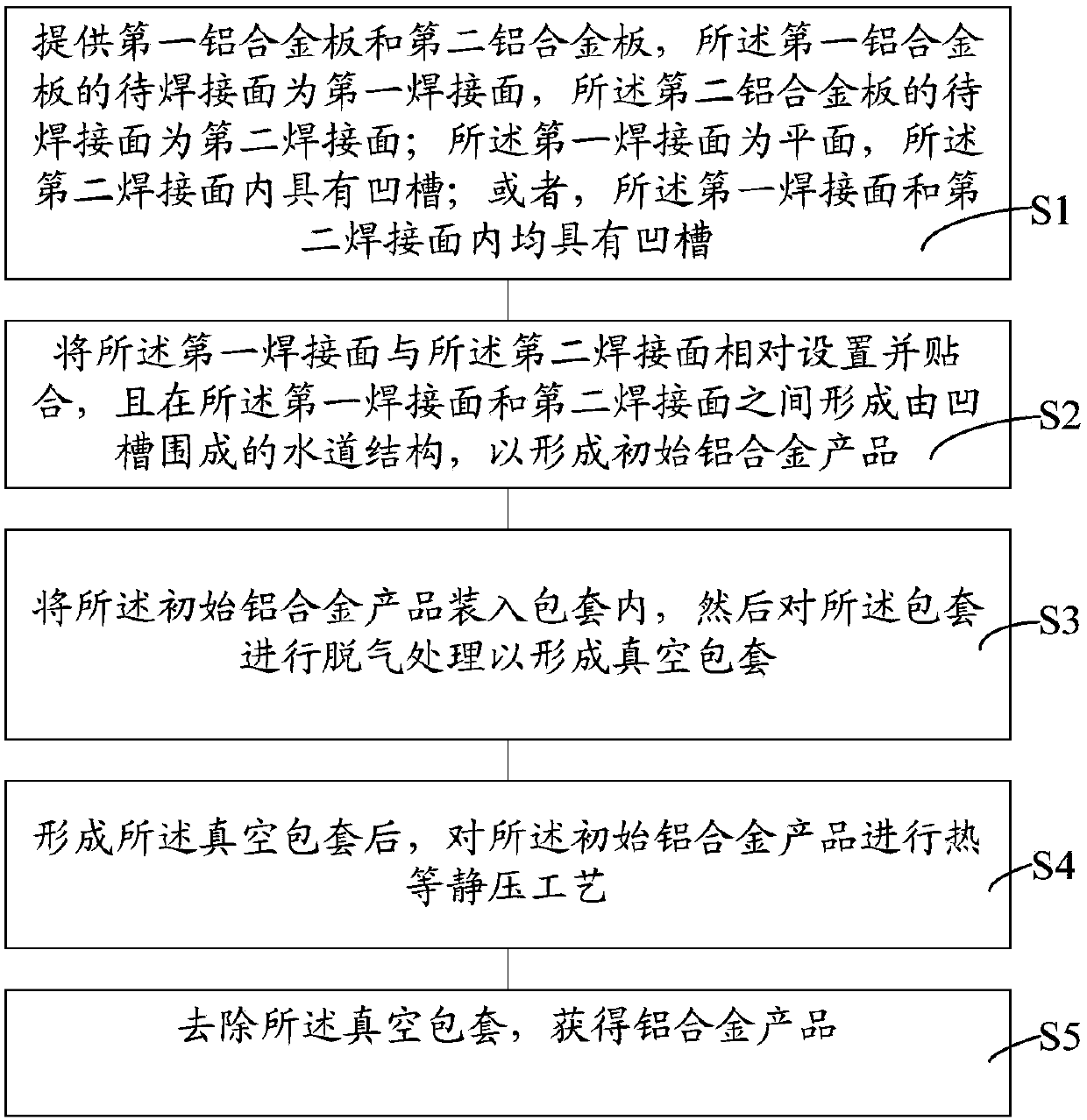

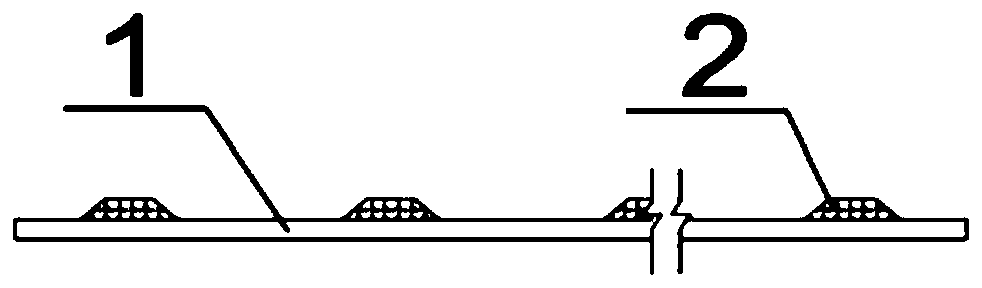

Manufacturing method of aluminum alloy product

InactiveCN107662045AImprove welding strengthAvoid deformation or even blockageNon-electric welding apparatusHot isostatic pressingWeld strength

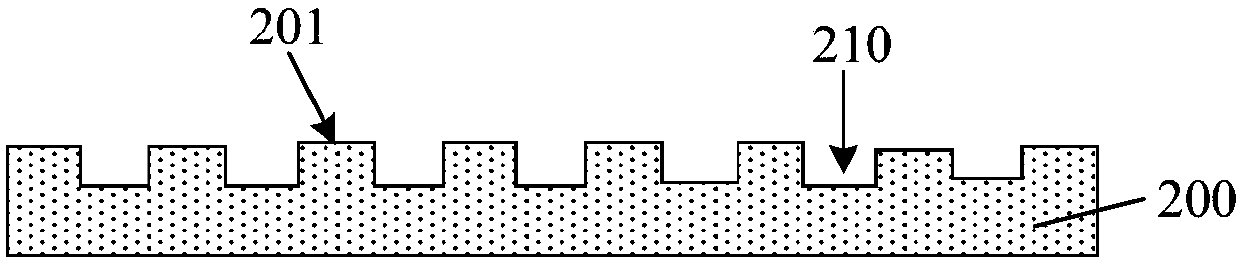

The invention provides a manufacturing method of an aluminum alloy product. The manufacturing method of the aluminum alloy product comprises the following steps: a first aluminum alloy plate and a second aluminum alloy plate are provided, wherein a surface to be welded of the first aluminum alloy plate is a first welded surface, and a surface to be welded of the second aluminum alloy plate is a second welded surface; the first welded surface is a plane, and a groove is formed in the second welded surface; or grooves are formed in the first welded surface and the second welded surface; the first welded surface and the second welded surface are oppositely arranged and bonded, and a water way structure, surrounded by the grooves, is formed between the first welded surface and the second welded surface to form an initial aluminum alloy product; the initial aluminum alloy product is filled in a cover; the cover is degassed to form a vacuum cover; then, a hot isostatic pressing process is performed on the initial aluminum alloy product; and the vacuum cover is removed to obtain the aluminum alloy product. As the hot isostatic pressing process is applied on the initial aluminum alloy product, the welding strength of the formed aluminum alloy product is improved, and meanwhile, deformation or even blockage of the water way structure is prevented.

Owner:KONFOONG MATERIALS INTERNATIONAL CO LTD

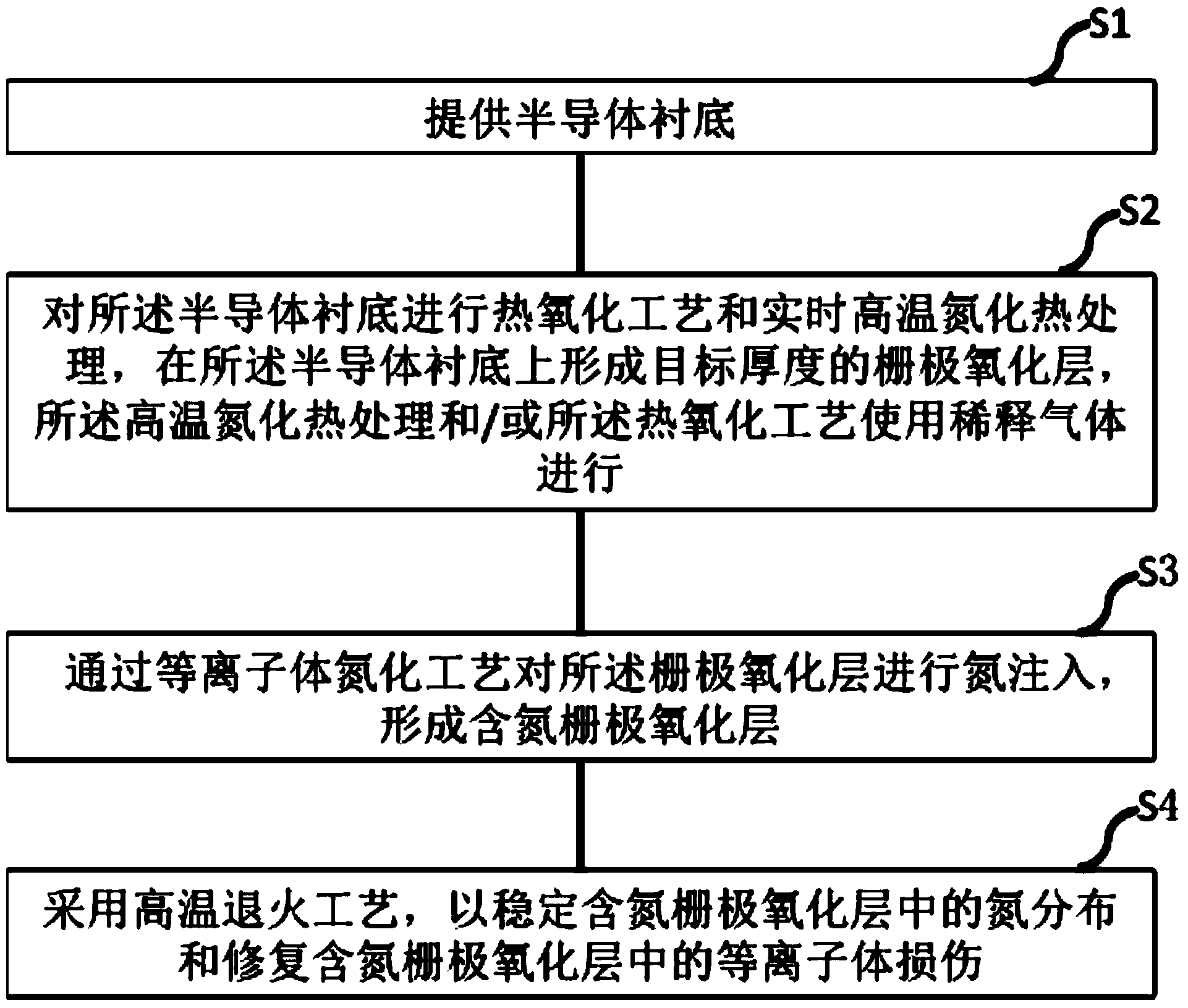

Manufacturing method for nitrogenous grid electrode oxidation layer

InactiveCN103972071AImprove interface stateReduce total chargeSemiconductor/solid-state device manufacturingNitrogenPlasma nitridation

The invention provides a manufacturing method for a nitrogenous grid electrode oxidation layer. The manufacturing method includes the steps that a semiconductor substrate is provided; a thermal oxidation technology and real-time high-temperature nitridation heat treatment are performed on the semiconductor substrate, a grid electrode oxidation layer with a target thickness is formed on the semiconductor substrate, and the high-temperature nitridation heat treatment and / or the thermal oxidation technology is performed through using diluent gas; nitrogen is injected into the grid electrode oxidation layer through a plasma nitridation technology to form the nitrogenous grid electrode oxidation layer; a high-temperature annealing technology is adopted for stabilizing nitrogen distribution in the nitrogenous grid electrode oxidation layer and remedying plasma damage in the nitrogenous grid electrode oxidation layer. The number of Si-H bonds, S-O-H bonds and breakage bonds existing nearby a Si-SiO2 interface is reduced, stress in the grid electrode oxidation layer is reduced, and NBTI performance of a pMOSFET semiconductor device is effectively improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

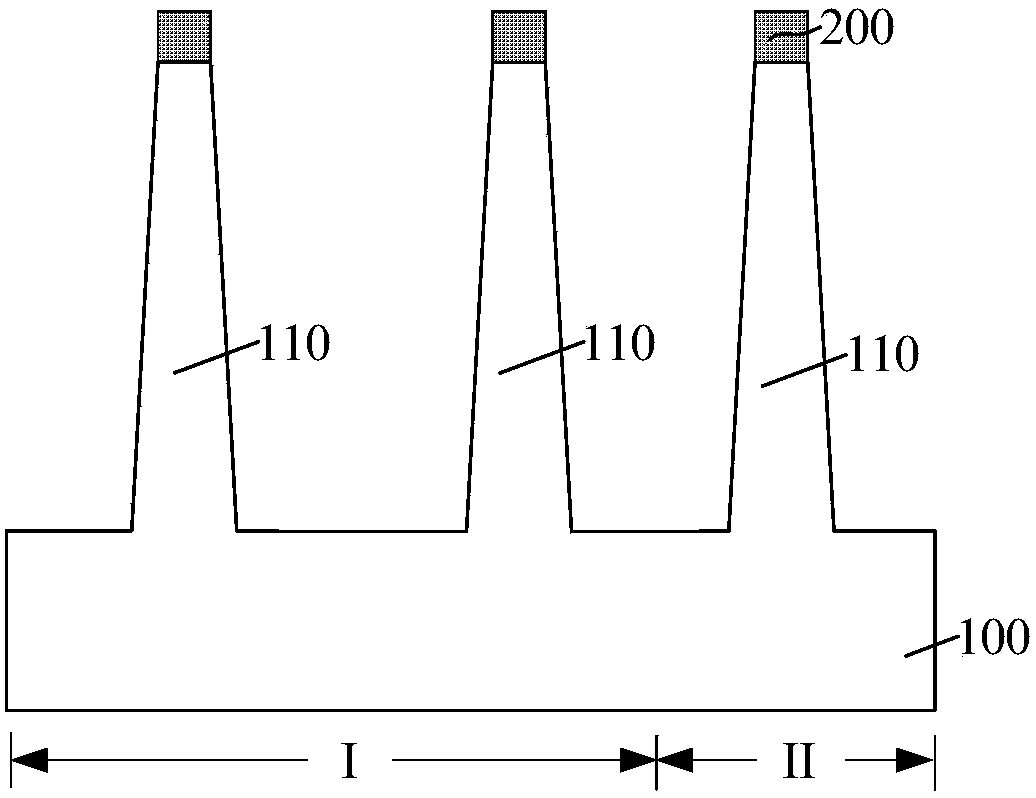

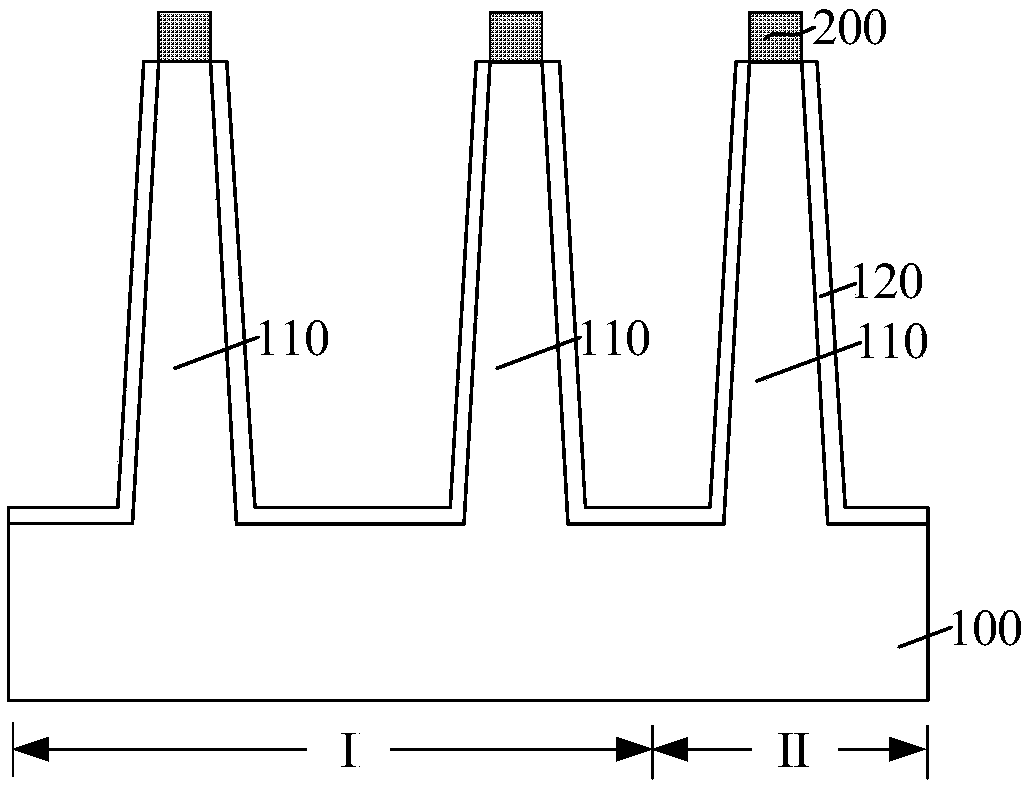

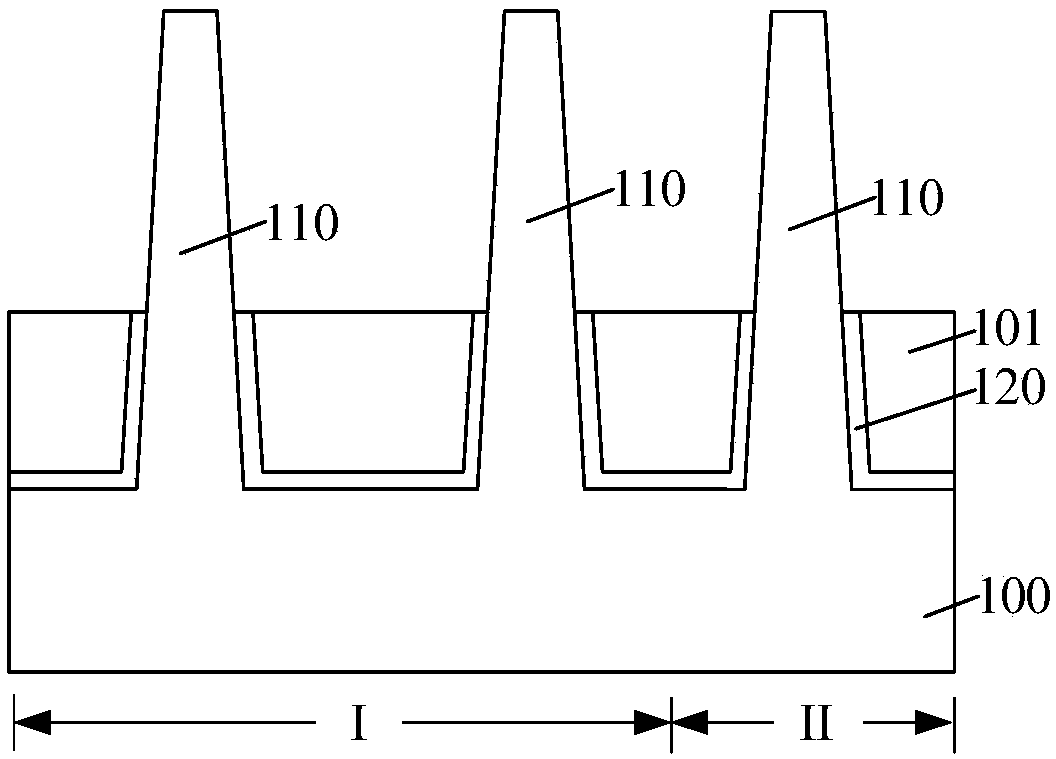

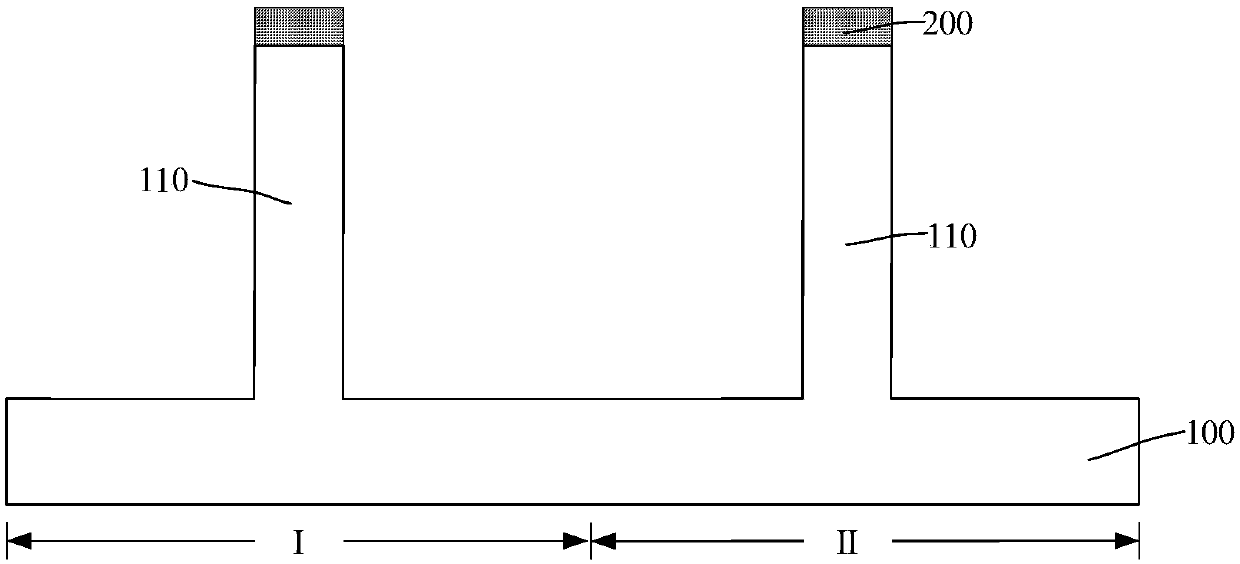

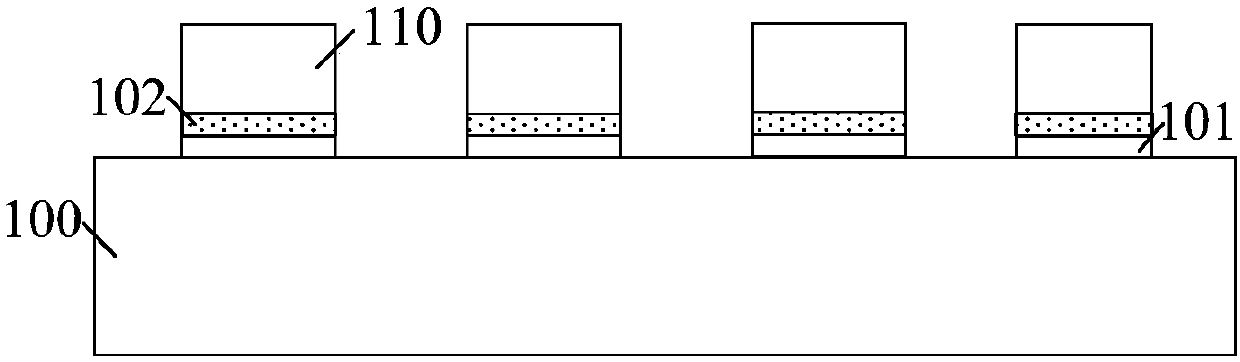

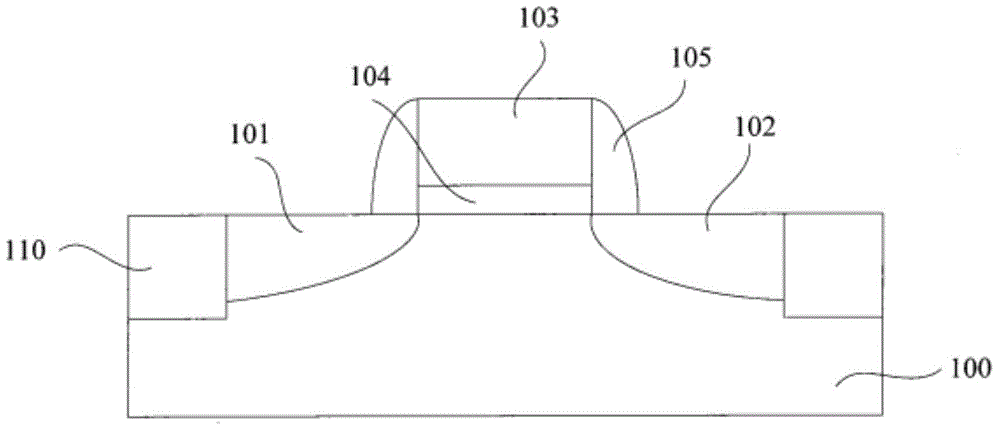

Forming method for fin-type field-effect tube

InactiveCN107919283AReduce dangling keysImprove interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesDangling bondEngineering

The invention discloses a forming method for a fin-type field-effect tube, and the method comprises the steps: providing a substrate which is provided with a plurality of split fin parts, wherein thefin parts are provided with first atoms; forming a pseudo-gate structure which stretches across the fin parts and covers the top surfaces and side wall surfaces of a part of fin parts, and comprises agate oxidation layer and a pseudo-gate electrode layer located on the gate oxidation layer; removing a part of the pseudo-gate electrode layer by certain thickness; carrying out the annealing processing of the tops of the fin parts through the gas comprising second atoms after the part of the pseudo-gate electrode layer is removed, wherein the second atoms can form chemical bonds with the first atoms in the annealing processing. According to the invention, after the part of the pseudo-gate electrode layer is removed, the gas comprising second atoms is employed for the annealing processing ofthe tops of the fin parts. Because the second atoms can form chemical bonds with the first atoms in the annealing processing, the annealing processing is suitable for the reduction of the semiconductor atom dangling bonds in corner regions of the tops of the fin parts (such as a silicon atom dangling bond), improves the interface state between the gate oxidation layer and the fin parts, and solvesa problem of pea discharge caused by the sharp corners of the corner regions.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

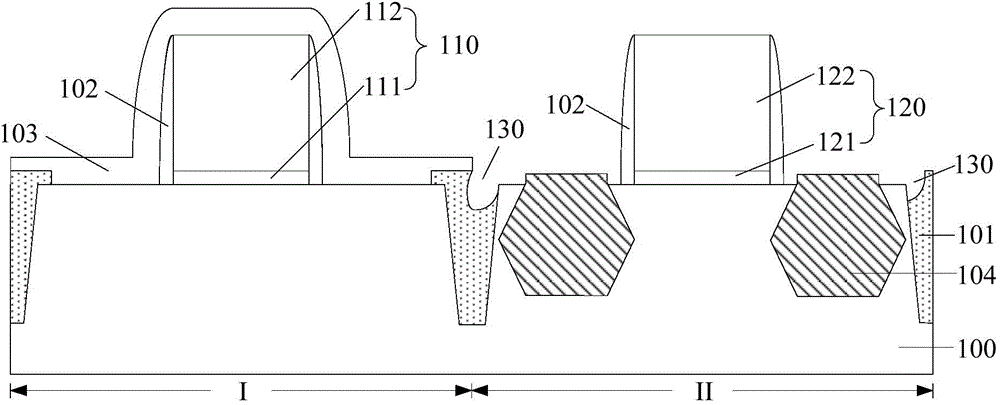

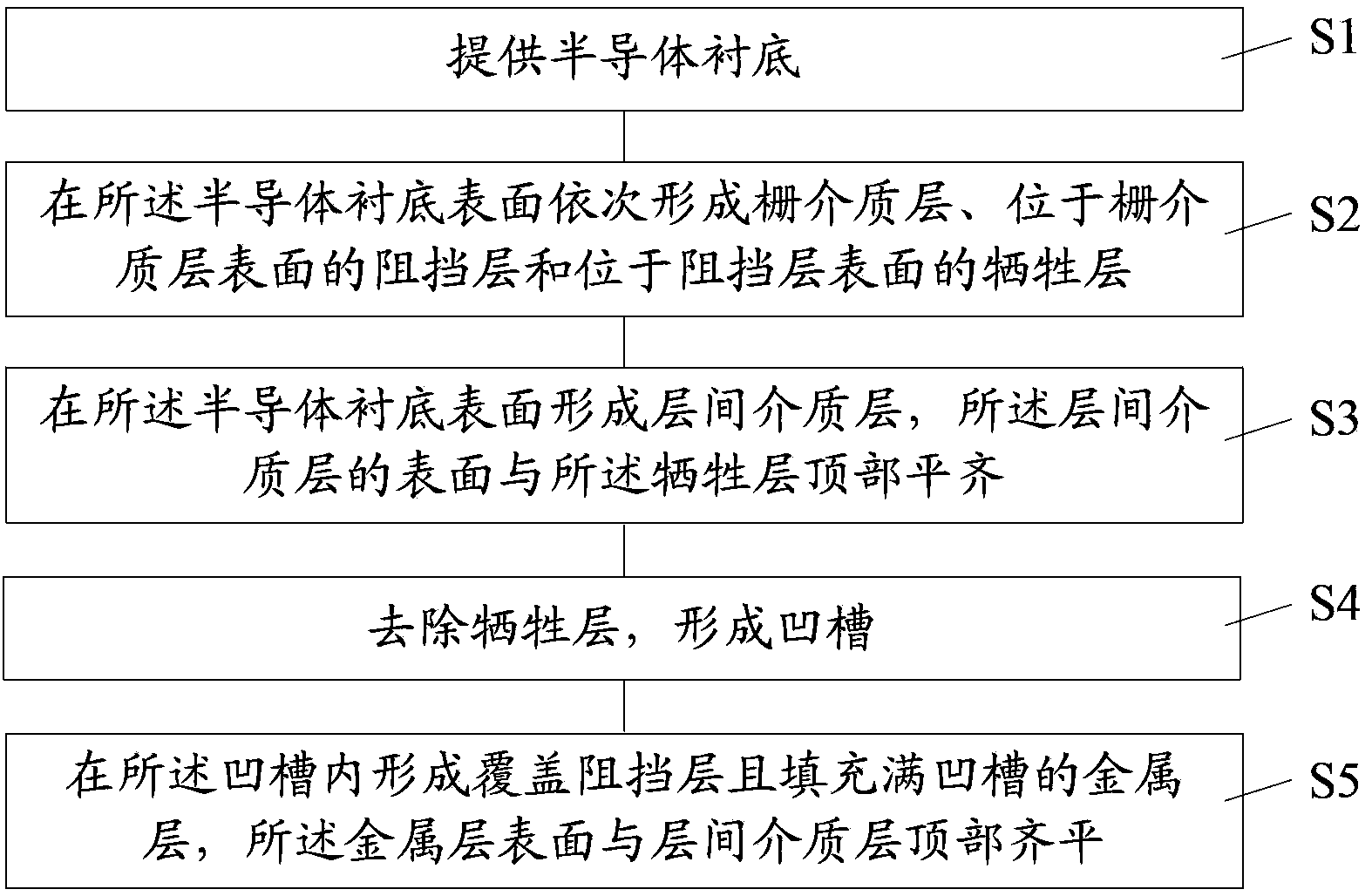

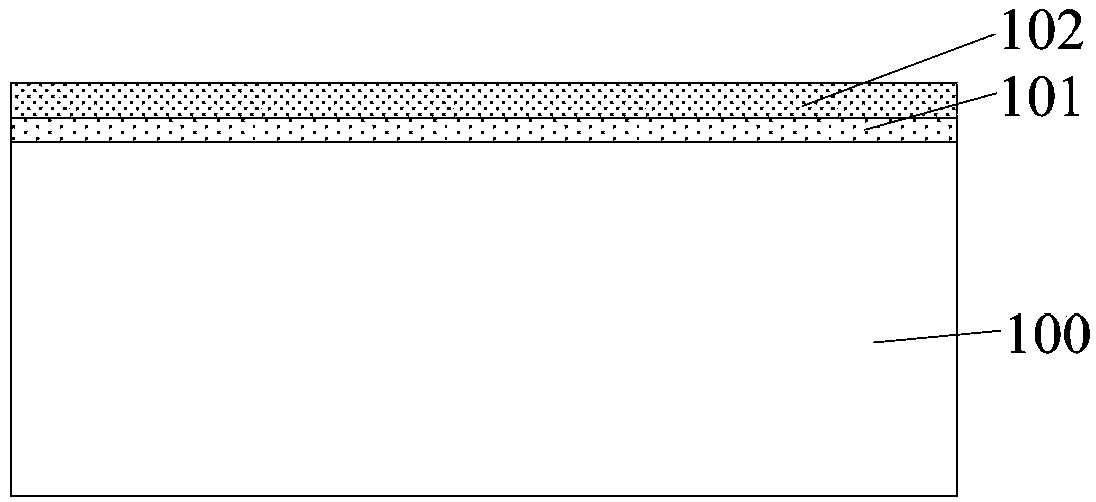

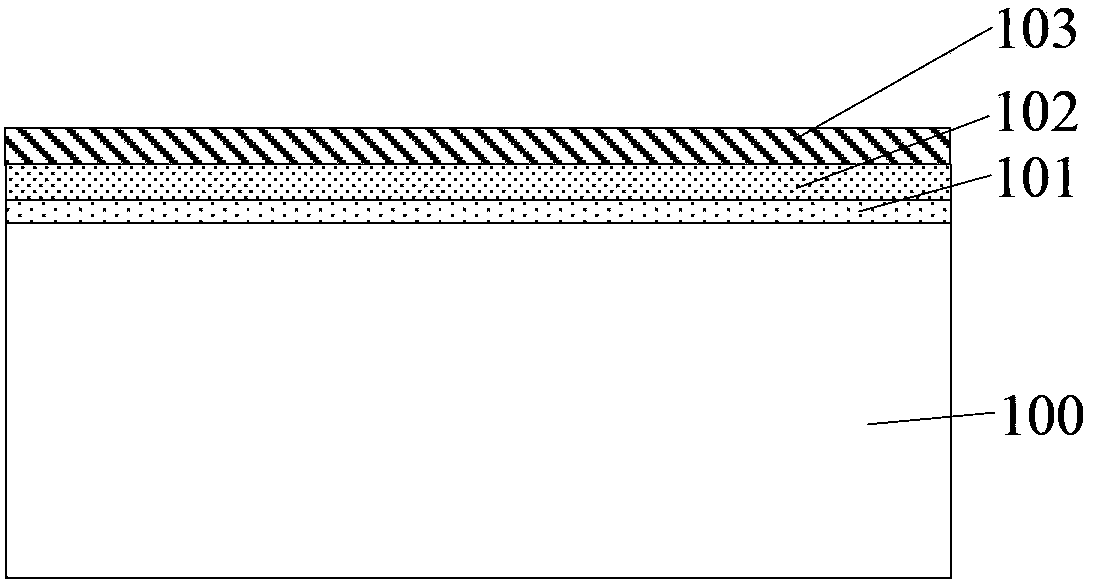

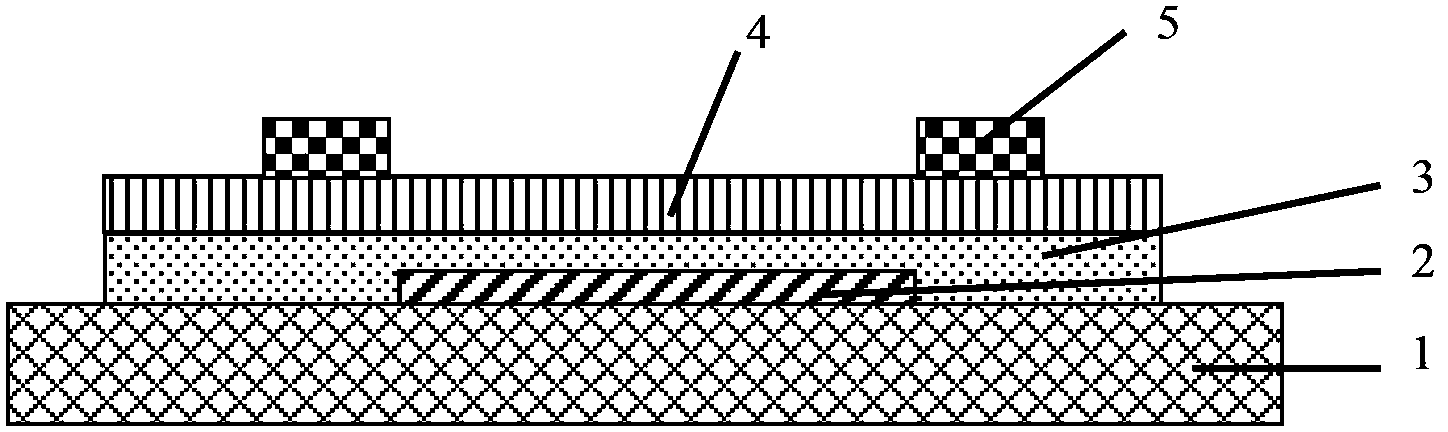

Method for forming semiconductor device

ActiveCN104465486AImprove stabilityIncrease process etch rateSemiconductor/solid-state device manufacturingElectrical performanceSemiconductor

A method for forming a semiconductor device comprises the following steps: providing a semiconductor substrate, wherein the semiconductor substrate is internally provided with isolation structures, and the surface of the semiconductor substrate is provided with gate structures arranged between adjacent isolation structures; stably doping the isolation structures to enhance the corrosion resistance of the isolation structures; forming grooves in the semiconductor substrate at the two sides of each gate structure; cleaning the grooves after doping the isolation structures; and forming a stress layer filling the grooves. The stability of the isolation structures is increased, the anti-etching ability of the isolation structure material is improved, the situation in which the isolation structures are etched by a semiconductor device fabrication process is avoided, the reliability of the isolation structures is improved, the reliability of semiconductor devices is improved, the occurrence of breakdown or leakage is avoided, and the electrical performance of semiconductor devices is optimized.

Owner:SEMICON MFG INT (SHANGHAI) CORP

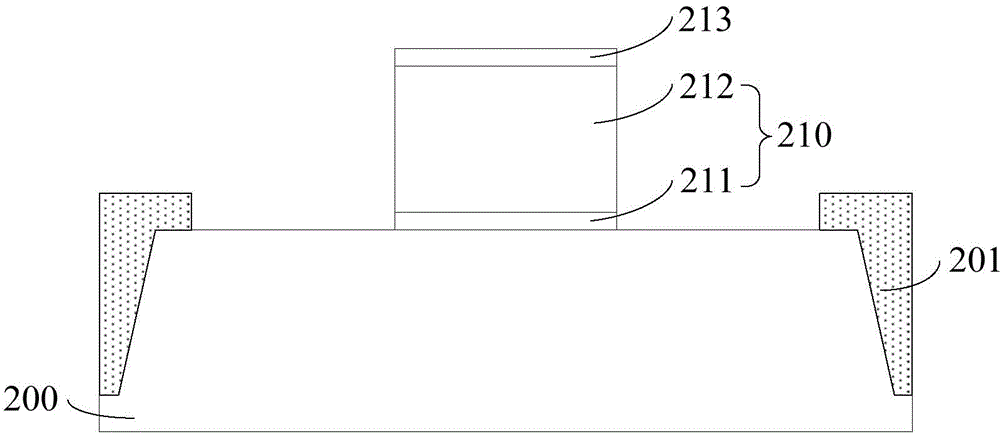

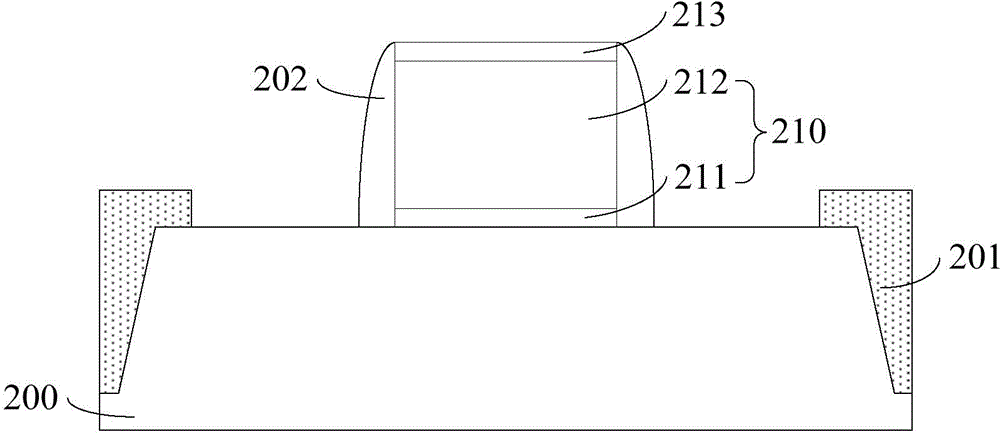

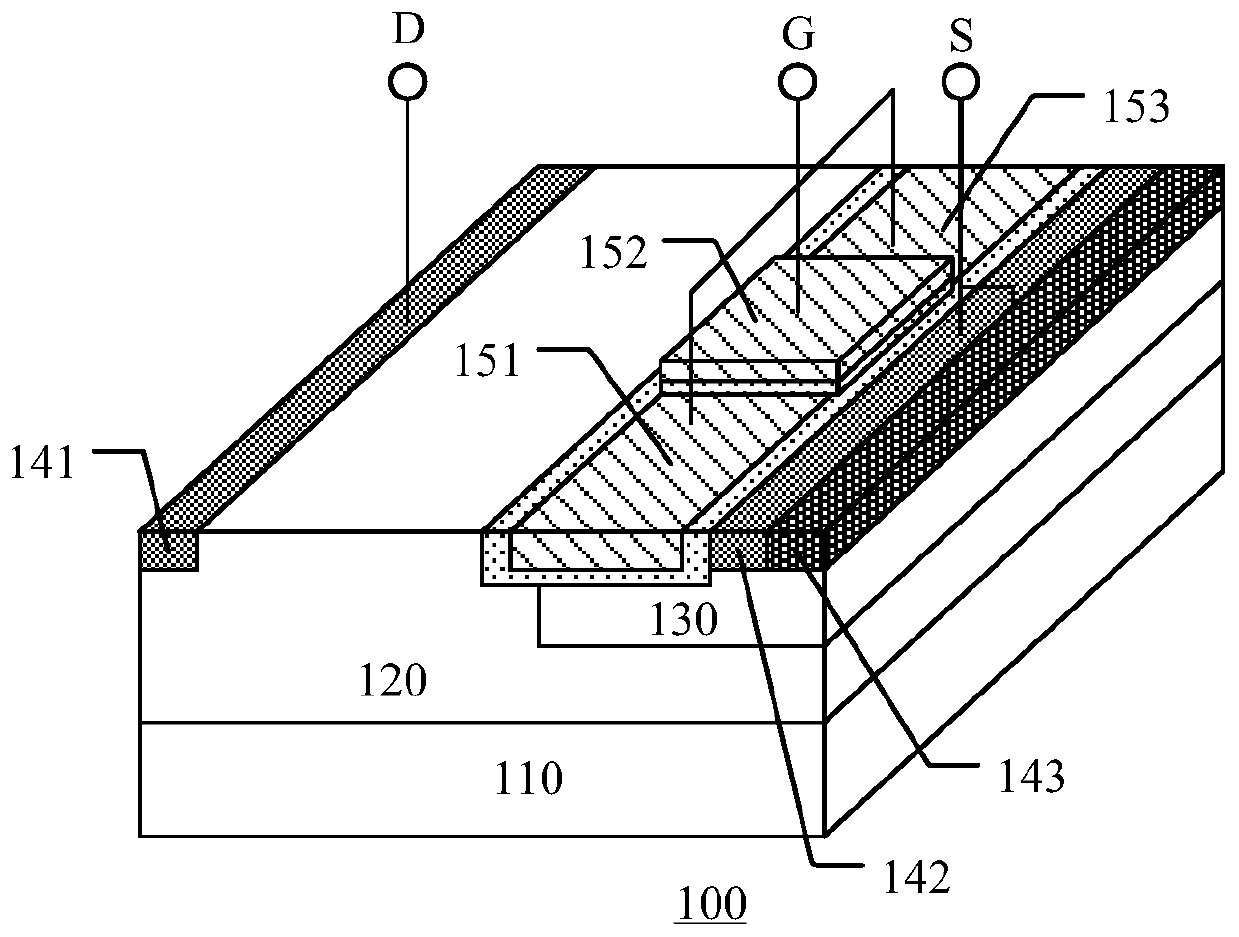

Transistor and formation method thereof

ActiveCN104299994ASimple processImprove electrical performanceTransistorSemiconductor/solid-state device manufacturingPhysicsSemiconductor

Provided is a transistor and a formation method thereof. The formation method of the transistor include: providing a semiconductor substrate; successively forming, on the surface of the semiconductor substrate, a gate dielectric layer, a first barrier layer on the surface of the gate dielectric layer, and a sacrificial layer on the surface of the first barrier layer; forming an interlayer dielectric layer on the surface of the semiconductor substrate, wherein the surface of the interlayer dielectric layer is aligned to the top of the sacrificial layer; removing the sacrificial layer to form a slot; forming a second barrier layer, which covers the first barrier layer, in the slot, wherein the morphology of the second barrier layer and morphology of the first barrier layer on which the sacrificial layer has been removed are in complementation; forming a metal layer fully filling the slot on the surface of the second barrier layer, wherein the surface of the metal layer is aligned to the top of the interlayer dielectric layer. This invention reduces the leakage current of the gate of the transistor and improves the reliability and electrical properties of the transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for preparing thin-film transistor on flexible substrate

InactiveCN103515236AImprove performanceReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsGate dielectric

The invention discloses a method for preparing a thin-film transistor on a flexible substrate. According to the invention, a thin-film transistor is prepared on a flexible plastic substrate. An aluminum-doped zinc oxide semiconductor material is used for forming a transparent conductive semiconductor channel layer. During the preparation process, an appropriate amount of oxygen is added by using the unique technology and thus the aluminum-doped zinc oxide presents a semiconductor characteristic and exhibits a high migration characteristic, thereby effectively improving the performance of the thin-film transistor. Meanwhile, the zinc oxide aluminum film is an environment-friendly material and the process is simple, so that the application prospect is wide. Moreover, the preparation method of simultaneous preparation of an insulated gate dielectric layer and a semiconductor channel layer is employed, thereby simplifying the preparation process. And an interface state of films on the flexible substrate can be effectively improved; the device performance is improved; the manufacturing cost is lowered; and the large-scale production can be realized.

Owner:BOE TECH GRP CO LTD

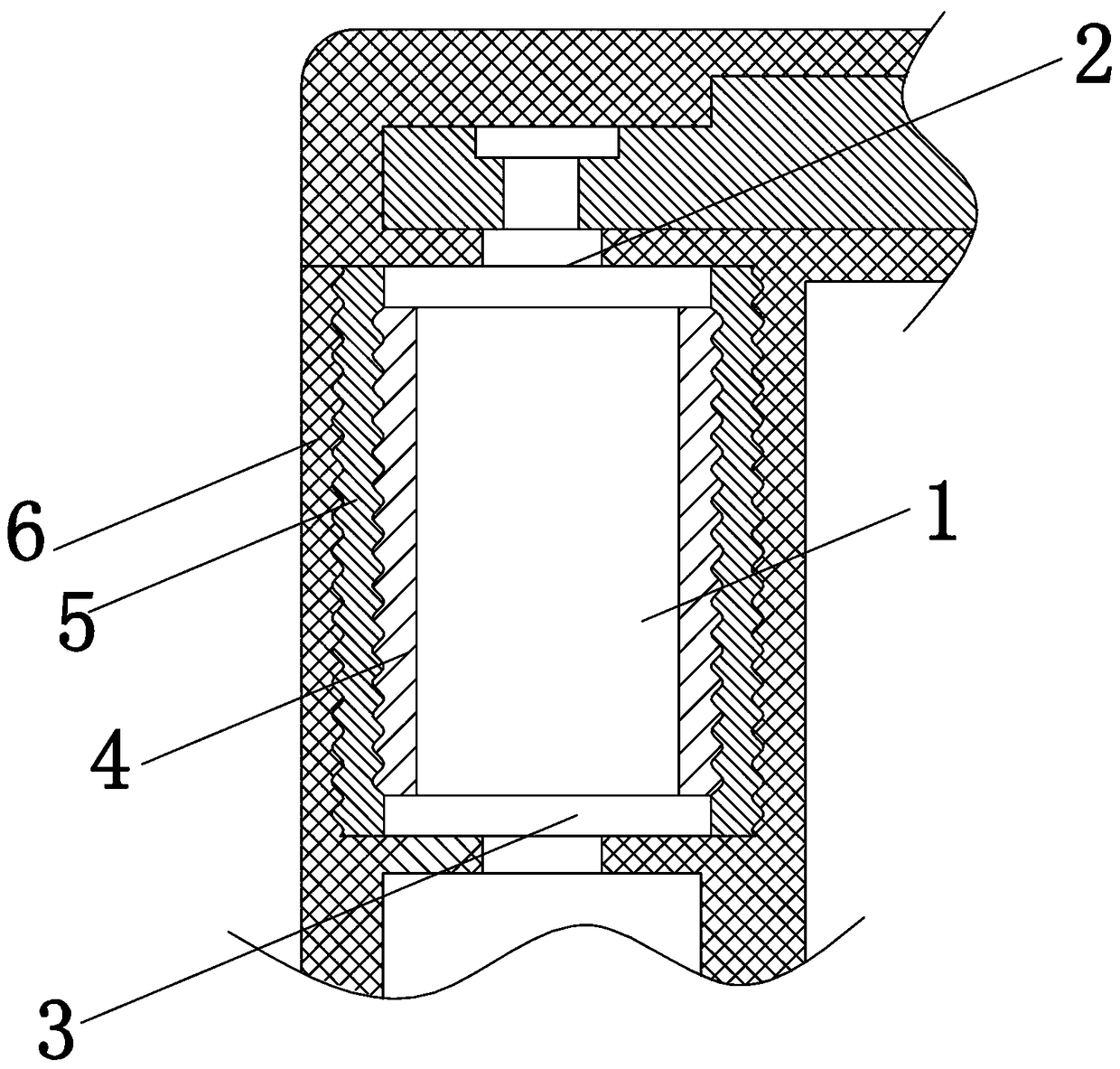

Composite insulated solid-sealed pole and production method thereof

InactiveCN108648954AImprove the level of external insulationImprove interface stateHigh-tension/heavy-dress switchesAir-break switchesEpoxySilicone Gels

The invention discloses a composite insulated solid-sealed pole, comprising a vacuum interrupter. A static end cover plate and a movable end cover plate are arranged at the two ends of the vacuum interrupter, a ceramics insulating layer is arranged on the surface of the vacuum interrupter, the outer side of the ceramic insulating layer is coated with a silica gel layer, and the outer side of the silica gel layer is coated with epoxy resin, wherein the contact interface between the ceramic insulating layer and the silica gel layer is an annular corrugated surface, and the contact interface of the silicone gel layer and the epoxy resin is also an annular corrugated surface. According to the composite insulated solid-sealed pole obtained by the invention, the buffering effect of the silica gel layer of the vacuum interrupter is improved, no air bubble is caused, and the external insulation level of the vacuum interrupter can be obviously improved, The distance between the static end coverplate and the movable end cover plate of the vacuum interrupter is increased by about 30% through the arrangement of the annular corrugated surfaces, the interface state of the two materials is changed, the surface dielectric structure is changed, and the linear breakdown is avoided.

Owner:慈溪益成电器有限公司

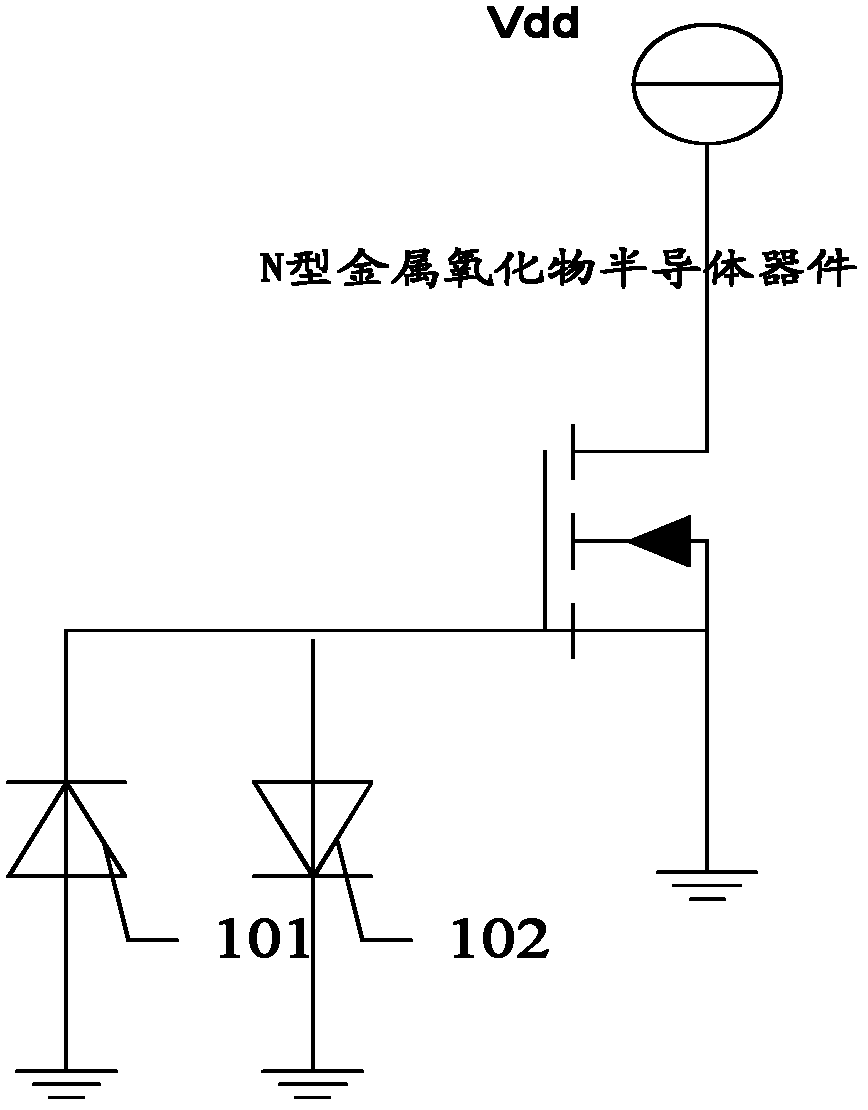

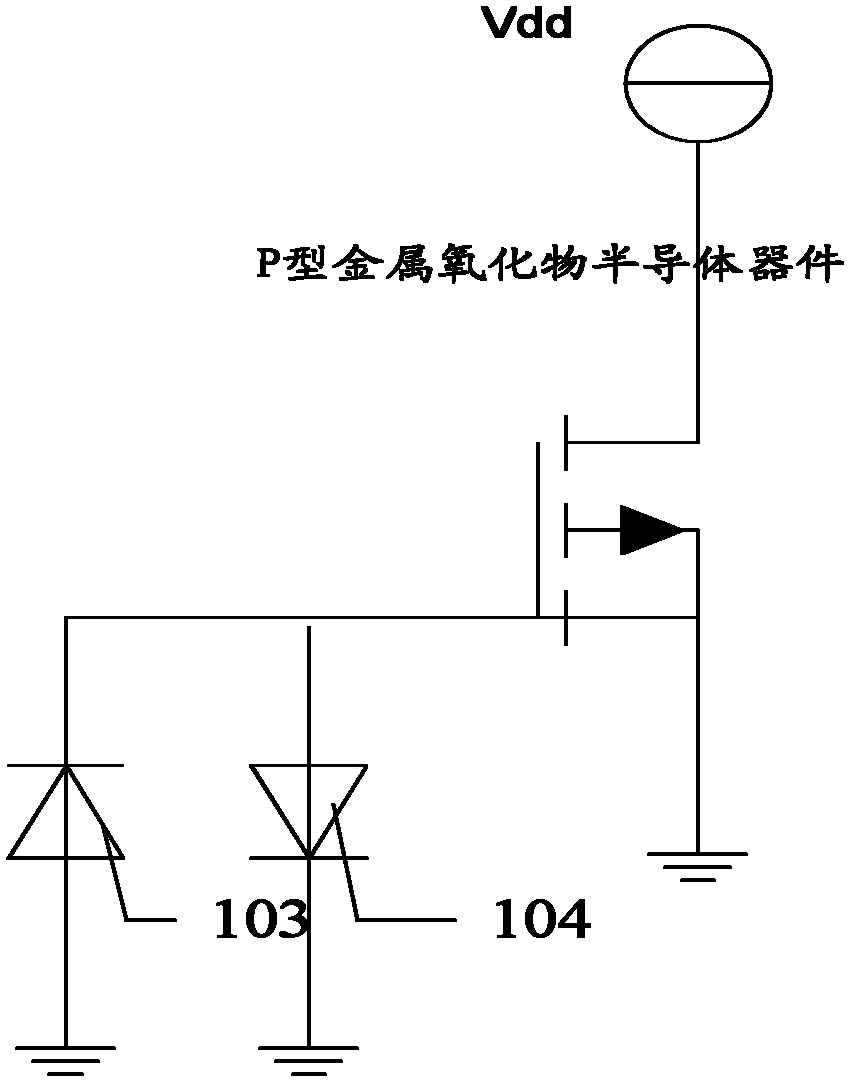

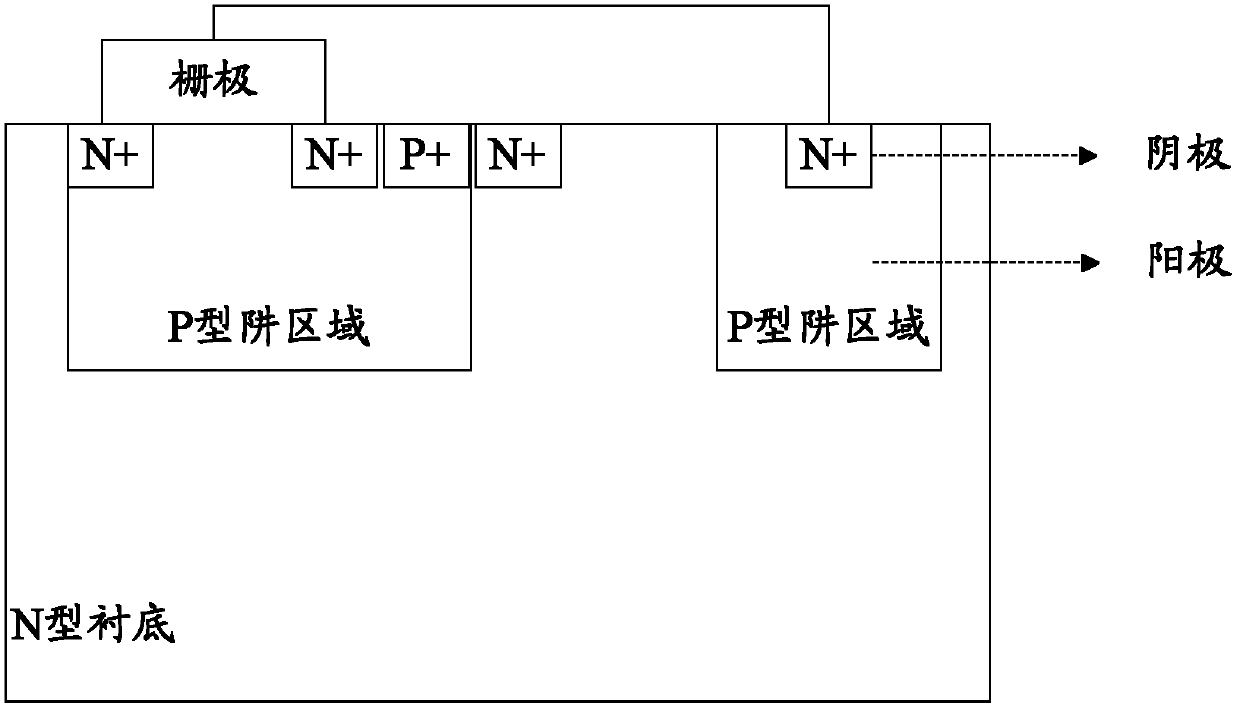

Metal oxide semiconductor electrical parameter testing device and method of manufacture

ActiveCN103378095AFacilitated releaseImprove interface stateSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorOxide

The invention discloses a metal oxide semiconductor electrical parameter testing device and a method of manufacture. A gate is a metal gate. A first P-type well region of an N-type substrate and a first N+ region form a first PN junction to constitute a first diode. A second P-type well region of the N-type substrate and a second N+ region form a second PN junction to constitute a second diode. The first diode is in anti-parallel connection with the second diode and is connected with the gate to form an N-type metal oxide semiconductor electrical parameter testing device. Or, the N-type substrate and the first P+ region form a third PN junction to constitute a third diode; the N-type substrate and the second P+ region form a fourth PN junction to constitute a fourth diode; and the third diode is in anti-parallel connection with the fourth diode and is connected with the gate to form a P-type metal oxide semiconductor electrical parameter testing device. According to the invention, positive charge or negative charge introduced due to plasma damage can be well discharged so as to enable small variation in threshold voltage.

Owner:FOUNDER MICROELECTRONICS INT

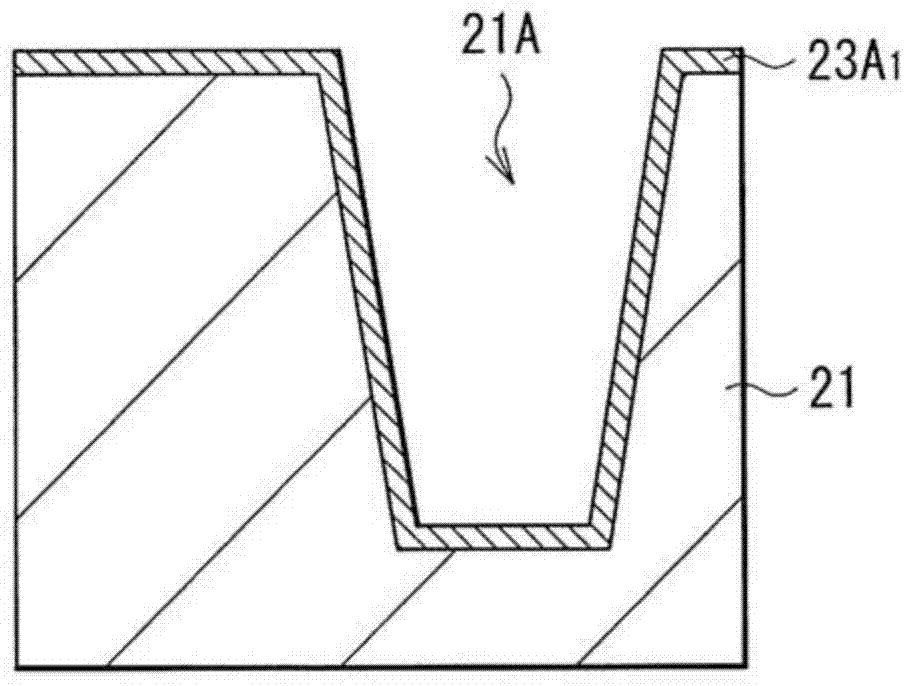

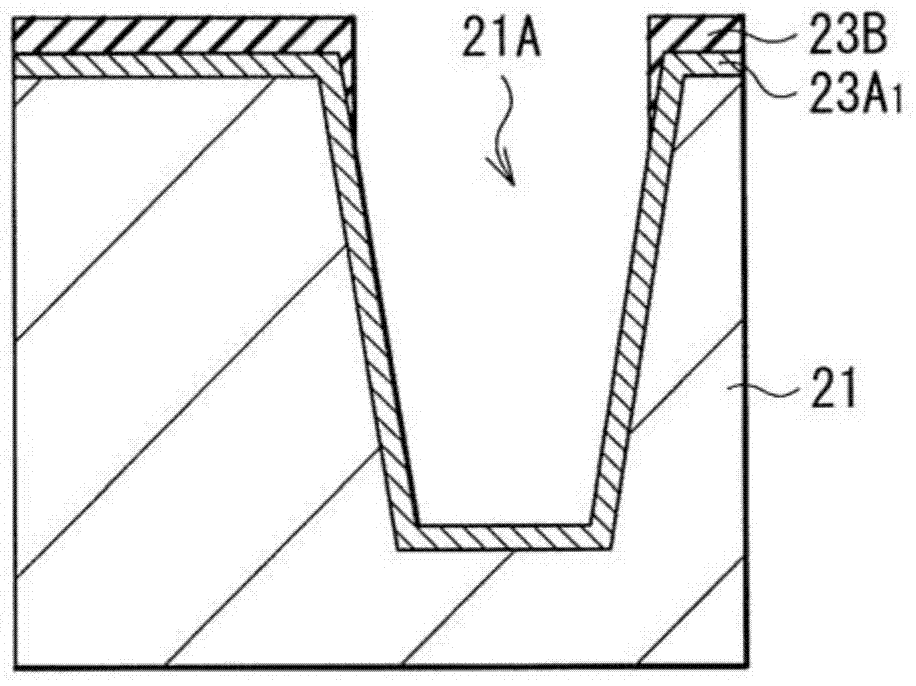

Fin-type field-effect tube and forming method therefor

ActiveCN107919326AImprove integrityReduce dislocationTransistorSolid-state devicesEtchingIn situ doping

The invention discloses a fin-type field-effect tube and a forming method therefor. The method comprises the steps: providing a substrate with a plurality of split fin parts, wherein the substrate comprises an NMOS region; forming a pseudo-gate structure which stretches across the fin parts and covers the top surfaces and side wall surfaces of a part of fin parts, and comprises a gate oxidation layer and a pseudo-gate electrode layer located on the gate oxidation layer; carrying out the etching of a part of fin parts at two sides of the pseudo-gate structure in the NMOS region by certain thickness, forming NMOS region grooves in the fin parts of the NMOS region, wherein the profile of each NMOS region groove in a direction perpendicular to the extending direction of the fin parts is shapedlike U; and forming an in-situ doped epitaxial layer with N-type doped atoms in the NMOS region grooves. According to the invention, the NMOS region grooves are formed in the fin parts at two sides of the pseudo-gate structure in the NMOS region, and the profile of each NMOS region groove in the direction perpendicular to the extending direction of the fin parts is shaped like U. The surfaces ofthe fin parts exposed by the NMOS region grooves are in <100> crystal orientation, and the in-situ doped epitaxial layer grows in the <100> crystal orientation, so the dislocation of the in-situ dopedepitaxial layer is smaller.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and formation method thereof

ActiveCN110391285AReduce lossImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

The invention discloses a semiconductor structure and a formation method thereof. The method includes providing a substrate, wherein the substrate includes a first area; forming a gate dielectric layer on the first area of the substrate; forming a protective layer on the gate dielectric layer of the first area, wherein the material of the protective layer is a non-crystalline material, and the protective layer has doped ions; and forming a grid electrode on the protective layer of the first area. The protective layer can be taken as a work function layer of the formed semiconductor structure,so that the protective layer cannot be removed in follow-up process, and therefore, technological process can be simplified; and the protective layer can be protected from damaging the gate dielectriclayer during removing, so that the performance of the formed semiconductor structure can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Interconnection structure and forming method of interconnection structure

ActiveCN104299958AImproved electromigration propertiesImprove performanceSemiconductor/solid-state device detailsSolid-state devicesInterconnectionCopper

The invention discloses an interconnection structure and a forming method of the interconnection structure. The forming method of the interconnection structure comprises the following steps: providing a semiconductor substrate, wherein a dielectric layer is formed on the surface of the semiconductor substrate; forming an opening in the dielectric layer, wherein the bottom of the opening is exposed out of the surface of the semiconductor substrate; forming a metal layer filling the opening in the opening, wherein the surface of the metal layer is flush with the top of the dielectric layer; forming a first cap layer on the surfaces of the metal cap layer and the dielectric layer, wherein the first cap layer is made from SiBC; and forming a second cap layer on the surface of the first cap layer. Through adoption of the forming method, the occurrence probability of a copper accumulation phenomenon in the interconnection structure is lowered; the electromigration service life of the interconnection structure is prolonged; and the reliability of the interconnection structure is enhanced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for preparing a zinc oxide thin film transistor

ActiveCN108962759AImprove stabilityIncrease the on-state currentTransistorSemiconductor/solid-state device manufacturingRadio frequency magnetron sputteringEvaporation

The invention relates to a method for preparing a zinc oxide thin film transistor, and belongs to a method for preparing a thin film transistor. The method includes substrate cleaning, gate deposition, insulating layer deposition, oxygen-rich zinc oxide channel layer deposition, low-oxygen zinc oxide channel layer deposition, and source electrode and drain electrode deposition. The method has theadvantages that through preparation of the double active layer structure and the interdigital source and drain electrodes, the oxygen-rich and low-oxygen layered channel layers are prepared to improvethe stability of the device and the on-state current, the source and drain electrodes of the interdigitated shape are prepared thereon to further greatly increases the on-state current, and the preparation process is simple. The method is commonly used in the market for RF magnetron sputtering and electron beam evaporation, and does not need to replace the production line; the raw material is pure zinc oxide, the cost is low, and environmental protection is achieved. The method has application prospects in the fields of ultraviolet detection and display driving. The pure zinc oxide thin filmtransistor has more potential application in the market.

Owner:JILIN JIANZHU UNIVERSITY

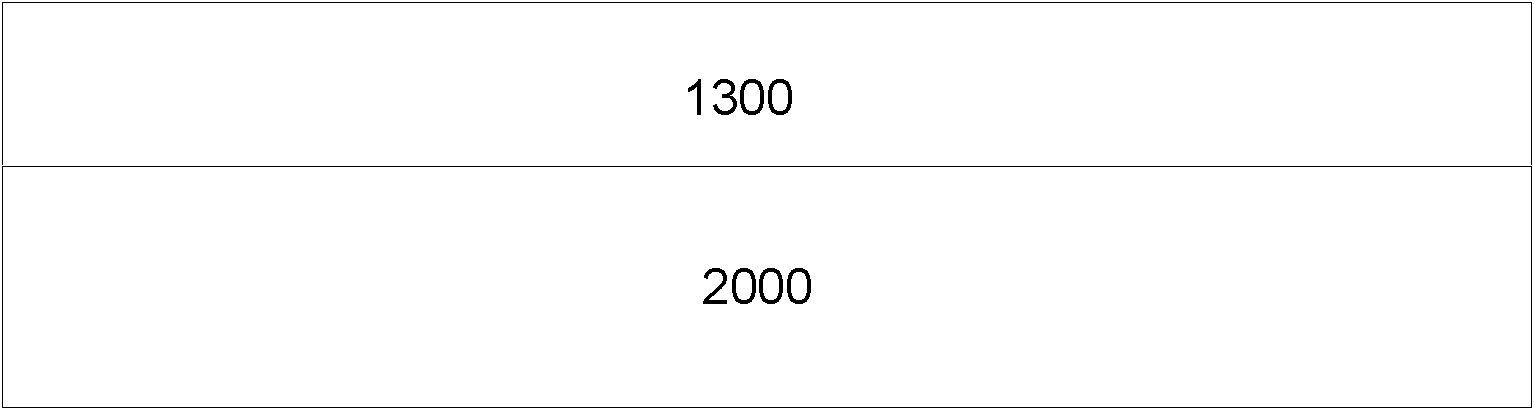

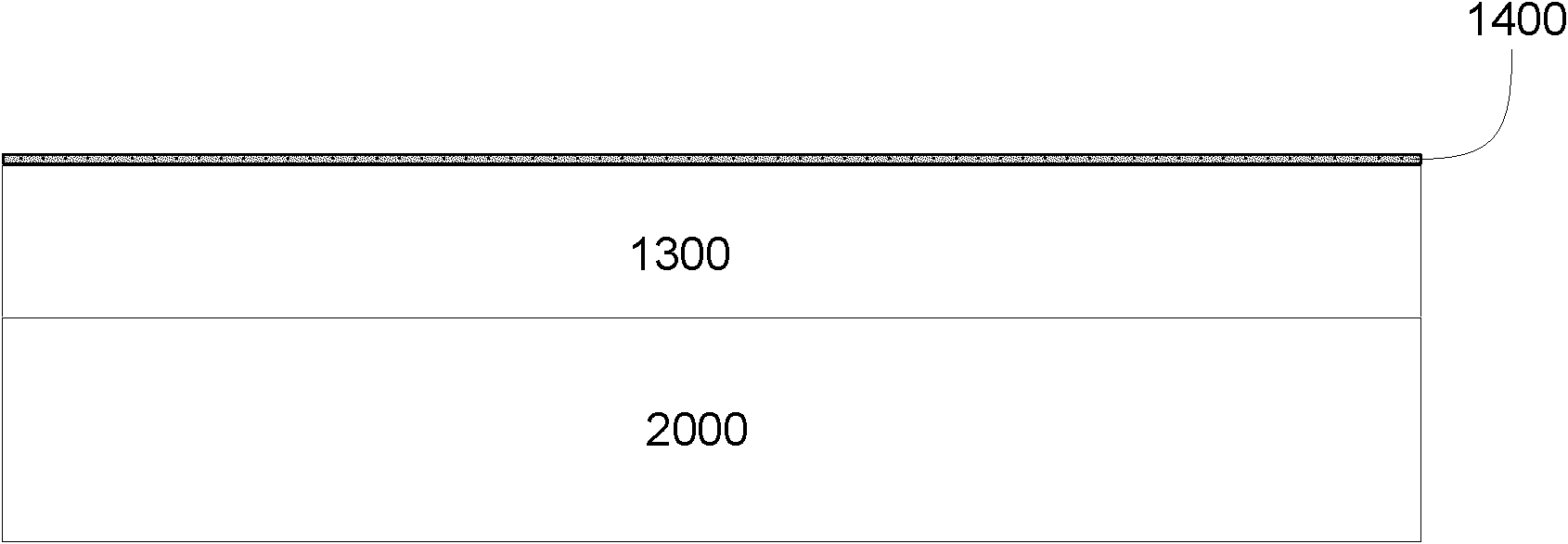

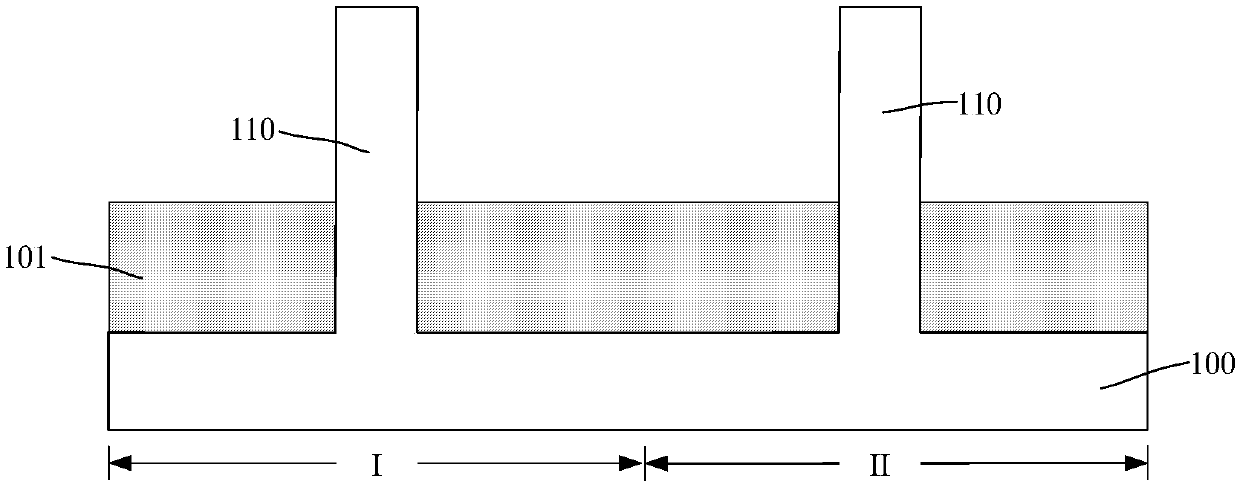

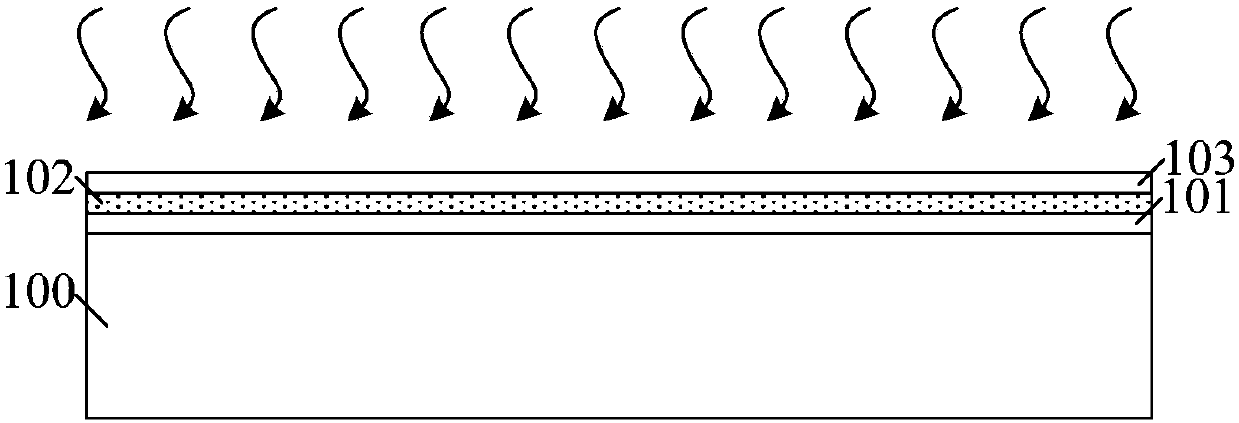

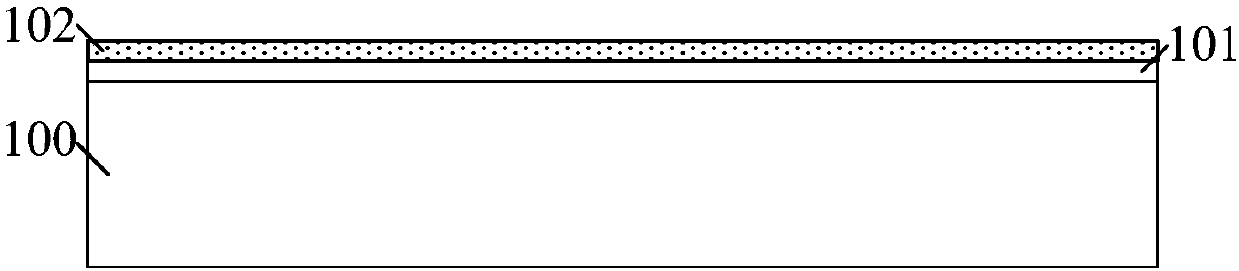

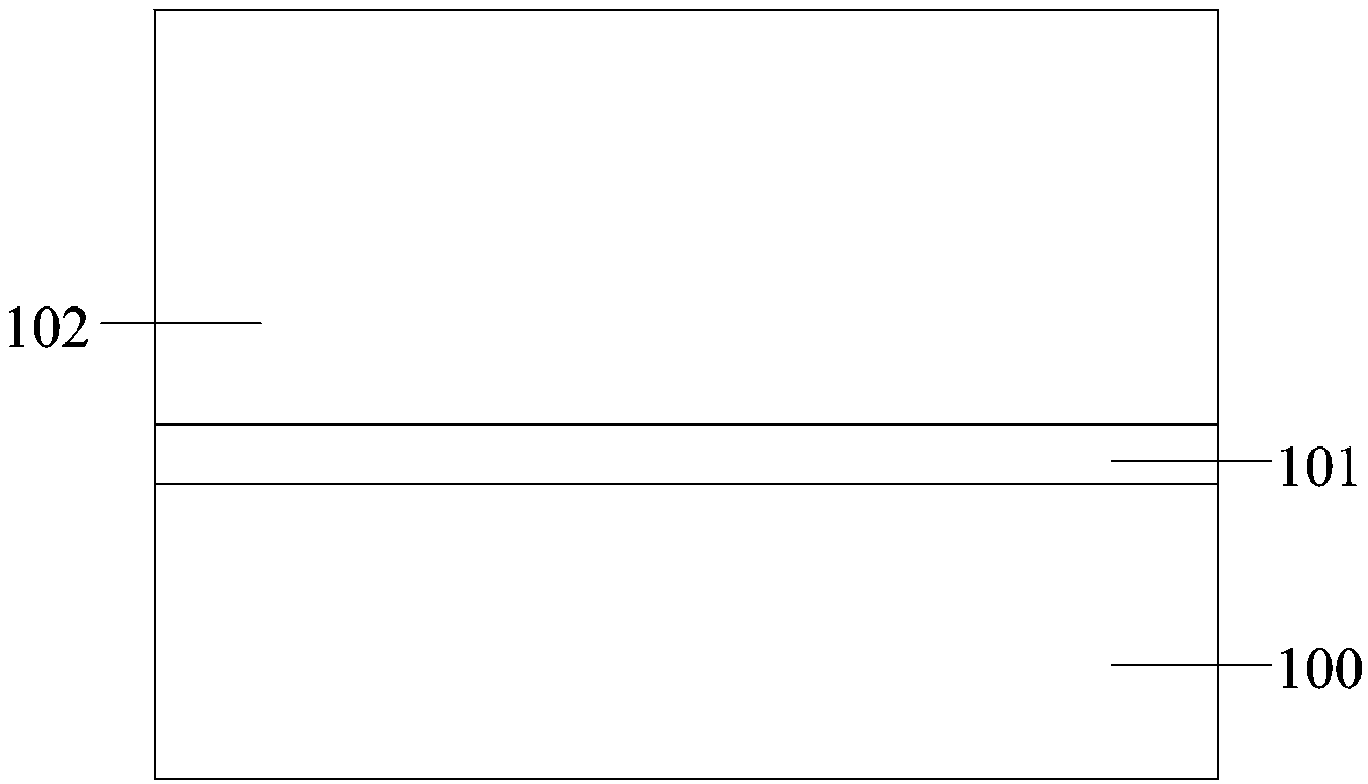

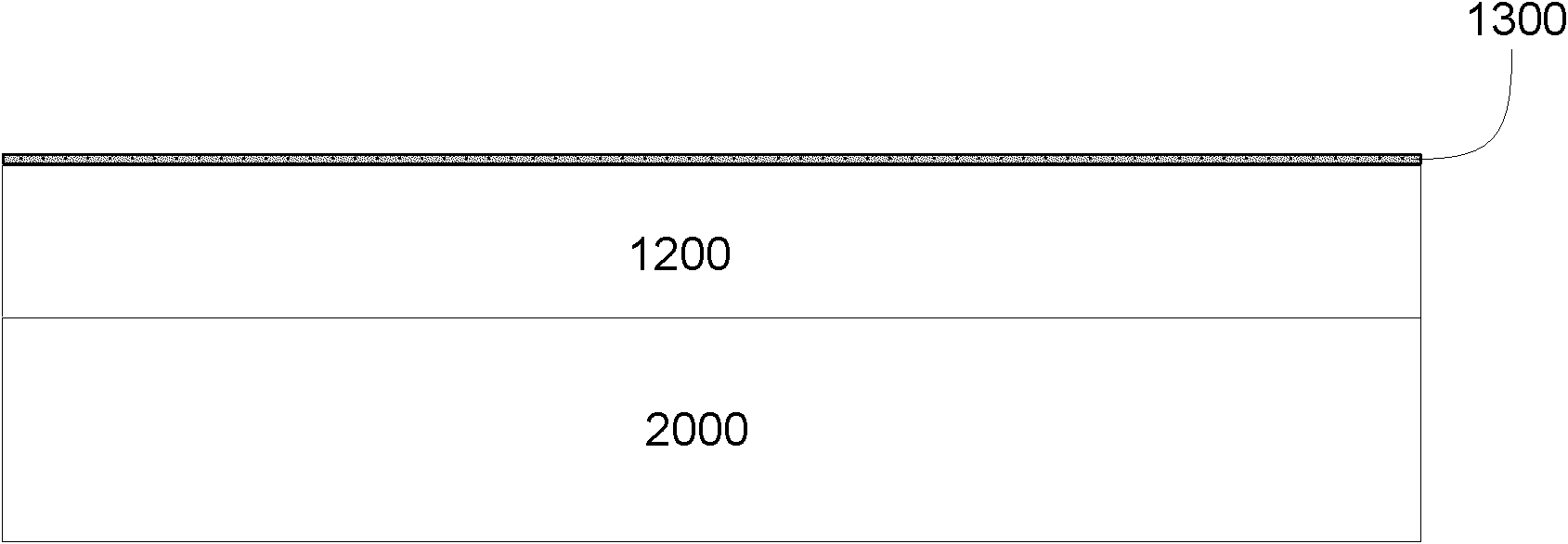

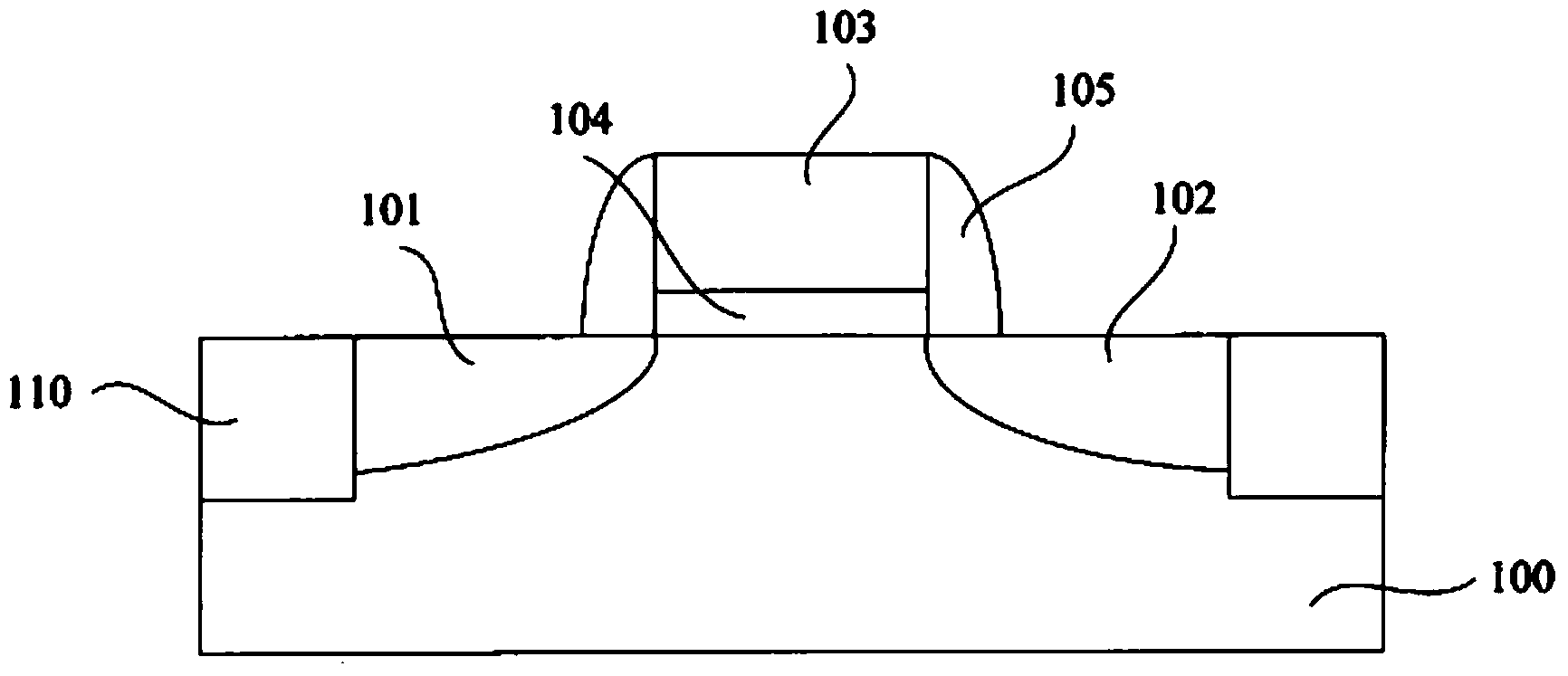

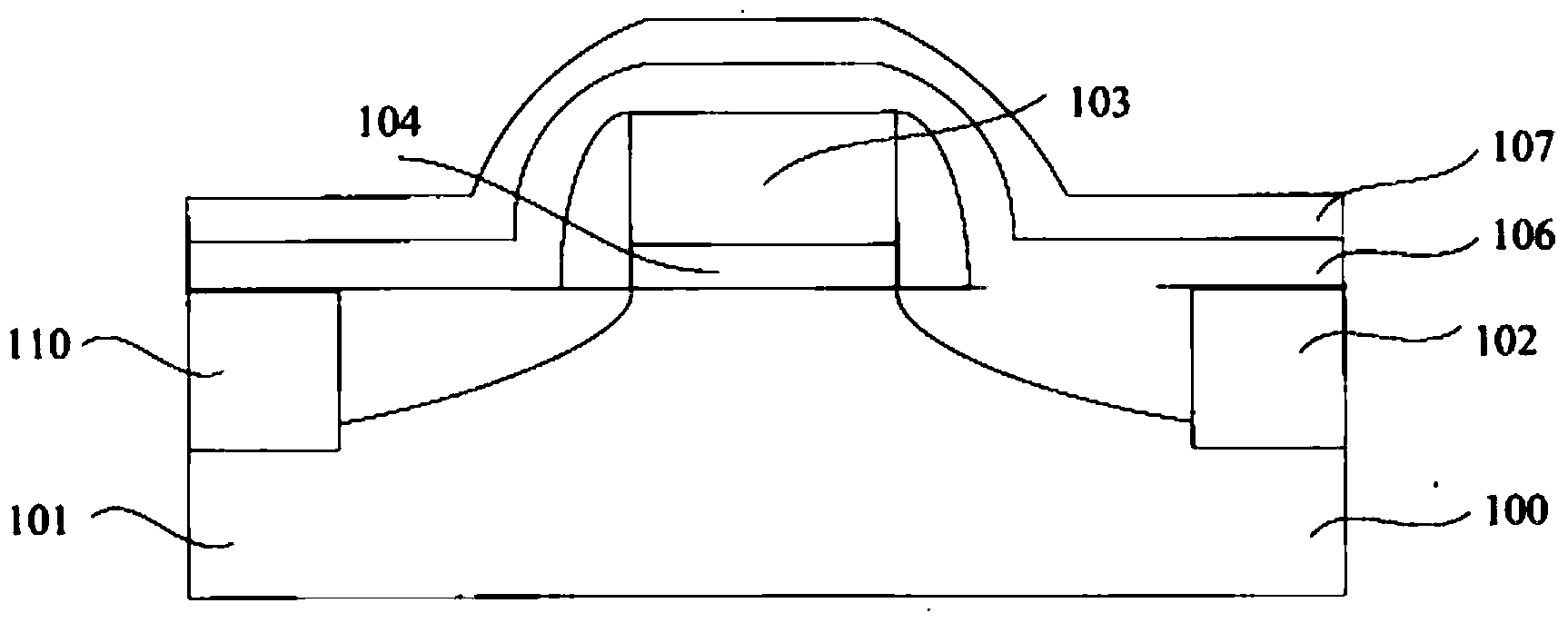

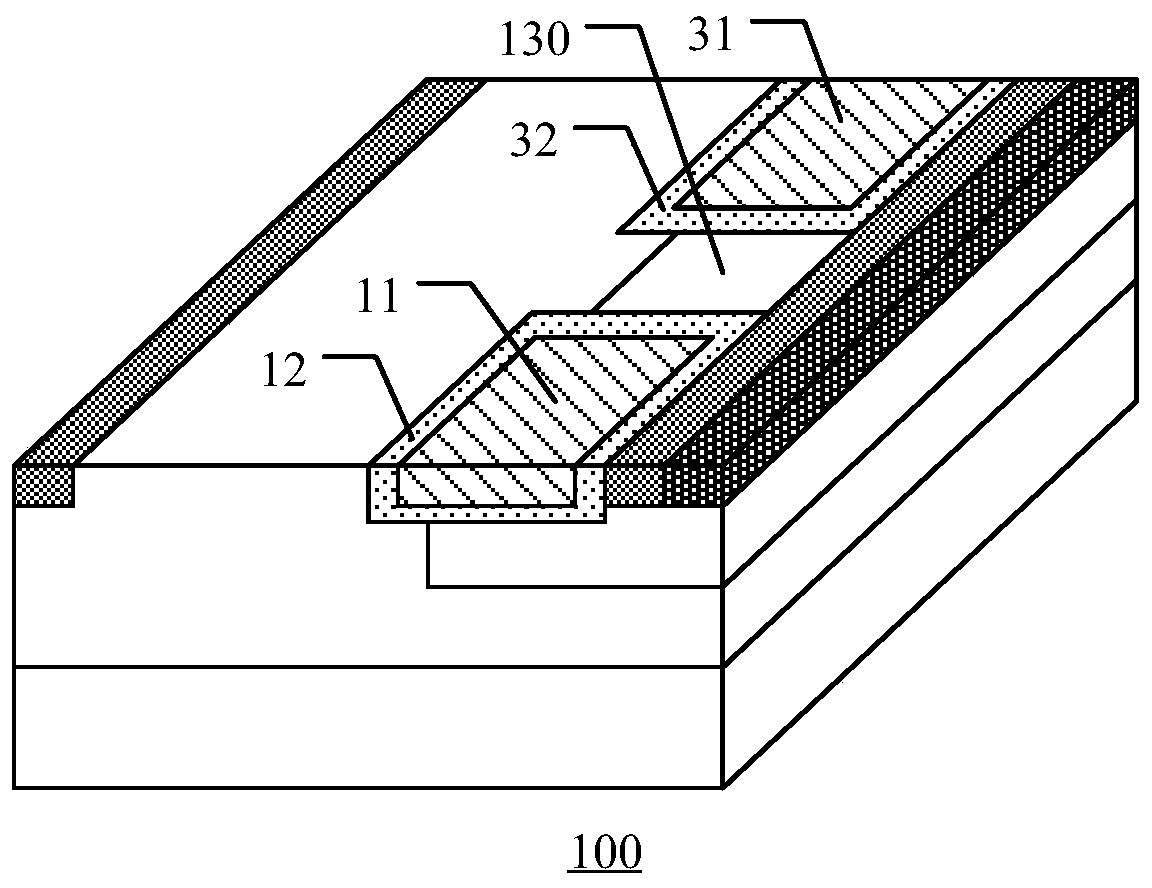

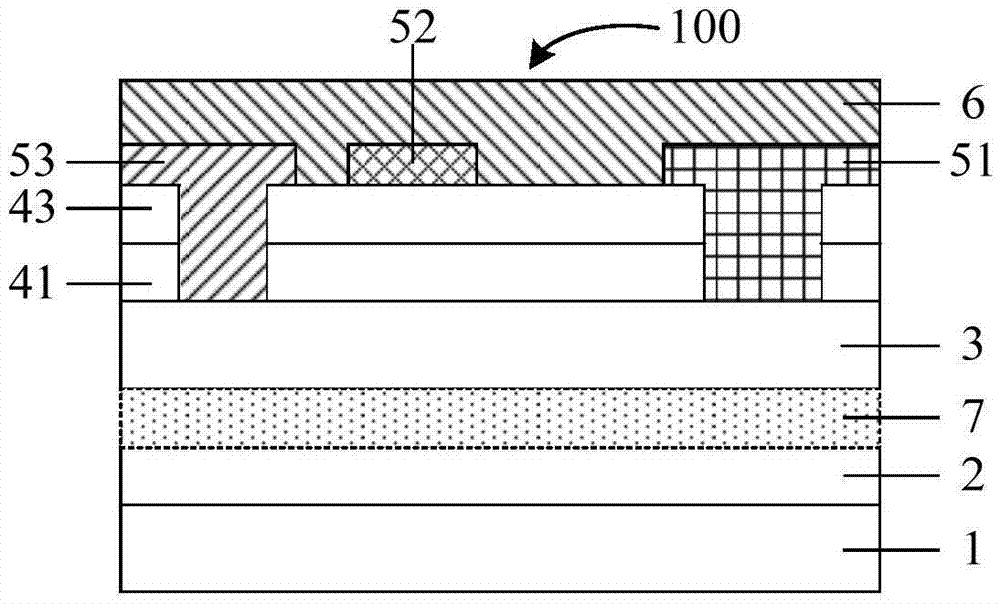

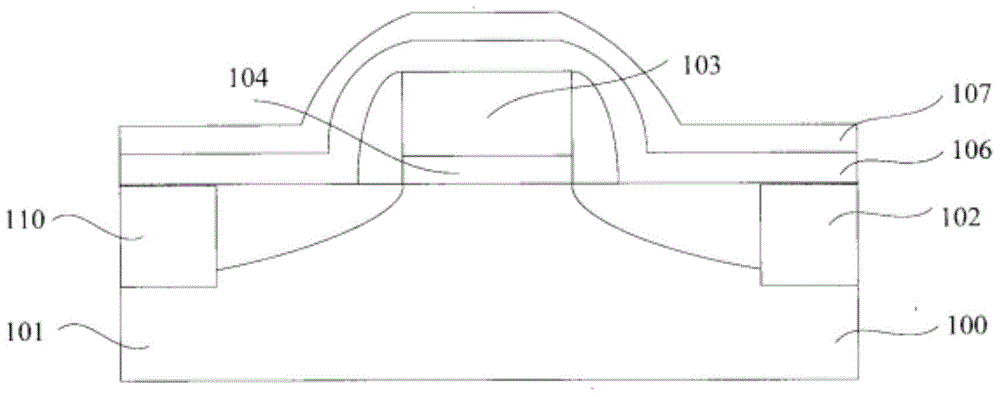

GeOI structure and formation method thereof

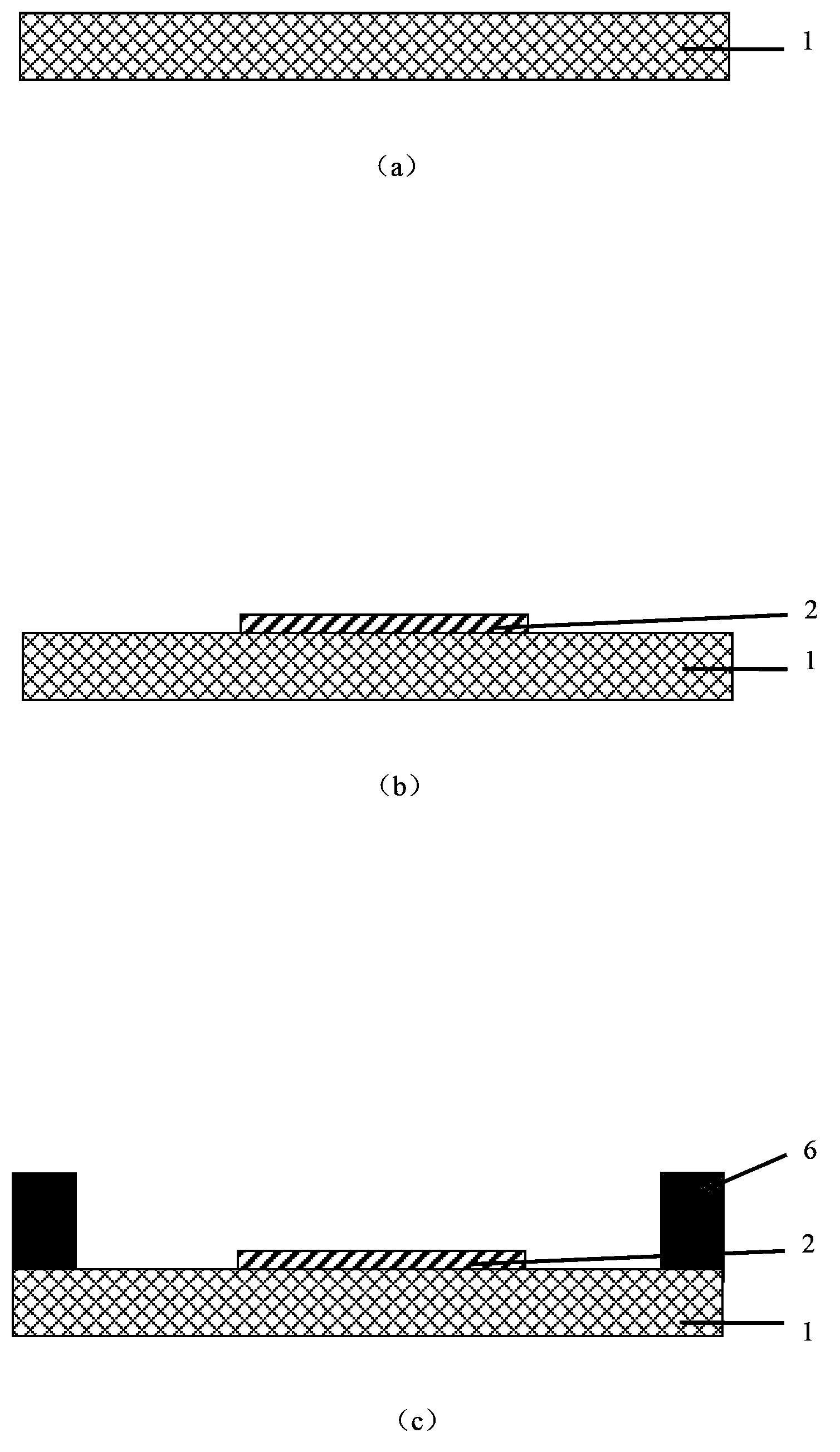

InactiveCN102157432AImprove interface stateReduced mobility performanceSemiconductor/solid-state device manufacturingSemiconductor devicesStrontiumGermanide

The invention provides a formation method of GeOI, which comprises the following steps: forming a Ge-containing layer on a first substrate; adopting strontium (Sr) or barium (Ba) to process a first surface of the Ge-containing layer for forming a first passivated thin layer; overturning the first substrate, the Ge-containing layer and the first passivated thin layer and transferring to a silicon substrate with an oxide insulating layer on the surface; and removing the first substrate. In the embodiment of the invention, the passivated thin layer formed by a strontium germanide or a barium germanide belongs to the field of semiconductors, therefore, the interface state problem between a Ge material and an insulating oxide can be improved, the phenomena of electric leakage and scattering in the position of an interface can be reduced, and the migration performance of the Ge material can not be excessively reduced.

Owner:TSINGHUA UNIV

Method for forming self-alignment metal silicide

InactiveCN104319236AReduce or avoid surface defectsPrevent oxidationSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideMetal silicide

The invention discloses a method for forming a self-alignment metal silicide. The two times of annealing technologies are adopted, hydrogen isotope gas is introduced in the first time of annealing technology, the hydrogen isotope gas is used for reacting with trace oxygen in the atmosphere to eliminate the oxygen, metal layers such as Ni are prevented from being oxidized, and therefore surface defects (such as a pyramid shape) of the metal silicide are reduced or avoided, and the metal silicide with a flat appearance and good uniformity is formed; isotope atoms in the introduced hydrogen isotope gas can enter the interface of the metal silicide and a silicon substrate and are combined with Si to form a new key which can be hardly fractured, and therefore the defects at the interface are overcome and reduced, and the interface state (Dit) is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for manufacturing embedded Si nanocrystalline SONOS device

InactiveCN102683292AImprove reliabilityReduce interface state densitySemiconductor/solid-state device manufacturingSilicon oxideState density

The invention discloses a method for manufacturing an embedded Si (silicon) nanocrystalline SONOS (silicon-oxide-nitride-oxide-silicon) device. The method comprises the following steps: forming a first oxide layer on a substrate in which a grate electrode is formed, and implementing the first annealing process; forming a silicon nitride layer on the first oxide layer, and embedding the Si nanocrystalline in the silicon nitride layer; forming a second oxide layer on the silicon nitride layer and implementing the secondary annealing process; and forming a Si layer on the second oxide layer, and adopting the Si layer as a control grate. According to the method, implements the first annealing process is implemented after the first oxide layer is formed so that the interface state density of the substrate and the interface of the first oxide layer is reduced, the secondary annealing process after forming the second oxide layer is formed on the silicon nitride layer is implemented so that the interface states of the substrate and the first oxide layer are further improved, and the interface between the Si nanocrystalline and the silicon nitride is improved so that the electric charge can retain on the interface between the nanocrystalline and the silicon nitride easily during the compiling and erasing process, so that the reliability of the embedded Si nanocrystalline SONOS device is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

LED epitaxial wafer, method for making the same, and LED chip including the same

ActiveCN103474538BImprove interface stateIncrease roughnessSemiconductor devicesQuantum efficiencyQuantum well

The invention discloses an LED epitaxial wafer, a manufacturing method thereof and an LED chip comprising the same. The epitaxial wafer includes: an undoped GaN layer, an N-type GaN layer, an active layer and a P-type GaN layer which are arranged in order from the surface of the substrate outwards, the active layer includes one or more groups of quantum well layers, each quantum well layer The layers include an InGaN well layer, a GaN barrier layer, and an MgN barrier layer that are sequentially disposed in a direction away from the substrate. The method includes the following steps: forming an undoped GaN layer, an N-type GaN layer, an active layer and a P-type GaN layer in sequence from the surface of the substrate outward, and the step of forming the active layer includes sequentially forming one or more groups of quantum wells The step of forming each quantum well layer includes: forming an InGaN well layer, a GaN barrier layer and an MgN barrier layer in sequence from the surface of the N-type GaN layer outward. The brightness and internal quantum efficiency of the LED obtained by using the manufacturing method of the LED epitaxial wafer provided by the present invention are improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

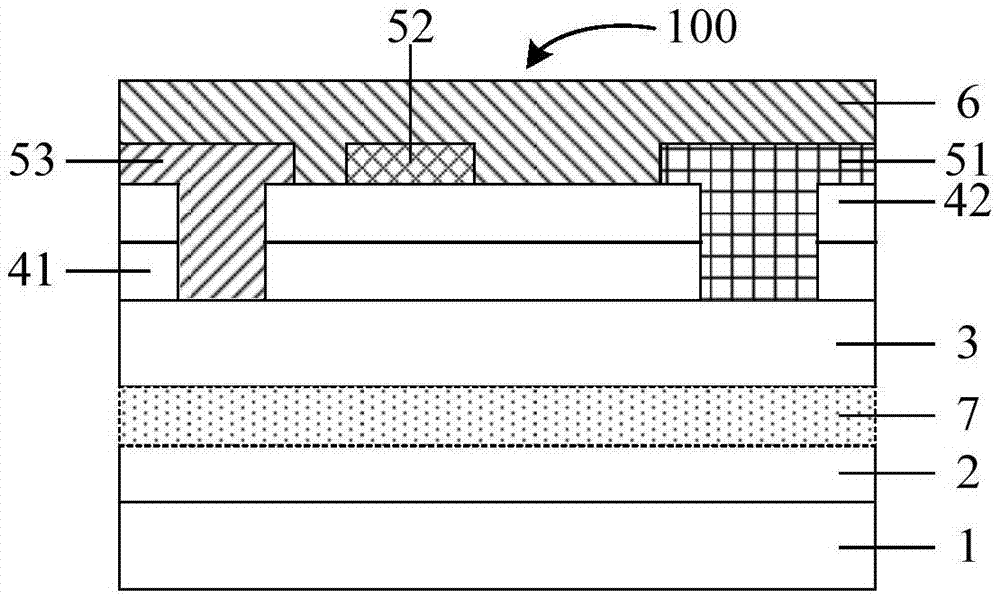

Strain GeOI structure and forming method thereof

ActiveCN102169888AImprove interface stateReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesStrontiumThin layer

The invention provides a strain GeOI structure which comprises a silicon substrate with an oxide insulating layer on a surface; a Ge layer formed on the oxide insulating layer, wherein a first passivation thin layer is formed between the Ge layer and the oxide insulating layer; a gate stack is formed on the Ge layer, and a channel region formed below the gate stack, and drain region and a source region formed at both sides of the channel region; and a SiN strain cap layer for covering the gate stack to enable the channel region to produce strain. The passivation thin layer formed by strontium germanide or barium germanide in the invention embodiment belongs to the semiconductor; an interface state problem between the Ge material and the insulating oxide can be improved through a first passivation layer so as to reduce the electric leakage and scattering at the interface. Furthermore, the SiN strain cap layer enables the channel region to produce strain so as to improve the performance of the appliance.

Owner:TSINGHUA UNIV

Semiconductor device and manufacturing method thereof

PendingCN111584634AExcellent electrical propertiesOptimizing the Uniformity of Vertical Doping ConcentrationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialTrench gate

The invention discloses a semiconductor device and a manufacturing method thereof. The manufacturing method comprises the steps: forming a drift region on a substrate, and etching a well region trench; obtaining a well region in the well region trench through an epitaxial method; and manufacturing a trench gate structure, a source region and a drain region. According to the semiconductor device and the manufacturing method thereof, the well region is manufactured through etching in an epitaxial mode, so that a well region with uniform doping concentration in the longitudinal direction can be obtained, and the semiconductor device with uniform threshold voltage of a trench gate and a plane gate is obtained. The method is mainly characterized in that the well region is manufactured in an epitaxial mode, the uniformity of the longitudinal doping concentration of the well region is mainly optimized to ensure the consistency of the threshold voltage of the trench gate, so that the electrical property of the device is improved. According to the invention, the advantages of the trench gate can be exerted, and the problem of inconsistent threshold voltages of different parts of the trenchgate can be effectively avoided.

Owner:JOULWATT TECH INC LTD

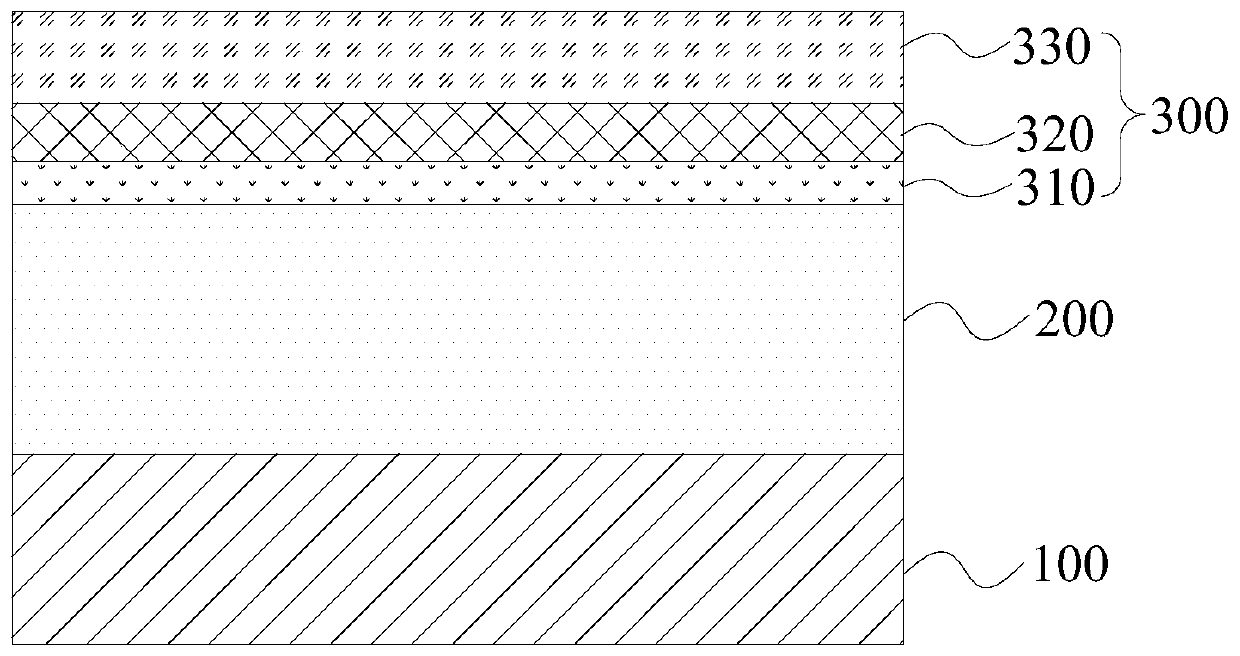

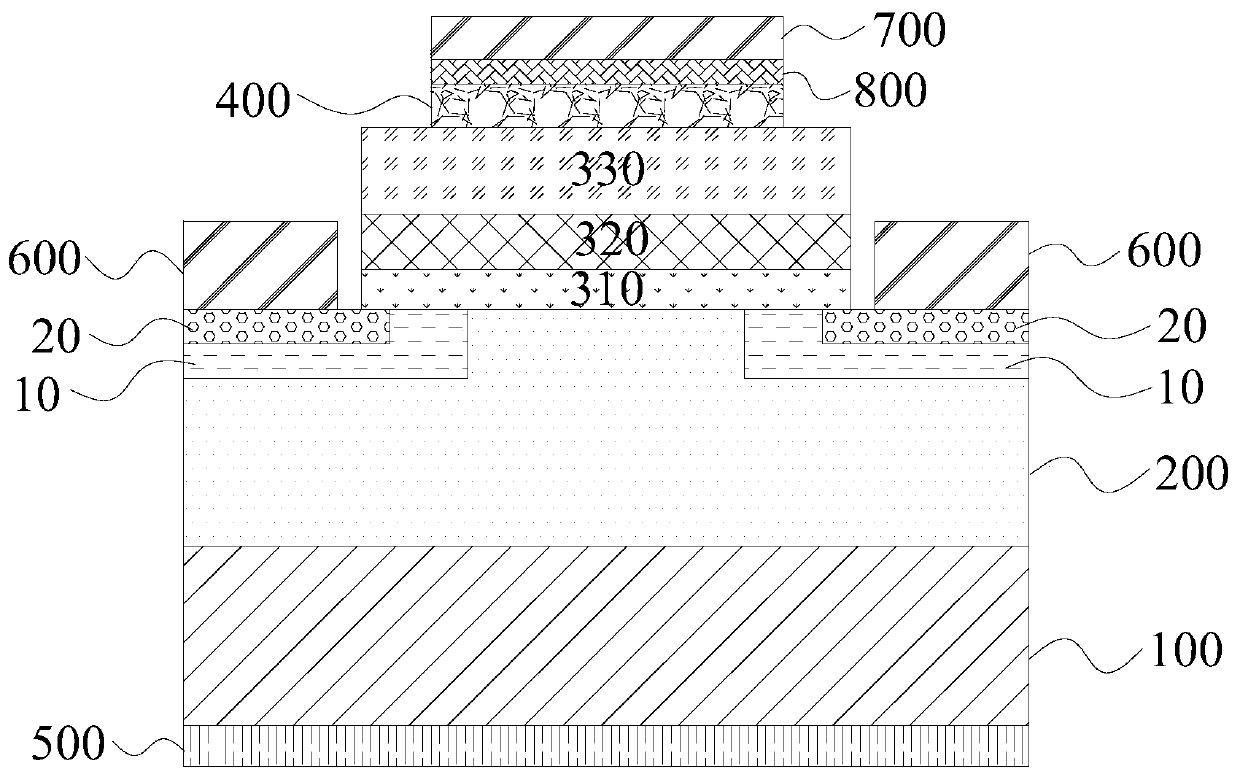

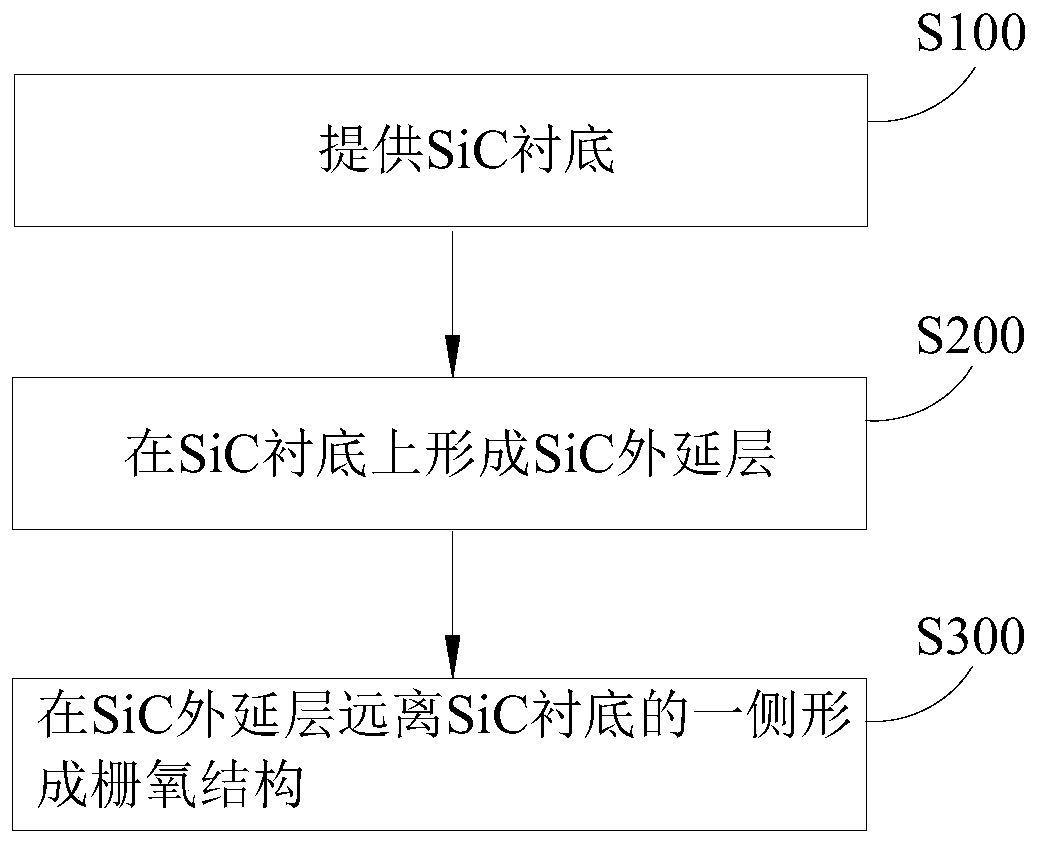

Field effect transistor, preparation method and electronic equipment

PendingCN111326573AImprove interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

The invention discloses a field effect transistor, a preparation method and electronic equipment. The field effect transistor comprises a SiC substrate, a SiC epitaxial layer and a gate oxide structure which are sequentially arranged in a stacked mode, wherein the gate oxide structure comprises a transition layer, a barrier layer and an oxide layer which are sequentially stacked, the transition layer is arranged on the side, which is away from the SiC substrate, of the SiC epitaxial layer, the transition layer and the oxide layer are both made of SiO2, and the thickness of the transition layeris less than that of the oxide layer. Therefore, the interface between the gate oxide structure and the SiC epitaxial layer of the field effect transistor has a good interface state, so that the interface between the gate oxide structure and the SiC epitaxial layer has high mobility, the gate oxide structure has high reliability, and the field effect transistor is enabled to have good use performance.

Owner:BYD SEMICON CO LTD

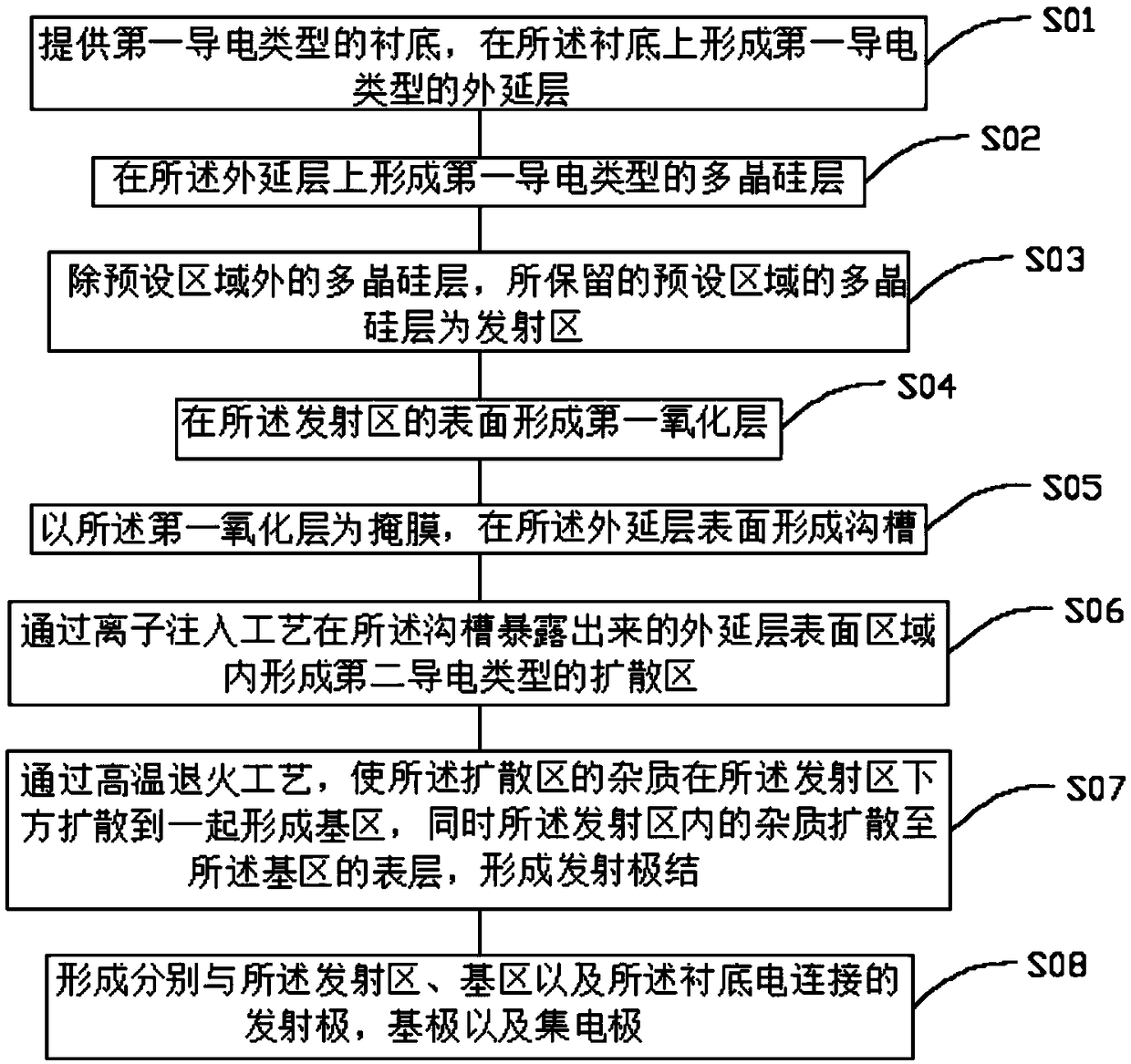

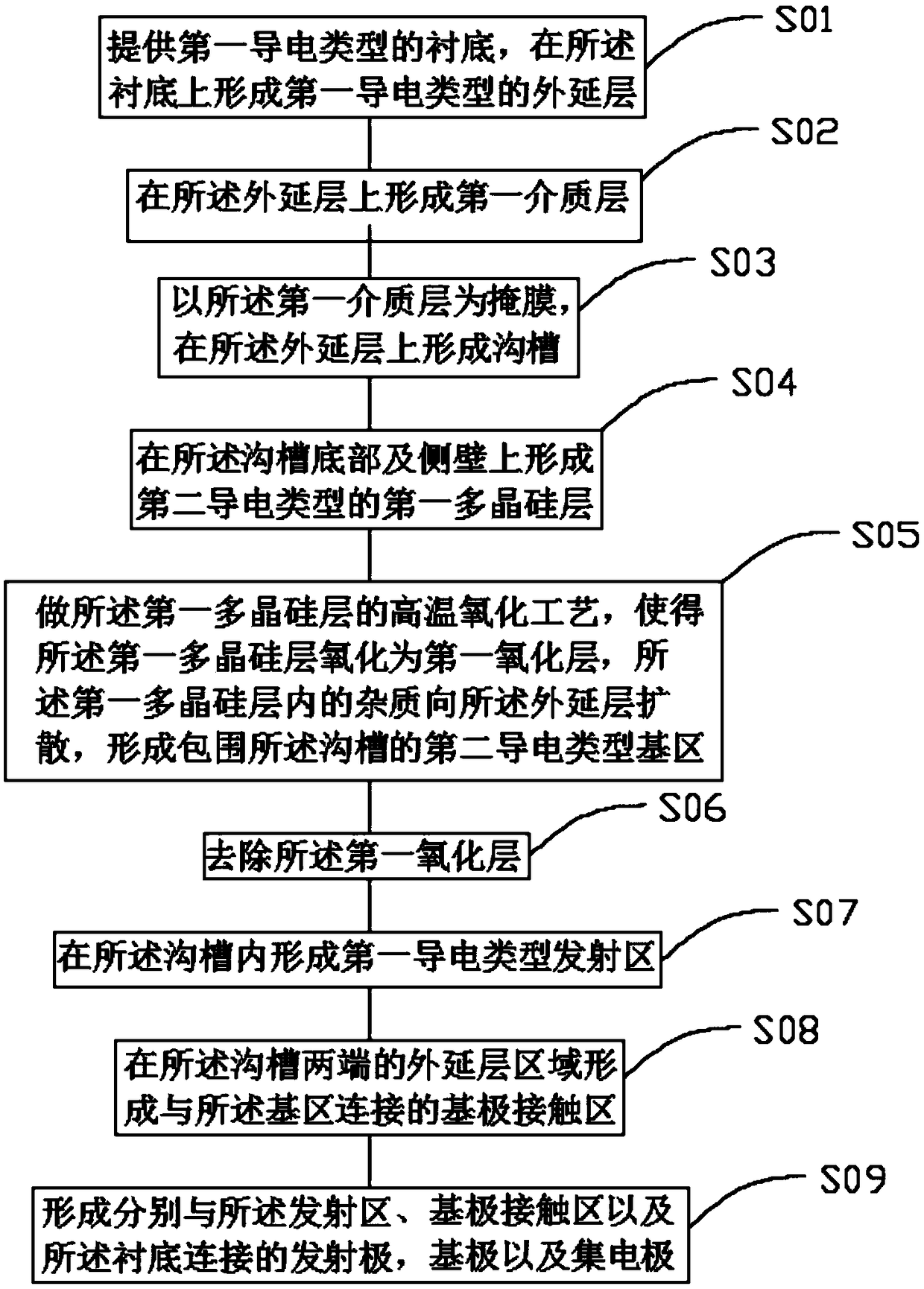

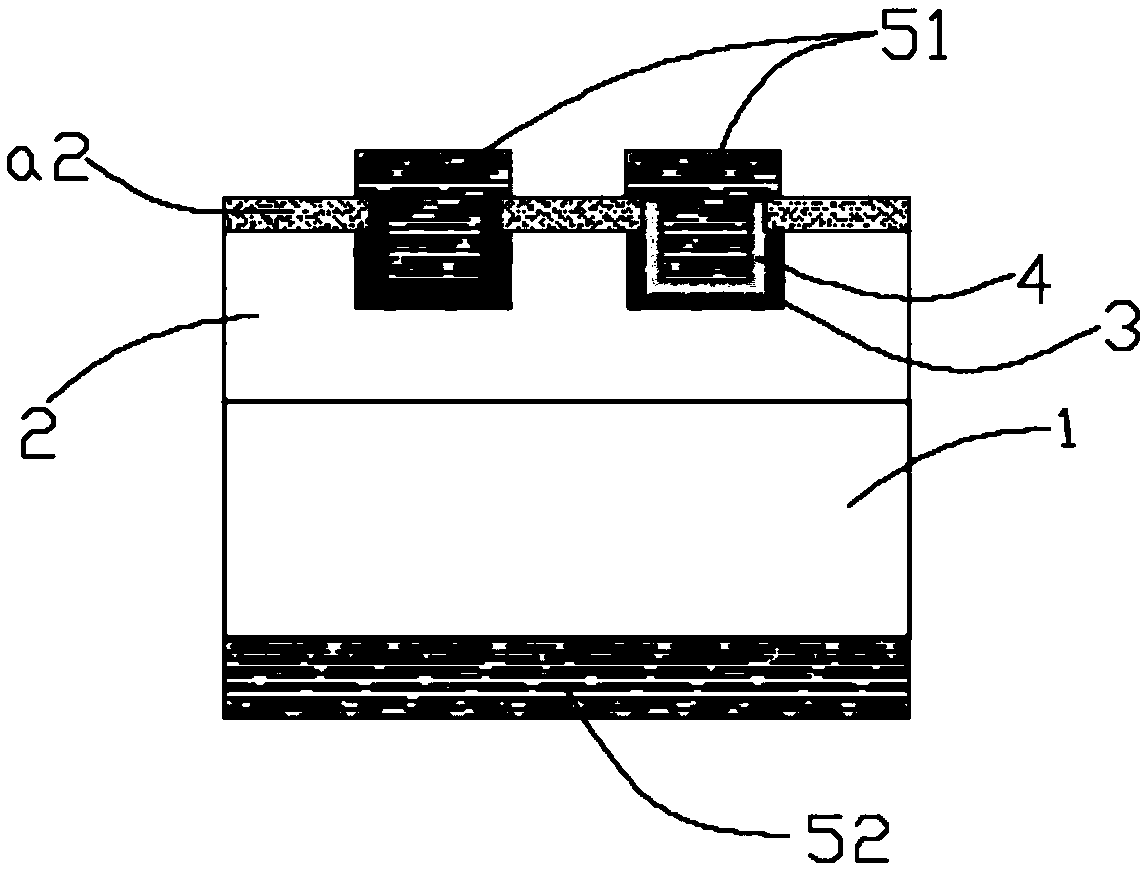

Transistor and manufacturing method thereof

InactiveCN109037061AImprove interface stateStable magnification factorSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerOptoelectronics

The invention relates to a transistor and a manufacturing method thereof. The method comprises the following steps: providing a substrate of a first conductivity type; forming an epitaxial layer of the first conductivity type on the substrate; forming a polysilicon layer of a first conductivity type on the epitaxial layer; removing a polycrystalline silicon layer outside the preset region, whereinthe polycrystalline silicon layer retained in the preset region is an emitter region; forming a first oxide layer on the surface of the emission region; forming a trench on the surface of the epitaxial layer using the first oxide layer as a mask; and forming a diffusion region of a second conductivity type in a surface region of the epitaxial layer exposed by the trench by an ion implantation process. Through a high-temperature annealing process, the impurities in the diffusion region are diffused together under the emitter region to form a base region, and simultaneously, the impurities in the emitter region are diffused to the surface layer of the base region to form an emitter junction; and the transistor formed by the method has a good interface state between the base region and the emitter region, and the amplification coefficient is stable.

Owner:SHENZHEN NANSHUO MINGTAI TECH CO LTD

High-electron-mobility transistor and memory chip

InactiveCN106935641AImprove interface stateReduce reverse leakage currentSemiconductor devicesMemory chipSurface layer

The invention provides a high-electron-mobility transistor and a memory chip. The high-electron-mobility transistor comprises a substrate, a gallium nitride layer, a gallium nitride aluminum layer, a dielectric layer and an electrode, wherein one side of the gallium nitride layer is compounded on a surface layer of the substrate and the other side of the gallium nitride layer is compounded on a bottom portion of the gallium nitride aluminum layer; the dielectric layer is compounded on a top layer of the gallium nitride aluminum layer, and the dielectric layer is provided with at least two cut-through contact holes; the electrode includes a drain electrode, a gate electrode and a source electrode, and the drain electrode and the source electrode are arranged in the corresponding contact holes of the at least two corresponding cut-through contact holes; and the dielectric layer includes a metal oxide layer and / or an inorganic oxide layer, and the inorganic oxide layer includes a first silicon oxide layer. In the technical scheme, an interface state of the high-electron-mobility transistor is improved, a reverse direction leakage current of the transistor is effectively reduced and simultaneously reliability of the transistor is increased.

Owner:PEKING UNIV +2

High-electron-mobility transistor and memory chip

InactiveCN106935640AImprove interface stateReduce reverse leakage currentSemiconductor devicesGallium nitrideMemory chip

The invention provides a high-electron-mobility transistor and a memory chip. The high-electron-mobility transistor comprises a substrate, a gallium nitride layer, a gallium nitride aluminum layer, a dielectric layer and an electrode, wherein one side of the gallium nitride layer is compounded on a surface layer of the substrate and the other side of the gallium nitride layer is compounded on a bottom portion of the gallium nitride aluminum layer; the dielectric layer is compounded on a top layer of the gallium nitride aluminum layer, and the dielectric layer is provided with at least two cut-through contact holes; the electrode includes a drain electrode, a gate electrode and a source electrode, and the drain electrode and the source electrode are arranged in the corresponding contact holes of the at least two corresponding cut-through contact holes; and the dielectric layer includes a metal oxide layer and / or an inorganic oxide layer. In the technical scheme, an interface state of the high-electron-mobility transistor is improved, a reverse direction leakage current of the transistor is effectively reduced and simultaneously reliability of the transistor is increased.

Owner:PEKING UNIV +2

Method for forming self-aligned metal silicide

InactiveCN104362087APrevent oxidationReduce or avoid surface defectsSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideMetal silicide

The invention discloses a method for forming self-aligned metal silicide. The method has the advantages that double-step annealing processes are implemented, isotope gas of hydrogen is introduced in the second annealing process, the isotope gas of the hydrogen and trace oxygen in atmosphere react with each other, accordingly, the oxygen can be eliminated, the metal silicide can be prevented from being oxidized, surface defects (such as pyramid shapes) of the metal silicide can be reduced or prevented, and the metal silicide which has flat morphology and is excellent in uniformity can be formed; isotope atoms in the introduced isotope gas of the hydrogen can enter interfaces of the metal silicide and a silicon substrate and can be combined with Si to form new keys which are difficult to break, accordingly, defects at the interfaces can be repaired and reduced, and interface states (Dit) can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

A kind of preparation method of zinc oxide thin film transistor

ActiveCN108962759BImprove stabilityIncrease the on-state currentTransistorSemiconductor/solid-state device manufacturingRadio frequency magnetron sputteringEvaporation

The invention relates to a method for preparing a zinc oxide thin film transistor, and belongs to a method for preparing a thin film transistor. The method includes substrate cleaning, gate deposition, insulating layer deposition, oxygen-rich zinc oxide channel layer deposition, low-oxygen zinc oxide channel layer deposition, and source electrode and drain electrode deposition. The method has theadvantages that through preparation of the double active layer structure and the interdigital source and drain electrodes, the oxygen-rich and low-oxygen layered channel layers are prepared to improvethe stability of the device and the on-state current, the source and drain electrodes of the interdigitated shape are prepared thereon to further greatly increases the on-state current, and the preparation process is simple. The method is commonly used in the market for RF magnetron sputtering and electron beam evaporation, and does not need to replace the production line; the raw material is pure zinc oxide, the cost is low, and environmental protection is achieved. The method has application prospects in the fields of ultraviolet detection and display driving. The pure zinc oxide thin filmtransistor has more potential application in the market.

Owner:JILIN JIANZHU UNIVERSITY

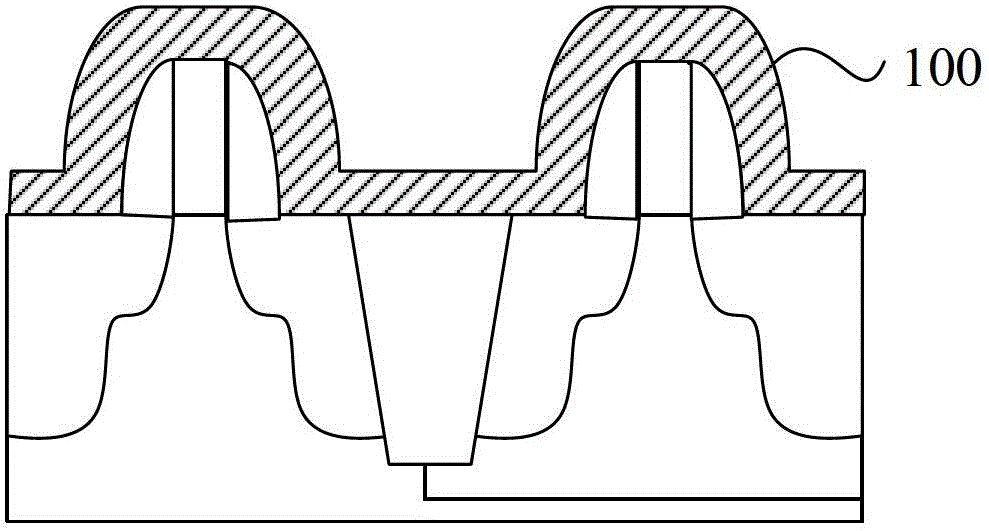

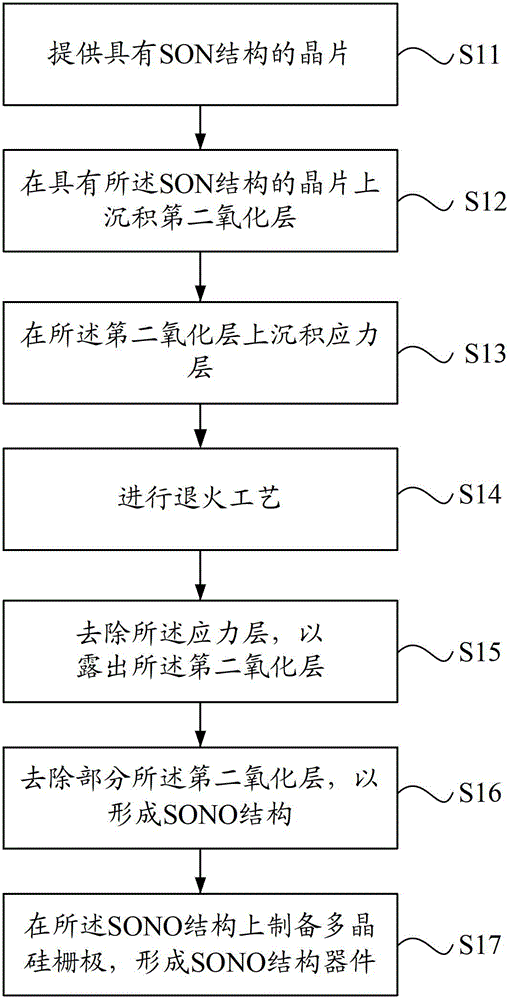

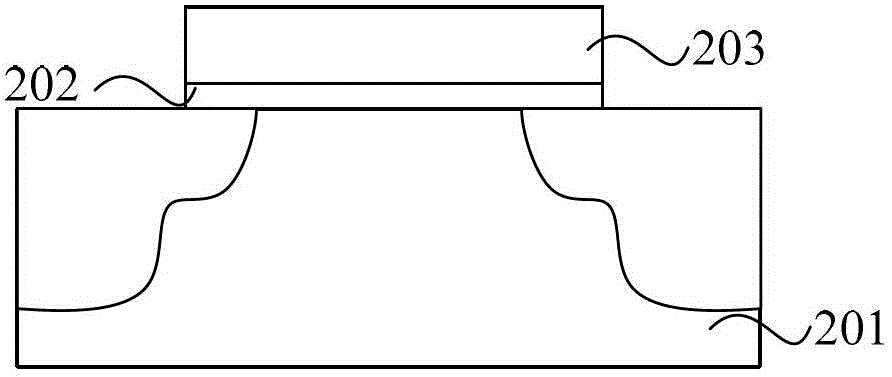

Method for improving compiling speed of silicon-oxide-nitride-oxide-silicon (SONOS) structure device by using stress technology

ActiveCN102683218BImprove mobilityThe effect of stress transfer is obviousSemiconductor/solid-state device manufacturingCharge carrier mobilitySilicon oxide

The invention discloses a method for improving the compiling speed of a silicon-oxide-nitride-oxide-silicon (SONOS) structure device by using a stress technology. The method comprises the following steps of: providing a wafer with an SON structure; depositing a second oxidation layer or a blocking oxidation layer on the wafer with the SON structure; depositing a stress layer on the second oxidation layer or the blocking oxidation layer; and annealing to generate stress on a storage nitration layer, a first oxidation layer and the blocking oxidation layer or the second oxidation layer, conducting the stress to a device channel, and converting the stress into the stress in the channel. The method has the advantages that the stress can be transferred by using the storage nitration layer, the first oxidation layer and the blocking oxidation layer or the second oxidation layer, the stress can approach the channel, and a stress transfer effect is obvious, so the carrier mobility of the SONOS structure device can be remarkably improved, and the compiling speed is improved; and meanwhile, damage to a polycrystalline silicon gate is avoided, and an interface state can be improved by the second oxidation layer or the blocking oxidation layer in the annealing process.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

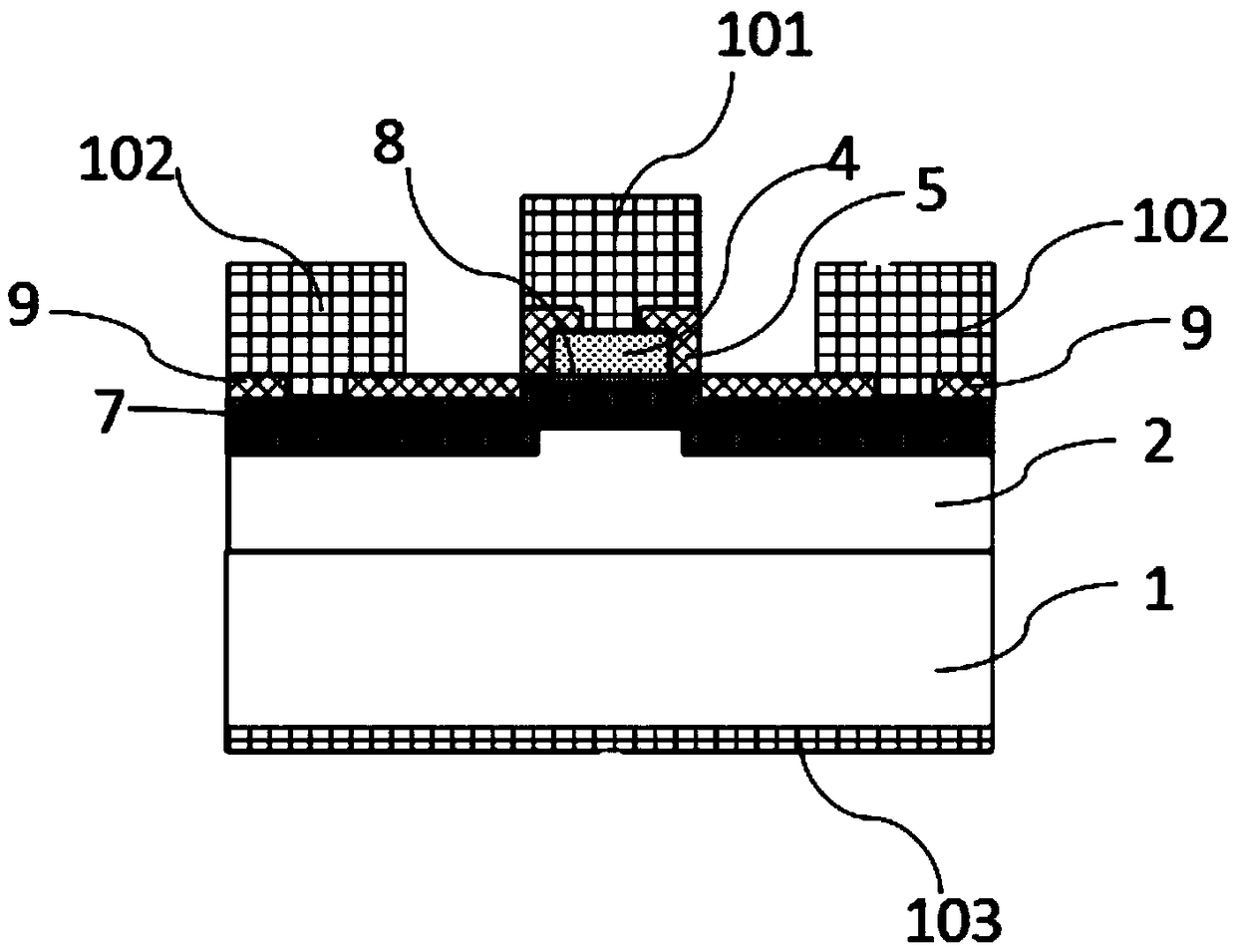

A transistor and a manufacturing method thereof

InactiveCN109103246AAchieve protectionImprove interface stateTransistorSemiconductor/solid-state device manufacturingEngineeringImpurity

The invention relates to a transistor and a manufacturing method thereof. The transistor comprises a substrate of a first conductivity type; an epitaxial layer of a first conductivity type formed on the substrate; a trench formed in the epitaxial layer; an emission region of a first conductivity type formed at the bottom of the trench and the sidewall; a base region of a second conductivity type formed in the epitaxial layer and surrounding the trench; a base contact region formed in the epitaxial layer region to connect the base region. The forming steps of the base region includes forming afirst polysilicon layer of a second conductivity type on the bottom and sidewalls of the trench; performing a high temperature oxidation process of the first polysilicon layer such that the first polysilicon layer is oxidized into a first oxide layer, and impurities in the first polysilicon layer diffuse toward the epitaxial layer to form a second conductivity type base region surrounding the trench. The transistor has a good interface state between the base region and the emission region, and the amplification coefficient is stable.

Owner:深圳市福来过科技有限公司