Transistor and formation method thereof

A transistor and topography technology, applied in the manufacture of transistors, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of large leakage current of transistors, difficult to control transistor formation process, poor reliability, etc., to reduce the gate resistivity, Superior performance and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] It can be seen from the background art that there are problems such as low reliability and large leakage current in the process of forming transistors in the prior art.

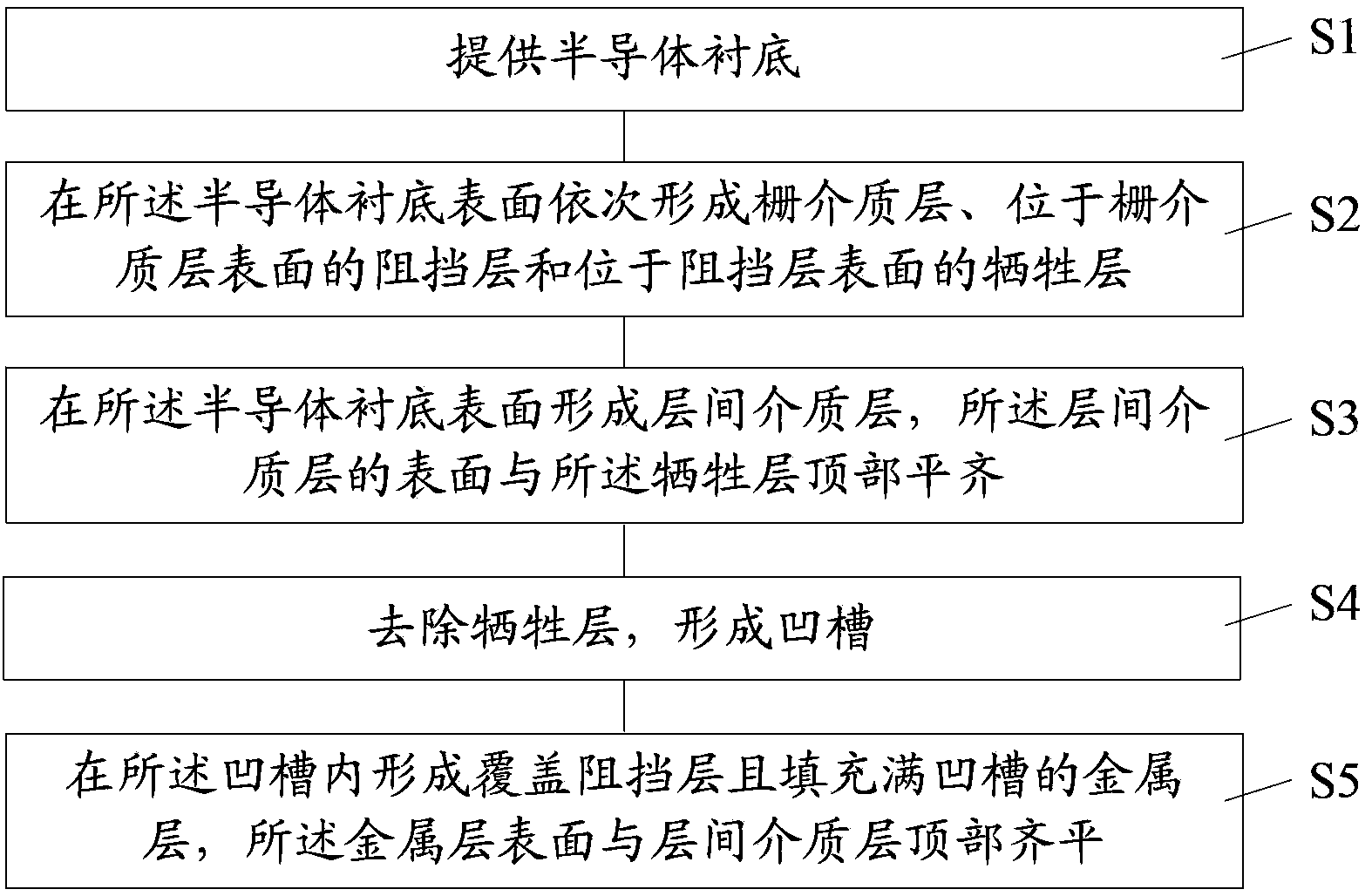

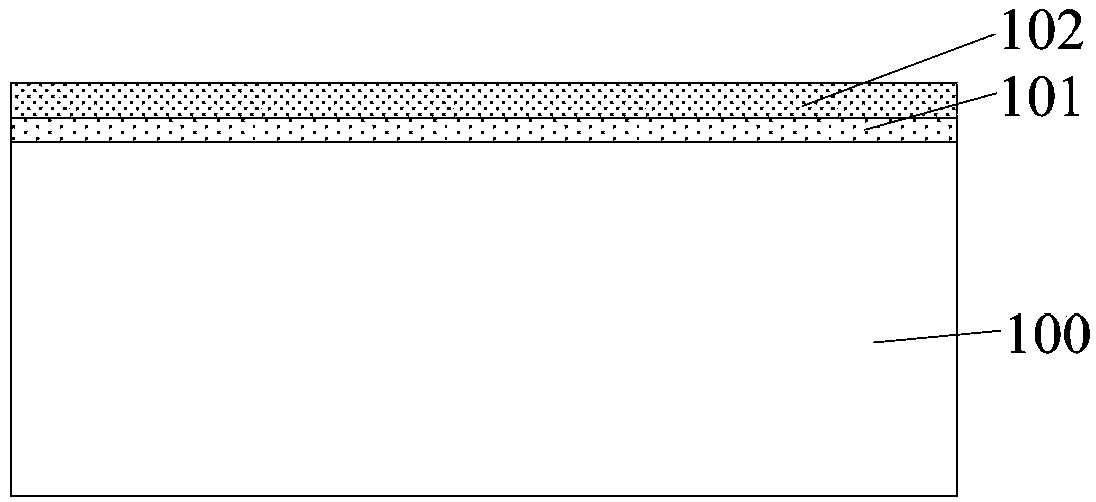

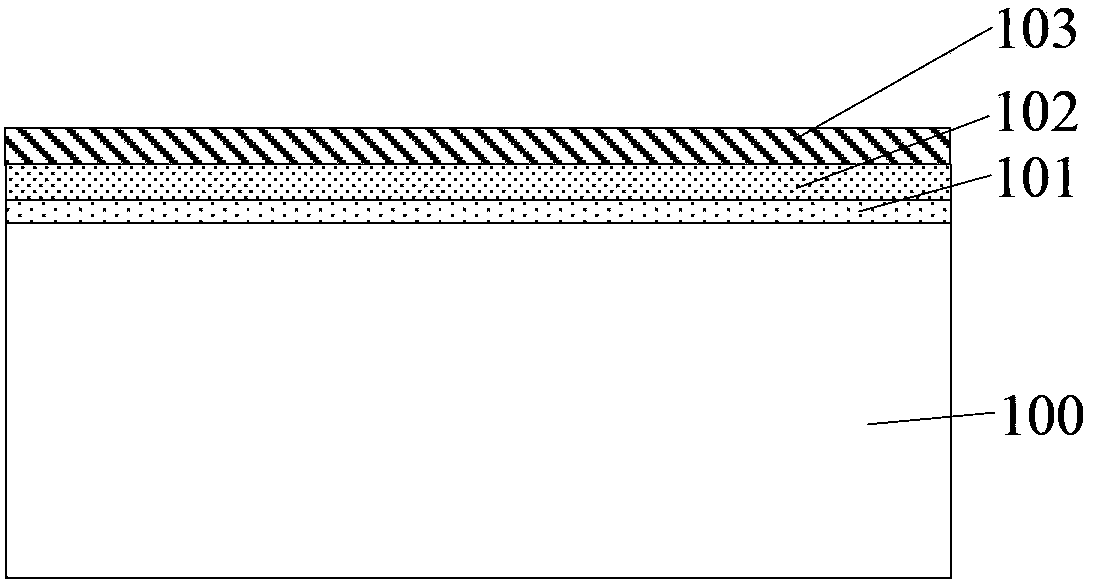

[0034] To this end, the transistor formation process is studied, and it is found that the transistor formation process includes the following steps, please refer to figure 1 : Step S1, providing a semiconductor substrate; Step S2, sequentially forming a gate dielectric layer, a barrier layer on the surface of the gate dielectric layer, and a sacrificial layer on the surface of the barrier layer on the surface of the semiconductor substrate; Step S3, forming a gate dielectric layer on the surface of the semiconductor substrate An interlayer dielectric layer is formed on the bottom surface, and the surface of the interlayer dielectric layer is flush with the top of the sacrificial layer; Step S4, removing the sacrificial layer to form a groove; Step S5, forming a covering barrier layer in the groove and ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More